idelay2中按推荐配置,从DATAIN还是从IDATAIN输入区别为是内部延时还是从IO输入,FIXED固定延时,idelay value先输入0,,时钟是200M,其他全部接0。

2020-11-25 14:35:49 12406

12406 xilinx verilog语法技巧 一 硬件描述语言(HDL)编码技术让您: •描述数字逻辑电路中最常见的功能。 •充分利用Xilinx®器件的架构特性。 1 Flip-Flops

2020-12-13 10:29:00 4344

4344 Xilinx Block Memory Generator(BMG)是一个先进的内存构造器,它使用Xilinx fpga中的嵌入式块RAM资源生成面积和 性能优化的内存。

2023-11-14 17:49:43 4751

4751

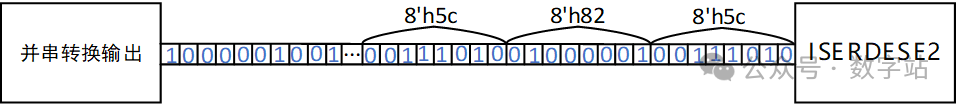

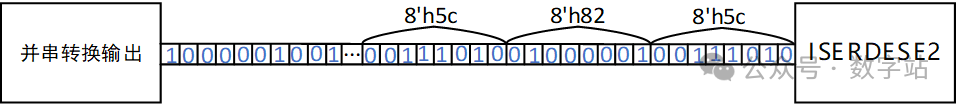

前面在讲解HDMI接口之前,讲解过IDDR、ODDR、OSERDESE2、IBUF等原语,之后一直有读者在问什么时候更新ISERDESE2这个原语。前文讲解过这些原语都在HDMI或者RGMII中使用过,但是ISERDESE2这个原语目前我的板子除了HDMI输入,其余并不会使用到,所以当时就没有出。

2025-03-17 10:52:33 2366

2366

今天用了PLL的IP核,但是提示要用ODDR2才能把输出的时钟信号输出到FPGA的普通IO口上,求大神指导,什么是ODDR2,怎么使用,还有就是怎么在ISE上查看它的接口?

2016-12-14 11:22:23

嗨,我附上了一个非常简单的ISE项目。我有一个2位自由运行计数器(cnt)指望clk的上升沿。 cnt输出定向到两个ODDR2实例的D0输入。 ODDR2的D1输入设置为“0”,C0设置为clk

2019-07-08 07:02:01

嗨,我复制在顶级模块中粘贴下面的ODDR代码,但它显示了一些错误。我可以知道我还应该做些什么吗?谢谢最好的祝福

2020-05-07 08:45:00

Xilinx Artix7 DEVB_124X92MM 6~16V

2023-03-28 13:05:55

`Xilinx FPGA入门连载40:SRAM读写测试之设计概述特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1jGjAhEm 1 功能简介如图所示,本

2015-12-18 12:57:01

Xilinx FPGA入门连载43:FPGA片内ROM实例之功能概述特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1jGjAhEm 1 功能概述该工程

2016-01-06 12:22:53

Xilinx FPGA入门连载47:FPGA片内RAM实例之功能概述特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1jGjAhEm 1 功能概述该工程

2016-01-20 12:28:28

Xilinx FPGA入门连载51:FPGA片内FIFO实例之功能概述特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1jGjAhEm 1 功能概述该工程

2016-02-26 10:26:05

指南 -- Modelsim仿真验证Lesson13 特权Xilinx FPGA SF-SP6入门指南 -- PWM蜂鸣器驱动之功能概述Lesson14 特权Xilinx FPGA SF-SP6入门指南

2015-07-22 11:49:20

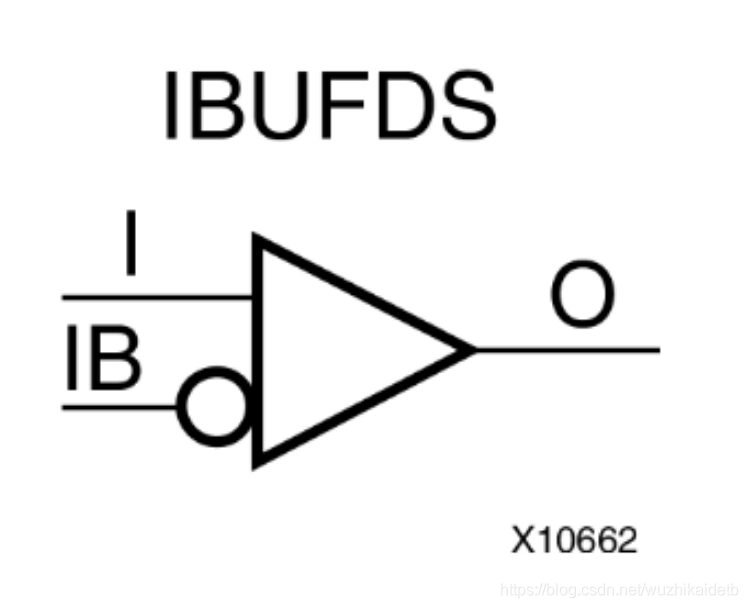

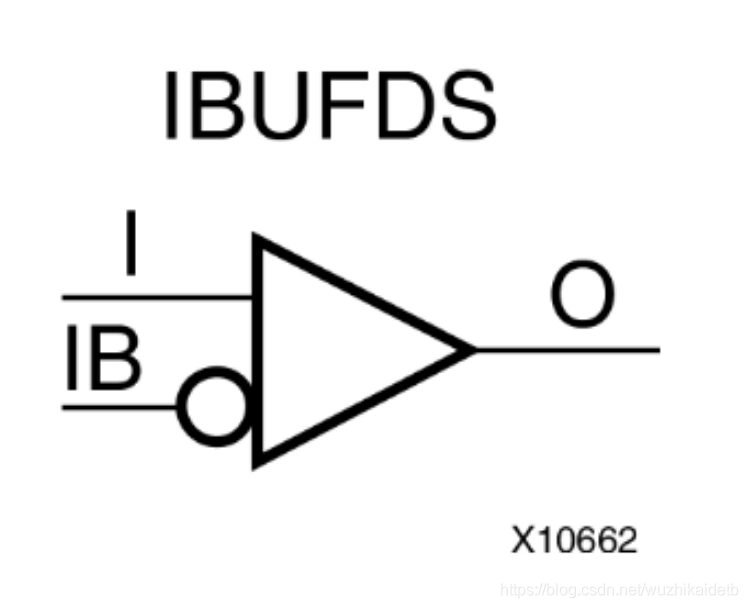

。 2实现 Xilinx 7系列的差分信号的实现主要通过IBUFDS、OBUFDS、IOBUFDS等原语的调用,在程序中直接进行原语的例化,以IBUFDS和OBUFDS为例: 2.1IBUFDS

2020-12-23 17:17:47

Xilinx原语使用方法

2021-02-22 06:55:53

个MUX。利用这种2+1的组合可以产生DDR操作,Xilinx称之为ODDR2。每个存储单元都有6个接口信号:时钟+时钟时能,数据输入+输出,置位复位+翻转输入除了这些信号,存储单元还有一些属性设置

2012-08-02 22:48:10

我看到别人写的项目 程序中用了很多原语,比如输入时钟要设置一个IBUFG,有一些输出信号接一个OBUFG,那么原语的好处是什么?如何知道什么时候要使用原语!

2017-07-13 19:59:37

器件结构及描述3.1 概述3.2 Spartan-ⅡE系列FPGA3.3 Spartan-3系列FPGA3.4 本章小结第4章 ISE 6.x设计工具简介和使用4.1 概述4.2 Xilinx设计流程

2012-02-27 14:43:30

Xilinx工具:vivado在该图中,TX_CLK_i连接到pll_x1模块的输入时钟。然后,pll_x1的输出时钟连接到ODDR。接下来,ODDR的输出引脚将连接到I / O引脚

2020-05-04 08:04:41

找到任何关于算法类型和基元类型的约束。如果有,我将使用更少的BRAM资源。Xilinx是否具有用于推断RAM的算法类型和原语类型?我使用的是Vivado 2014.4和Kintex-7设备。 谢谢大家。

2020-03-31 07:45:01

`[tr=transparent]BUFMUX原语是2输入1选择1输出,现在我想改成2位位宽的s选择信号,达到一个四输入的BUFMUX,请问有什么办法可以实现,如果级联?图片最下面这个控制信号是2位的[/tr]`

2018-03-23 15:18:46

`BUFMUX原语是2输入1选择1输出,现在我想改成2位位宽的s选择信号,达到一个四输入的BUFMUX,请问有什么办法可以实现,如果级联?图片最下面这个控制信号是2位的`

2018-03-23 15:12:31

xilinx中的carry4原语在高云FPGA中用什么原语替代

2024-05-09 16:13:02

使用xilinx spartan6,在工程中使用原语生成DDR控制器mig文件,DDR数据管脚定义发生改变,需要重新分配管脚,求告知,这个管脚分配要怎么弄

2016-07-19 09:54:37

今天给大侠带来 Xilinx ISE14.7 LVDS应用,话不多说,上货。

最近项目需要用到差分信号传输,于是看了一下FPGA上差分信号的使用。Xilinx FPGA中,主要通过原语实现差分信

2024-06-13 16:28:52

用于xilinx ML507的Xilinx顶点XC5VFX70TFFG1136 FPGA如何将xilinx LUT作为移位寄存器?什么是xilinx ML507的Xilinx顶点XC5VFX70TFFG1136 FPGA的CLB结构。这个FPGA上有哪些额外的原语?

2020-06-16 16:48:59

Gowin FPGA原语使用指南

2022-09-30 06:59:55

IDDR与ODDR的简述RGMII时序简述千兆网输入与输出模块的设计测试模块的设计仿真测试结果总结

2021-01-22 06:09:37

SelectIO接口使用IDDR原语执行4x异步过采样。时钟由MMCM或PLL原语生成,并通过BUFG时钟网络路由,并可使用器件内任何选定的输入对单端或差分信号进行操作。XAPP523是由MMCM

2020-08-11 10:59:59

我正在使用ODDR2生成外部时钟(ISE = 13.1,Planahead = 13.1):clk5m_inst:ODDR2通用映射(DDR_ALIGNMENT =>“NONE”, - 将输出

2019-06-17 14:43:06

ADAPTER TC2050 FOR XILINX CABLE

2023-03-22 19:59:52

如图,在书上看到的一个小例程,然后用quartusii V14.1对其进行综合,显示Verilog不能合成MOS开关门原语。这段代码是在康华光的第五版的数电上看到的啊,为什么不能综合?

2017-06-03 15:54:37

程序里,tx_data_oddr_s[l_inst]经OBUFDS输出两个正交的量,一路作为I(tx_data_out_p),一路作为Q(tx_data_out_n)进入AD9361输入引脚。应该是

2016-01-15 17:51:39

://www.xilinx.com/support/answers/35032.htm解决方案是使用ODDR2实例化(时钟转发技术),其中时钟信号不直接驱动负载引脚,而是充当ODDR2的输入,然后ODDR2的输出

2018-10-17 14:28:54

时钟编译报错,好好的东西在QUARTUS里面也没有报错啊,经过各种分析发现,XILINX的时钟处理很麻烦,时钟不能直接输出到IO,需要加ODDR,然后才能接到IO中,这个ODDR我是添加了,但是一直

2017-08-17 23:37:42

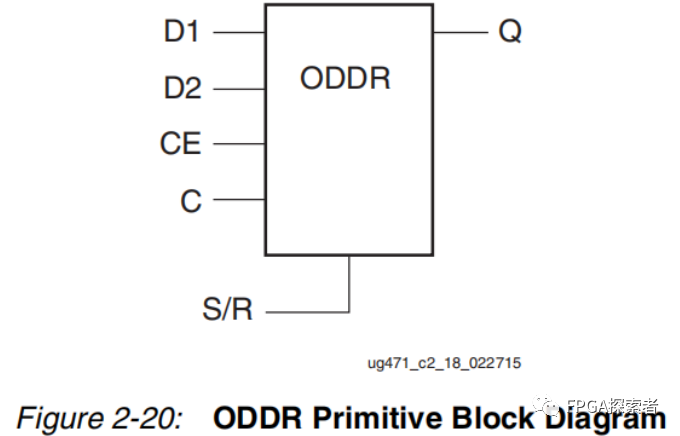

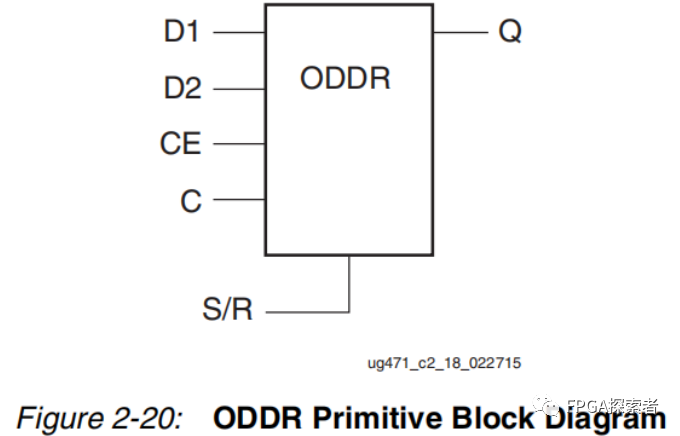

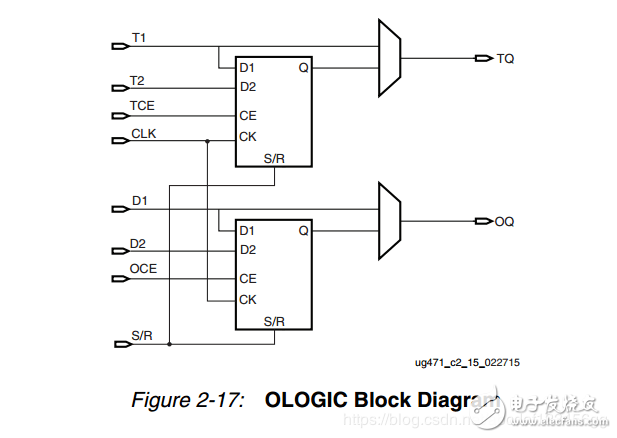

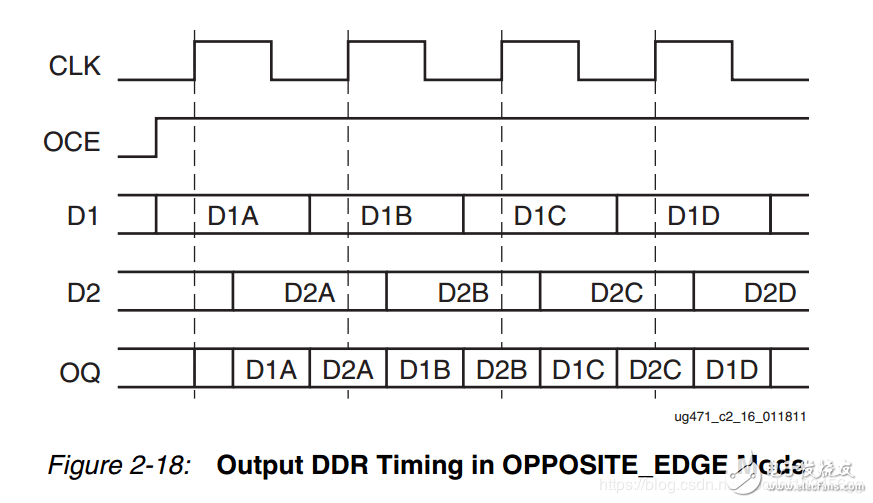

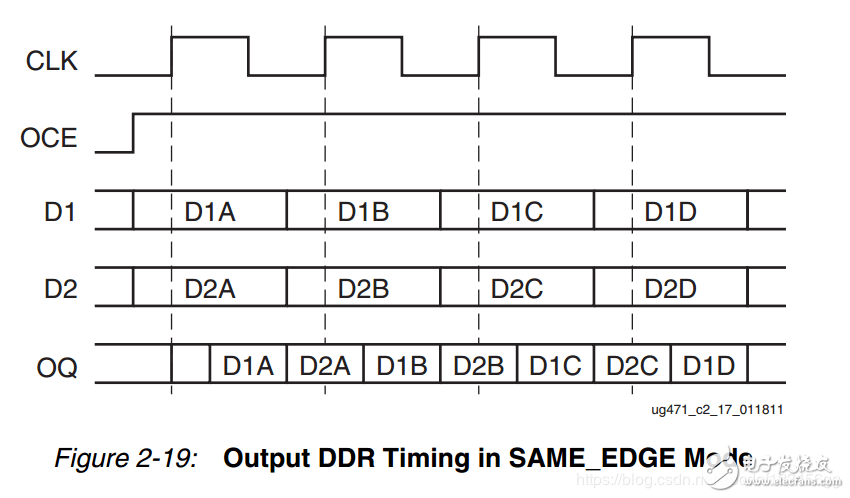

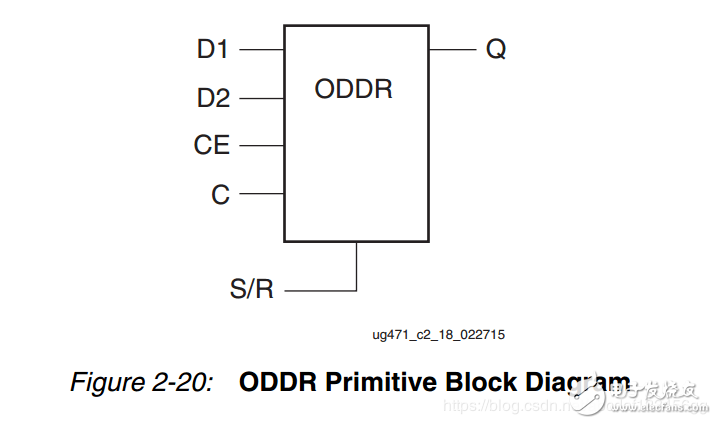

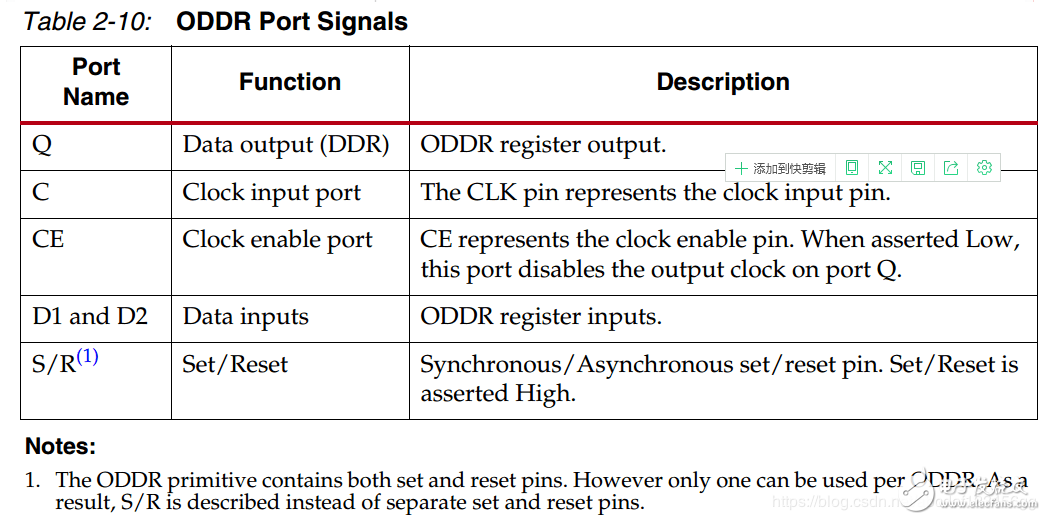

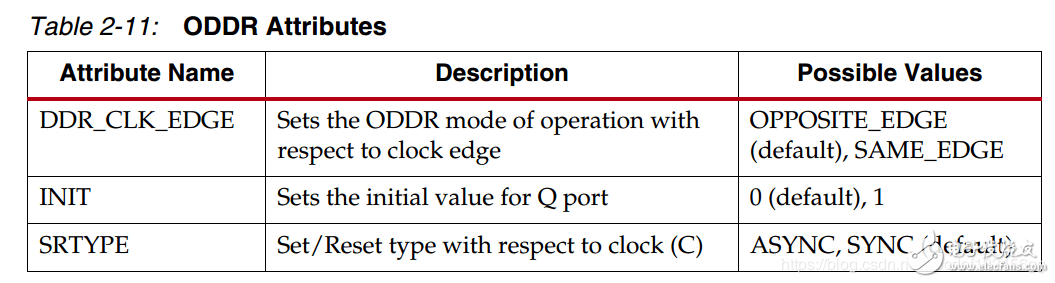

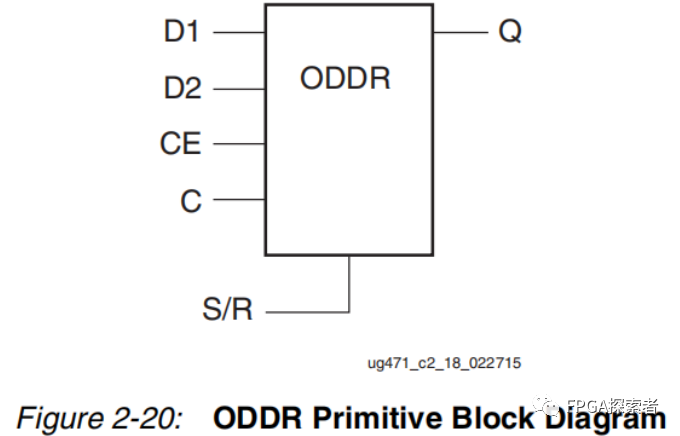

。 IDDR与ODDR的简述 这里的表述,我们主要依靠技术手册来给大家进行讲解。 简单的框图显示如下: 其中IDDR的原语如下: IDDR #( .DDR_CLK_EDGE

2021-01-15 16:41:12

你好我将virtex5 LX50与具有应根据standardEIA / TIA-644 LVDS规范终止的输出数据的设备连接起来我在用着IBUFDS用于将输入LVDS转换为LVTTL,OBUFDS用于输出信号和时钟这是这样做的正确方法为此目的使用ODDR原语的重要性是什么?问候uzmeed

2020-06-17 14:59:44

问候,两个与ODDR相关的问题:1)如果我想将由同一个BUFG驱动的同一时钟转发到多个外部设备,我是否必须实例化几个ODDR?或者,如果我只是实例化一个ODDR并将输出驱动到指向外部设备的多个

2018-11-02 11:28:55

嗨,在post place and route genererated .vhd文件中有一个组件实例化X_FF。我已经搜索到了描述X_FF的等效xilinx原语(触发器),但发现了很多。我想xilinx原始X_FF描述IN VIRTEX 7 BO ??谢谢Manasa Thoonoli

2020-04-06 17:34:42

嗨,我正在使用Planahead 14.6 - 来自Xilinx的人可以在OVERSAMPLE模式下确认Kintex-7中ISERDES原语的实际位顺序输出是什么吗?我问的原因是,由于大多数这种

2020-08-14 08:00:57

IamusingtheSpartan7inmydesign。我发现我可以直接将MMCM的输出连接到FPGA端口。我想知道在不使用ODDR的情况下转发时钟有什么意义吗?

2020-08-25 15:55:37

亲爱的大家,Virtex中的许多原语在Spartan 6中找不到,例如BUFIO,BUFR,IDELAY,IDDR。如何使用Spartan原语实现类似的功能?非常感谢你!箱子以上来自于谷歌翻译以下

2019-06-03 10:31:21

嗨,我正在使用斯巴达-6和12.3 ISE。我必须从FPGA输出60 MHz到ADC的时钟。对于这个部分,我从时钟发生器IP内核获得60 MHz并将其馈送到ODDR2的一个输入,并将反相时钟馈送

2019-07-30 09:47:00

我有一个从Core Generator生成的模块,它使用来自100Mhz输入时钟的PLL_base原语生成时钟。现在由于一些错误,我不得不在原语的输出中添加一个非门和一个ODDR2,我通过编辑由核心

2019-05-31 06:56:29

你好,我最近正在进行FPGA测试工作,我碰巧使用xilinx文档中描述的回读捕获UG191.i可以使用回读验证功能回读配置存储器数据,但我无法使用CAPTURE_VIRTEX5原语读回FF

2020-06-11 08:37:48

你好!我想在Kintex 7(XC7K410T)设计中实现PLLE2_BASE原语,但实例化原语时不会突出显示。此外,我收到不支持CLKFBOUT_MULT属性的警告。谁能告诉我我做错了什么?这是

2020-07-18 18:21:08

大家好,我无法找到IODRP2_MCB原语的任何文档。Xilinx文档中唯一提到它的地方是用于HDL设计的Spartan-6库指南(UG615-v12.1,第138页),其中包含指向其他文档的链接

2019-05-24 13:06:19

有什么方法可以使用SEM和CAPTURE原语吗?我是否激活了CAPTURE,SEM可以重新计算ECC的帧数变化了吗?或将永远失去?谢谢中号

2020-06-16 16:41:14

嗨!我想知道BUFIO2 + BUFG和ODDR2的解决方案是否用于时钟路由在时钟源上可以避免使用Spartan 6(使用直接赋值)已经从外部缓冲了。我的意思是,而不是 bufio2_axi_clk

2018-10-23 10:24:05

嗨, 我想得到一些关于k7原语的详细信息(更具体的oserdes和iserdes)。我发现了一个关于v6 hdl原语的UG。 k7有类似的UG吗?我没找到它。谢谢。

2020-08-24 09:48:20

美好的一天,我对IOB中的ODDR2触发器有疑问。现在我实例化以下内容:ODDR2_1:ODDR2通用映射(DDR_ALIGNMENT =>“NONE”, - 将输出对齐设置为“NONE

2019-07-23 10:24:11

我正在调试Xilinx Zynq + ADS58C48,ADC使用的是LVDS模式,ADC不能正常工作。有以下几点问题:

1)通过Xilinx FPGA差分原语输给ADC一个10MHz的差分时

2024-12-10 07:34:45

大家好,我是使用Xilinx ISE和编程FPGA的新手。我开发了一个程序来模拟DDR SDRAM用于测量目的。我使用了许多原语,如Blockram(IP CORE gen工具),DCM,ODDR

2019-05-08 13:07:02

器件定义

软件工具概述

选择配置模式

编程/配置选项

XILINX的通用配置/编程的装置

2010-06-22 16:24:01 78

78 本书系统地论述了Xilinx FPGA开发方法、开发工具、实际案例及开发技巧,内容涵盖Xilinx器件概述、Verilog HDL开发基础与进阶、Xilinx FPGA电路原理与系统设计

2012-07-31 16:20:42 12480

12480

Xilinx FPGA工程例子源码:PCI Express标准概述白皮书

2016-06-07 14:13:43 14

14 xilinx原语的使用,建议有一定经验的参考。

2016-12-17 11:58:56 14

14 当ISE调用ModelSim进行仿真的时候,如果在FPGA设计中使用了Xilinx提供的的IP core或者其他的原语语句,ModelSim不添加Xilinx相应的库文件的话,是无法仿真的。

2017-02-11 15:22:37 1766

1766

IBUFGDS输入全局时钟及DCM分频使用

2017-02-11 16:16:11 5368

5368 xilinx 原语使用方法

2017-10-17 08:57:42 11

11 xilinx原语使用方法

2017-10-19 08:50:39 15

15 基于SRL16的分布式RAM不再支持V5、S6和V6等器件,但是SRL16是所有XIlinx器件都支持的,并且在设计中应用非常频繁,因此可通过调用原语的方法来调用SRL16E甚至SRL32E来实现原来ISE分布式RAM IP核的设计。

2018-05-05 10:38:00 7848

7848 了解如何使用Xilinx SDK调试u-boot代码。

概述了技术以获得重定位偏移量,以便可以在SDK中应用它。

2018-11-27 06:36:00 4823

4823 了解Xilinx SDK如何为您提供在Zynq全可编程器件上创建,开发,调试和部署嵌入式软件应用所需的所有工具。

该视频为您提供了Xilinx SDK的全面高级概述。

2018-11-26 07:12:00 6830

6830 了解Xilinx FSBL如何操作以启动Zynq器件。

包括程序执行概述,调试技巧以及有关特定引导设备的信息。

还包括FSBL角度的启动安全性简要概述。

2018-11-23 06:32:00 5155

5155 项目中主要用到的原语与IO端口有关,所以基本在Input/Output Functions 和IO两类中。下面着重介绍实际中所用到的几个原语,芯片A7系列。

2019-01-06 11:23:11 17316

17316

UltraRAM 原语(也称为 URAM)可在 Xilinx UltraScale +™ 架构中使用,而且可用来高效地实现大容量深存储器。

2019-07-13 11:08:09 8533

8533

在7系列设备的ILOGIC block中有专属的registers来实现input double-data-rate(DDR) registers。这些特性可以通过实例化IDDR 原语实现。

2020-12-28 17:13:13 13

13 注意:ODDR与IDDR工作有一个复位时间,大概110-120ns之间

IDDR是上升沿采一次数据,下降沿采一次数据,形成的双路数据在下一个时钟沿输出。

2020-12-30 16:27:49 16

16 高速串行信号,经过传输媒体(光缆或铜线),最后在接收端高速串行信号重新转换成低速并行信号。这种点对点的串行通信技术充分利用传输媒体的信道容量,减少所需的传输信道和器件引脚数目,提升信号的传输速度,从而大大降低通信成本。xilinx 7系列通过原语调用serdes接口,就可

2020-12-31 17:30:59 16

16 Xilinx公司的原语按照功能分为10类,包括:计算组件、I/O端口组件、寄存器和锁存器、时钟组件、处理器组件、移位寄存器、配置和检测组件、RAM/ROM组件、Slice/CLB组件以及G比特收发器组件。下面分别对其进行详细介绍。

2022-02-08 14:01:49 2259

2259

只能发生在FPGA的IOB上面,这里有特定的硬件结构可以实验上面单沿变双沿的方法,也就是使用原语进行一些列的操作。

2021-01-25 07:07:04 12

12 1 IDDR 1.1 介绍 该设计元素是专用的输入寄存器,旨在将外部双数据速率(DDR)信号接收到Xilinx FPGA中。IDDR可用的模式可以在捕获数据的时间和时钟沿或在相同的时钟沿向

2021-03-05 18:11:20 10879

10879

Xilinx公司的原语按照功能分为10类,包括:计算组件、I/O端口组件、寄存器和锁存器、时钟组件、处理器组件、移位寄存器、配置和检测组件、RAM/ROM组件、Slice/CLB组件以及G比特收发器组件。下面分别对其进行详细介绍。

2021-03-24 06:14:29 4

4 (29)FPGA原语设计(差分时钟转单端时钟)1.1 目录1)目录2)FPGA简介3)Verilog HDL简介4)FPGA原语设计(差分时钟转单端时钟)5)结语1.2 FPGA简介FPGA

2021-12-29 19:41:38 5

5 (30)FPGA原语设计(单端时钟转差分时钟)1.1 目录1)目录2)FPGA简介3)Verilog HDL简介4)FPGA原语设计(单端时钟转差分时钟)5)结语1.2 FPGA简介FPGA

2021-12-29 19:41:48 10

10 IBUFDS、和OBUFDS都是差分信号缓冲器,用于不同电平接口之间的缓冲和转换。IBUFDS 用于差分输入,OBUFDS用于差分输出。

2022-02-16 16:21:27 8348

8348

Xilinx SelectI IP是一个VHDL/Veilog封装文件,根据用户配置生成实例化的I/O逻辑,满足了输入SERDES、输出SERDES和延迟模块的应用要求。另外,它也可以例化生成所需的I/O时钟原语,将它连接到I/O引脚。

2022-06-06 09:46:43 3481

3481 在前一章中,我们介绍了Verilog HDL提供的内置基本门。本章讲述Verilog HDL指定用户定义原语U D P的能力。

2022-08-08 11:46:46 1616

1616 电子发烧友网站提供《Gowin原语用户指南.pdf》资料免费下载

2022-09-15 11:57:38 1

1 在SDR接口中,ODDR转发时钟(仍在时钟树内),输出端要直连到输出port,不可加逻辑,连接方式:输出时钟连接ODDR的C引脚,D1固定值1'b1, D2固定值1'b0,CE固定值1’b1,ODDR的输出Q连接到OBUF;

2023-06-21 14:11:06 3603

3603

在SDR接口中,ODDR转发时钟(仍在时钟树内),输出端要直连到输出port,不可加逻辑

2023-06-27 10:21:18 10801

10801

最近项目需要用到差分信号传输,于是看了一下FPGA上差分信号的使用。Xilinx FPGA中,主要通过原语实现差分信号的收发:OBUFDS(差分输出BUF),IBUFDS(差分输入BUF)。

2024-05-07 17:17:48 2524

2524

电子发烧友App

电子发烧友App

评论