资料介绍

作者:swang_shan

版权声明:本文为博主原创文章,遵循 CC 4.0 BY-SA 版权协议,转载请附上原文出处链接和本声明。

本文链接:https://blog.csdn.net/swang_shan/article/details/103806824

简介

原语(Primitive),是Xilinx针对其器件特征开发的一系列常用模块的名字,用户可以将其看成Xilinx公司为用户提供的库函数,是芯片中的基本元件,代表FPGA中实际拥有的硬件逻辑单元,如LUT,D触发器,RAM等,相当于软件中的机器语言。在实现过程中的翻译步骤时,要将所有的设计单元都转译为目标器件中的基本元件,否则就是不可实现的。原语在设计中可以直接例化使用,是最直接的代码输入方式,其和HDL语言的关系,类似于汇编语言和C语言的关系。

Xilinx公司提供的原语,涵盖了FPGA开发的常用领域,但只有相应配置的硬件才能执行相应的原语,并不是所有的原语都可以在任何一款芯片上运行。在Verilog中使用原语非常简单,将其作为模块名直接例化即可。

Xilinx公司的原语按照功能分为10类,包括:计算组件、I/O端口组件、寄存器和锁存器、时钟组件、处理器组件、移位寄存器、配置和检测组件、RAM/ROM组件、Slice/CLB组件以及G比特收发器组件。下面分别对其进行详细介绍。

1、 时钟组件

目前,大型设计一般推荐使用同步时序电路。同步时序电路基于时钟触发沿设计,对时钟的周期、占空比、延时和抖动提出了更高的要求。为了满足同步时序设计的要求,一般在FPGA设计中采用全局时钟资源驱动设计的主时钟,以达到最低的时钟抖动和延迟。 FPGA 全局时钟资源一般使用全铜层工艺实现,并设计了专用时钟缓冲与驱动结构,从而使全局时钟到达芯片内部的所有可配置单元(CLB)、I/O单元(IOB)和选择性块RAM(Block Select RAM)的时延和抖动都为最小。为了适应复杂设计的需要,Xilinx的FPGA中集成的专用时钟资源与数字延迟锁相环(DLL)的数目不断增加,最新的 Virtex II器件最多可以提供16个全局时钟输入端口和8个数字时钟管理模块(DCM)。

与全局时钟资源相关的原语常用的与全局时钟资源相关的Xilinx器件原语包括:IBUFG、IBUFGDS、BUFG、BUFGP、BUFGCE、BUFGMUX、BUFGDLL和DCM等。

IBUFG

即输入全局缓冲,是与专用全局时钟输入管脚相连接的首级全局缓冲。所有从全局时钟管脚输入的信号必须经过IBUFG 单元,否则在布局布线时会报错。 IBUFG支持AGP、CTT、GTL、GTLP、HSTL、LVCMOS、LVDCI、LVDS、LVPECL、LVTTL、PCI、PCIX和 SSTL等多种格式的IO标准。

IBUFGDS

IBUFG的差分形式,当信号从一对差分全局时钟管脚输入时,必须使用IBUFGDS作为全局时钟输入缓冲。IBUFG支持BLVDS、LDT、LVDSEXT、LVDS、LVPECL和ULVDS等多种格式的IO标准。

BUFG

全局缓冲,它的输入是IBUFG的输出,BUFG的输出到达FPGA内部的IOB、CLB、选择性块RAM的时钟延迟和抖动最小。

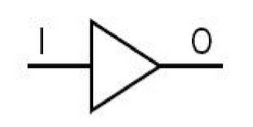

BUFG是具有高扇出的全局时钟缓冲器,一般由综合器自动推断并使用,其和同类原语的RTL结构如图所示。全局时钟是具有高扇出驱动能力的缓冲器,可以将信号连到时钟抖动可以忽略不计的全局时钟网络,BUFG组件还可应用于典型的高扇出信号和网络,如复位信号和时钟使能信号。如果要对全局时钟实现PLL或DCM等时钟管理,则需要手动例化该缓冲器。其例化的代码模板如下所示:

// BUFG: 全局时钟缓存(Global Clock Buffer),只能以内部信号驱动

// Xilinx HDL库向导版本,ISE 9.1

BUFG BUFG_inst (

.O(O), //时钟缓存输出信号

.I(I) // /时钟缓存输入信号

);

// 结束BUFG_ins模块的例化过程

BUFG—RTL

BUFG—RTL

4. BUFGCE是带有时钟使能端的全局缓冲。它有一个输入I、一个使能端CE和一个输出端O。只有当BUFGCE的使能端CE有效(高电平)时,BUFGCE才有输出。

5. BUFGMUX是全局时钟选择缓冲,它有I0和I1两个输入,一个控制端S,一个输出端O。当S为低电平时输出时钟为I0,反之为I1。需要指出的是BUFGMUX的应用十分灵活,I0和I1两个输入时钟甚至可以为异步关系。

6. BUFGP相当于IBUG加上BUFG。

7. BUFGDLL是全局缓冲延迟锁相环,相当于BUFG与DLL的结合。BUFGDLL在早期设计中经常使用,用以完成全局时钟的同步和驱动等功能。随着数字时钟管理单元(DCM)的日益完善,目前BUFGDLL的应用已经逐渐被DCM所取代。

8. DCM即数字时钟管理单元,主要完成时钟的同步、移相、分频、倍频和去抖动等。DCM与全局时钟有着密不可分的联系,为了达到最小的延迟和抖动,几乎所有的DCM应用都要使用全局缓冲资源。DCM可以用Xilinx ISE软件中的Architecture Wizard直接生成。

全局时钟资源的使用方法 全局时钟资源的使用方法(五种)

1:IBUFG + BUFG的使用方法:

IBUFG后面连接BUFG的方法是最基本的全局时钟资源使用方法,由于IBUFG组合BUFG相当于BUFGP,所以在这种使用方法也称为BUFGP方法。

2. IBUFGDS + BUFG的使用方法:

当输入时钟信号为差分信号时,需要使用IBUFGDS代替IBUFG。

3. IBUFG + DCM + BUFG的使用方法:

这种使用方法最灵活,对全局时钟的控制更加有效。通过DCM模块不仅仅能对时钟进行同步、移相、分频和倍频等变换,而且可以使全局时钟的输出达到无抖动延迟。

4. Logic + BUFG的使用方法:

BUFG不但可以驱动IBUFG的输出,还可以驱动其它普通信号的输出。当某个信号(时钟、使能、快速路径)的扇出非常大,并且要求抖动延迟最小时,可以使用BUFG驱动该信号,使该信号利用全局时钟资源。但需要注意的是,普通IO的输入或普通片内信号进入全局时钟布线层需要一个固有的延时,一般在 10ns左右,即普通IO和普通片内信号从输入到BUFG输出有一个约10ns左右的固有延时,但是BUFG的输出到片内所有单元(IOB、CLB、选择性块RAM)的延时可以忽略不计为“0”ns。

5. Logic + DCM + BUFG的使用方法:

DCM同样也可以控制并变换普通时钟信号,即DCM的输入也可以是普通片内信号。使用全局时钟资源的注意事项全局时钟资源必须满足的重要原则是:使用 IBUFG或IBUFGDS的充分必要条件是信号从专用全局时钟管脚输入。换言之,当某个信号从全局时钟管脚输入,不论它是否为时钟信号,都必须使用 IBUFG或IBUFGDS;如果对某个信号使用了IBUFG或IBUFGDS硬件原语,则这个信号必定是从全局时钟管脚输入的。如果违反了这条原则,那么在布局布线时会报错。这条规则的使用是由FPGA的内部结构决定的:IBUFG和IBUFGDS的输入端仅仅与芯片的专用全局时钟输入管脚有物理连接,与普通IO和其它内部CLB等没有物理连接。另外,由于BUFGP相当于IBUFG和BUFG的组合,所以BUFGP的使用也必须遵循上述的原则。

- AD5940评估套件使用方法.ppt 21次下载

- PICC安装及使用方法汇总 4次下载

- Xilinx-DCM的使用方法技巧 12次下载

- oracle-C#使用方法 6次下载

- ORCADCapture_使用方法与概念 29次下载

- 数字万用表的使用方法 27次下载

- 在FPGA中配置PLL的步骤及使用方法 20次下载

- 图解示波器使用方法与技巧 216次下载

- FPGA的LVDS介绍和xilinx原语的使用方法中文说明 5次下载

- xilinx原语使用方法 15次下载

- ORCAD PSPICE 使用方法 38次下载

- xilinx 原语使用方法 11次下载

- xilinx原语的使用方法 13次下载

- 示波器的使用方法 31次下载

- 十分钟学会Xilinx FPGA 设计 177次下载

- 如何用RTL原语实现MUX门级映射呢? 426次阅读

- 获取Xilinx FPGA芯片IDCODE的4种方法 1595次阅读

- CubeMX的基础使用方法 3465次阅读

- 光纤收发器的作用和使用方法 2.4w次阅读

- 新规划PCI核查工具的使用方法和应用事例 2436次阅读

- 在线式UPS电源的使用方法 7340次阅读

- 时控开关的应用及使用方法 1.3w次阅读

- 基于URAM原语创建容量更大的RAM 6674次阅读

- Xilinx FPGA常用原语介绍 1.5w次阅读

- Xilinx FPGA中SRL原理 7011次阅读

- 助焊膏怎么用_助焊膏的使用方法 5.3w次阅读

- 电流表的使用方法_钳型电流表的使用方法及图解 11.1w次阅读

- 钳型表如何使用_钳型表使用方法图解大全 9.8w次阅读

- 记利用compxlibgui工具编译Xilinx库 1274次阅读

- 详析示波器的使用方法和步骤 1.4w次阅读

下载排行

本周

- 1电子电路原理第七版PDF电子教材免费下载

- 0.00 MB | 1491次下载 | 免费

- 2单片机典型实例介绍

- 18.19 MB | 95次下载 | 1 积分

- 3S7-200PLC编程实例详细资料

- 1.17 MB | 27次下载 | 1 积分

- 4笔记本电脑主板的元件识别和讲解说明

- 4.28 MB | 18次下载 | 4 积分

- 5开关电源原理及各功能电路详解

- 0.38 MB | 11次下载 | 免费

- 6100W短波放大电路图

- 0.05 MB | 4次下载 | 3 积分

- 7基于单片机和 SG3525的程控开关电源设计

- 0.23 MB | 4次下载 | 免费

- 8基于AT89C2051/4051单片机编程器的实验

- 0.11 MB | 4次下载 | 免费

本月

- 1OrCAD10.5下载OrCAD10.5中文版软件

- 0.00 MB | 234313次下载 | 免费

- 2PADS 9.0 2009最新版 -下载

- 0.00 MB | 66304次下载 | 免费

- 3protel99下载protel99软件下载(中文版)

- 0.00 MB | 51209次下载 | 免费

- 4LabView 8.0 专业版下载 (3CD完整版)

- 0.00 MB | 51043次下载 | 免费

- 5555集成电路应用800例(新编版)

- 0.00 MB | 33562次下载 | 免费

- 6接口电路图大全

- 未知 | 30320次下载 | 免费

- 7Multisim 10下载Multisim 10 中文版

- 0.00 MB | 28588次下载 | 免费

- 8开关电源设计实例指南

- 未知 | 21539次下载 | 免费

总榜

- 1matlab软件下载入口

- 未知 | 935053次下载 | 免费

- 2protel99se软件下载(可英文版转中文版)

- 78.1 MB | 537793次下载 | 免费

- 3MATLAB 7.1 下载 (含软件介绍)

- 未知 | 420026次下载 | 免费

- 4OrCAD10.5下载OrCAD10.5中文版软件

- 0.00 MB | 234313次下载 | 免费

- 5Altium DXP2002下载入口

- 未知 | 233046次下载 | 免费

- 6电路仿真软件multisim 10.0免费下载

- 340992 | 191183次下载 | 免费

- 7十天学会AVR单片机与C语言视频教程 下载

- 158M | 183277次下载 | 免费

- 8proe5.0野火版下载(中文版免费下载)

- 未知 | 138039次下载 | 免费

电子发烧友App

电子发烧友App

创作

创作 发文章

发文章 发帖

发帖  提问

提问  发资料

发资料 发视频

发视频 上传资料赚积分

上传资料赚积分

评论