分频器是数字系统设计中的基本电路,根据不同设计的需要,我们会遇到偶数分频、奇数分频、半整数分频等,有时要求等占空比,有时要求非等占空比。在同一个设计中有

2010-09-03 17:04:20 2861

2861

RAM Bits 327,680Maximum Macrocells2,560Maximum I/O Pins 716图1 EP20K 系列的等效门数下面以EP20K1000E 为例详细说明FPGA

2012-03-01 10:08:53

在FPGA中,我们怎么实现除法操作?最简单的方法当然是调IP Core。在Divider Generator的IP Core中,我们可以选择有/无符号数进行除法,还可以选择除法的延迟。当然,延迟越小

2020-12-24 16:06:22

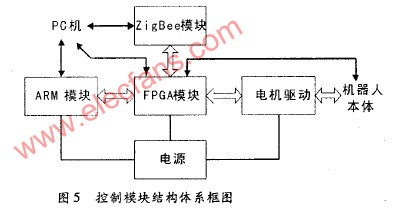

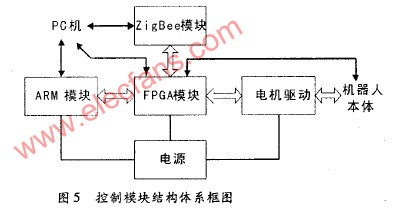

本文采用FPGA和ARM结合设计,很好地完成了多通道高精度的数据采集与处理,并且还详细介绍了FPGA逻辑的设计方法。

2021-05-06 06:21:48

ROHM开发出以2MHz开关频率实现业界最高降压比的DC/DC转换器IC“BD9V100MUF-C”,并已于2017年6月开始出售样品,于2017年12月投入量产。从2016年的CEATEC起

2018-12-04 10:22:26

,FPGA又是单片机和DSP的超集。也就是说,单片机和DSP能实现的功能,FPGA一般都能实现。在SoC设计中,基于FPGA器件设计工艺的发展使得越来越多的功能集成到一个芯片成为可能。为实现这一目标,有一种

2019-05-05 08:30:00

以FPGA为桥梁的FIFO设计方案是什么?以FPGA为桥梁的FIFO有哪些应用?

2021-04-29 07:05:18

本帖最后由 eehome 于 2013-1-5 09:47 编辑

周立功EASYFPGA原理图周立功大师经典力作,FPGA原理图。欢迎大家下载学习周立功大师EASY FPGA原理图

2012-03-16 11:02:04

咨询一个问题:CH34X系列USB转串口芯片的波特率分频方式只有整数分频?还是有小数分频?例如CP210x芯片的波特率生成只有整数分频,为48 MHz/(2 × Prescale × n),生成

2022-07-07 07:09:19

附件为使用FPGA实现两路CAN接口进行回环通信的工程文件。包含详细的工程使用说明文档。在小梅哥的Starter FPGA开发板上验证通过,CAN通信使用开源的OC_CAN IP和VP230收发器实现,上层应用使用NIOS II实现,使用非常方便。

2017-09-22 22:42:14

FPGA实现接口协议,完成接口数据的截获、处理(在本文中主要是数据加密)和转发,支持PIO和Ultra DMA两种数据传输模式。下面重点介绍用FPGA实现接口协议的方法。1 IDE接口协议简介1.1

2019-04-18 07:00:10

带通滤波器为例,较为详细地介绍了其设计和实现方法。给定巴特沃兹数字带通滤波器的抽样频率为500Hz,上、下边带截止频率分别为150Hz和30Hz.

2019-07-08 07:18:25

【摘要】:介绍了基于FPGA的任意分频系数的分频器的设计,该分频器能实现分频系数和占空比均可以调节的3类分频:整数分频、小数分频和分数分频。所有分频均通过VHDL语言进行了编译并且给出了仿真图。本

2010-04-26 16:09:01

双模前置小数分频原理是什么?如何对小数分频器进行仿真测试?

2021-04-29 07:29:41

小数分频器整数边界杂散问题的提出小数分频器整数边界杂散的优化设计

2021-04-19 08:32:15

FUT/FREF看起来是一个有理数,PLL配置为整数-N模式以获得最佳抖动性能(FS0)。有人知道是否有一种方法来禁用这个默认函数&仍然在分数模式,而不是整数模式的程序部分? 以上

2018-10-01 15:22:06

要设计小数分频PLL,基本架构已经确定:使用基于MASH111的DSM,双模预分频器+PScounter实现。现在遇到的问题是,不知道怎么把小数分频控制字经过DSM后的输出与整数分频控制字结合起来去控制(双模分频器+PScounter)可编程分频器此前没做过小数分频PLL,求助大佬们点拨一二

2021-06-24 07:20:38

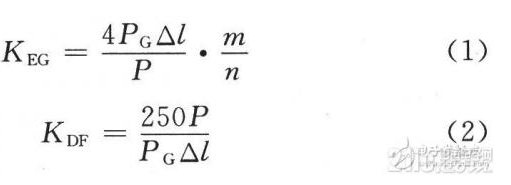

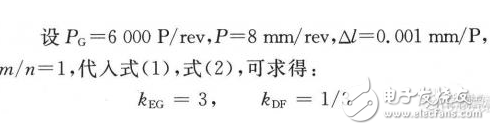

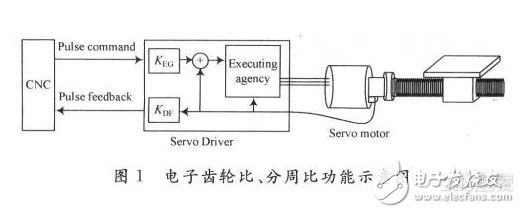

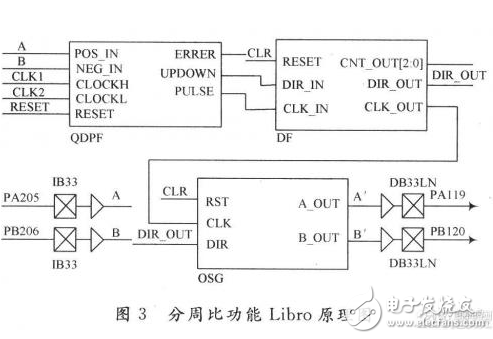

什么是电子齿轮比与分周比?分周比的结构是怎样构成的?

2021-04-29 06:11:55

求大神详细剖析GM的VOLT车

2021-05-18 06:14:30

本文以ADF 4153型小数分频频率合成器为例,给出了容易实现的三阶环路滤波器的设计方法,能够满足芯片实际测试的需要。

2021-04-30 06:55:25

使用VHDL语言怎样实现数控半整数分频器,就当输入为3时,就实现3.5分频,当输入为4时,就实现4.5分频,同时要求占空比为50%。

2014-12-02 18:28:57

请问频率合成器像LMX2594,LMX2595,LMX2694这类芯片的同步功能是都需要在整数分频模式下才能同步吗?

在TCIS软件中设置好像都需要整数分频才行,这样限制太大了,使用的频点都是要小数分频

2024-11-11 11:07:44

最近在学习周立功CAN的上位机编程,在网上下载了一份接口函数库的详细说明,比论坛上那份说明要详细些,新手可以下载下来看看。

2017-03-02 19:34:27

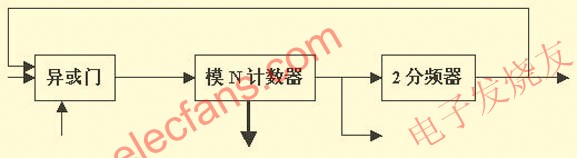

在复杂数字逻辑电路设计中,经常会用到多个不同的时钟信号。介绍一种通用的分频器,可实现2~256 之间的任意奇数、偶数、半整数分频。首先简要介绍了FPGA 器件的特点和应用范

2009-11-01 14:39:19 78

78 提出了一种基于FPGA 实现QPSK 调制器的方法。以FPGA 实现DDS,通过对DDS 信号输出相位的控制实现调相。仿真结果表明方案是可行的。

2009-12-18 11:57:08 66

66 波形发生器是信号处理领域中必不可少的设备。这里,介绍了基于FPGA 的模拟电路中阶梯波、阶梯波等常用渐变信号的波形实现方法,并详细地阐述了其相应硬件电路的工作原理

2009-12-19 16:17:30 40

40 NandFlash控制器的FPGA实现方法技巧与程序案例分享。

2017-09-21 09:40:00 78

78 基于FPGA 的等占空比任意整数分频器的设计

给出了一种基于FPGA 的等占空比任意整数分频电路的设计方法。首先简要介绍了FPGA 器件的特点和应用范围, 接着讨论了一

2010-02-22 14:22:32 39

39 简要介绍了CPLD/FPGA器件的特点和应用范围,并以分频比为2.5和1.5的分频器的设计为例,介绍了在MaxPlusII开发软件下,利用VHDL硬件描述语言以及原理图的输入方式来设计数字逻辑电路的过

2010-07-17 17:55:57 36

36 摘要:简要介绍了CPLD/FPGA器件的特点和应用范围,并以分频比为2.5的半整数分频器的设计为例,介绍了在MAX+plus II开发软件下,利用VHDL硬件描述语言以及原理图的输

2006-03-13 19:36:44 1072

1072

摘 要: 本文通过在QuartursⅡ开发平台下,一种能够实现等占空比、非等占空比整数分频及半整数分频的通用分频器的FPGA设计与实现,介绍了利用VHDL硬件描

2009-06-20 12:43:07 731

731

摘要:简要介绍了CPLD/FPGA器件的特点和应用范围,并以分频比为2.5的半整数分频器的设计为例,介绍了在MAX+plus II开发软件下,利用VHDL硬件描述语言以及原理图的输

2009-06-20 12:45:00 884

884

整数的表示方法

整数表示的数据的最小单位为1,可认为它是小数点定在数值最低位右面的一种数据。

2009-10-13 17:12:56 4631

4631 整数的编码方法

与定点小数的三种编码方法类似,整数也可以用原码、补码和反码三种不同的编码方法表示。区别主要表现在:

2009-10-13 17:19:26 5734

5734 摘要:文中详述了FPGA被动串行配置方式的时序,给出配置流程图及实现的程序代码,并通过实例验证了该方法的优越

2010-07-21 14:48:48 1692

1692

给出了一种小数分频技术的实现方法, 并在实验的基础上进一步证实了小数分频的可行性该法通过微机控制,

2011-02-22 14:58:54 45

45 将PCIE与PCI、K1.X等总线技术进行比较,分析它的技术特性和优势,剖析数据包在各层中的流动过程。/并且详细阐述基于FPGA的两种盯行性实现方案,即采用第三方PHY接口器件和低成本

2011-08-31 17:42:49 156

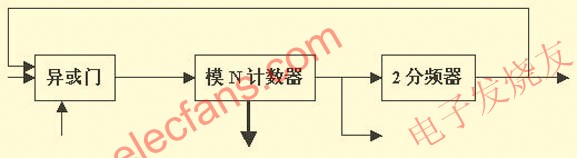

156 提出了一种基于FPGA的小数分频实现方法,介绍了现有分频方法的局限性,提出一种新的基于两级计数器的分频实现方法,给出了该设计方法的设计原理以及实现框图

2011-11-09 09:36:22 121

121 给出了一种基于FPGA的分频电路的设计方法.根据FPGA器件的特点和应用范围,提出了基于Verilog的分频方法.该方法时于在FPGA硬件平台上设计常用的任意偶数分频、奇数分频、半整数分频

2011-11-09 09:49:33 355

355 本文提出了一种用FPGA实现纠错编码的设计思想,并以Altera MAX+PluslI为硬件开发平台。利用FPGA编程的特点,用软件编程方法,很好的解决了纠错编码中存在的码速变换和实时性问题,实现

2011-11-10 17:10:59 61

61 介绍了一种基于FPGA的双模前置小数分频器的分频原理及电路设计,并用VHDL编程实现分频器的仿真.

2011-11-29 16:43:06 48

48 LMX2531 系列产品被广泛应用于无线通讯基站系统,相比较整数分频,采用小数分频可以获得更好的相位噪声性能,但是小数分频会导致杂散问题,特别是整数边界杂散尤为突出。本文介绍一种在尽可能保证相位噪声性能的基础上,改善整数边界杂散达10dB。

2013-04-27 15:51:04 3492

3492 用 Verilog实现基于FPGA 的通用分频器的设计时钟分频包括奇数和偶数分频

2016-07-14 11:32:47 46

46 华清远见FPGA代码-整数DCT变换的设计与实现

2016-10-27 18:07:54 8

8 大咖及嘉宾均发表了对物联网产业及发展趋势的各自看法。广州致远电子周立功先生在会上对于企业和个人成功、稳健可持续发展发表了极其精彩的演讲,虽然周先生以理论说明居多,但每一个方法论确实点到实处,听到的人都

2016-12-16 18:56:00 1441

1441 基于HEVC整数DST的VLSI设计与实现_杜高明

2017-01-03 17:41:32 0

0 基于DSP的FPGA配置方法研究与实现

2017-10-19 16:15:19 36

36 本文详细介绍了完整数据采集系统的硬件的构建方法。

2017-11-15 14:35:34 20

20 部分组成。对FPGA进行测试要对FPGA内部可能包含的资源进行结构分析,经过一个测试配置(TC)和向量实施(TS)的过程,把FPGA配置为具有特定功能的电路,再从应用级别上对电路进行测试,完成电路的功能及参数测试。 2 FPGA的配置方法 对FPGA进行配置有多种方法可以选择,包括边界扫描配置方法等。

2017-11-18 10:44:37 3307

3307

的使用,同时以整数数据处理方式实现了向导滤波器中方差和变换系数的计算,并且通过参数调整,可以方便地实现不同大小图像的不同尺寸窗口的向导滤波。在Altera公司Cyclone系列FPGA芯片上进行了综合,实验结果表明,向导滤波整数FPGA结构的处理结果与

2017-11-22 15:43:12 12

12 电动机是各类数控机床的重要执行部件。要实现对电动机的精确位置控制,转子的位置必须能够被精确的检测出来。光电编码器是目前最常用的检测器件。光电编码器分为增量式、绝对式和混合式。其中,增量式以其构造简单

2017-11-23 10:05:01 1267

1267 FPGA仿真篇-使用脚本命令来加速仿真二 基于FPGA的HDMI高清显示借口驱动 基于FPGA灰度图像高斯滤波算法的实现 FPGA为什么比CPU和GPU快 基于Xilinx FPGA的视频图像采集

2018-02-20 20:49:00 1934

1934 三分频,五分频,七分频等等奇数类分频,那究竟怎么办呢?在这里,让我介绍一个可以实现任意整数分频的方法,这个办法也是同样利用了计数器来计算,当是跟偶数分频不一样的地方是任意整数分频利用了两个计数器来实现。 设计原理 : 本

2018-06-13 11:21:48 13569

13569

高精度相对GPS定位是基于非常精确的载波相位测量。为了在短时间内获得高精度的结果,必须利用模糊度的整数性质。本文回顾了基于双差分GPS观测模型的参数估计的全过程,重点讨论了GPS双差分模糊度的整数估计。

2018-10-15 08:00:00 12

12 建立了一个基于FPGA的可实现流水化运行的OFDM系统的硬件平台,包括模拟前端、基于FPGA的OFDM调制器和OFDM 解调器。重点给出了OFDM调制解调器的实现构架,对FPGA实现方法进行了详细的描述,介绍了系统调试方法,并对系统进行了性能评价。

2018-12-13 16:45:51 22

22 分频器主要分为偶数分频、奇数分频、半整数分频和小数分频,如果在设计过程中采用参数化设计,就可以随时改变参量以得到不同的分频需要。

2019-02-01 01:28:00 18914

18914

本文档详细介绍的是FPGA良好设计方法及误区的详细资料说明主要内容包括了:1.FPGA的适用领域及选型,2.FPGA系统设计典型流程,3.FPGA逻辑设计良好设计方法一引入,4.FPGA的设计方法,5.FPGA系统设计中的误区

2019-02-26 11:03:16 13

13 本文档的主要内容详细介绍的是FPGA设计的思路和方法初探详细资料免费下载。

2019-02-26 14:09:40 11

11 本文档的主要内容详细介绍的是FPGA教程之FPGA系统设计的主要思路和方法初探资料说明包括了:1.FPGA的适用领域及选型FPGA系统设计典型流程,2.FPGA逻辑设计方法 弓|入ASIC的设计方法,3.FPGA设计的常用技巧,4.FPGA系统设计中的对与错

2019-04-04 17:19:58 55

55 本文档的详细介绍的是FPGA设计有哪些良好的设计方法及误区内容包括了:1.FPGA的适用领域及选型,2.FPGA系统设计典型流程,3.FPGA逻辑设计良好设计方法一引入ASIC的设计方法,4.FPGA设计的常用技巧,5.FPGA系统设计中的误区

2019-04-18 17:30:04 23

23 分支定界法是一种求解离散最优化问题的计算分析方法。它是由Land Doig和Dakin等人在20世纪60年代初提出的。分支定界法可求纯整数或混合整数线性规划问题,求解方法由分支和定界组成。“分支”为

2019-06-03 08:00:00 5

5 分频器是一种基本电路,通常用来对某个给定频率进行分频,得到所需的频率。整数分频器的实现非常简单,可采用标准的计数器,也可以采用可编逻辑器件设计实现。但在某些场合下,时钟源与所需的频率不成整数倍关系,此时可采用小数分频器进行分频。

2019-11-20 07:05:00 7995

7995 对于CPLD/FPGA初学者而言,如何实现双向信号往往是个难题。duoduo 当年初接触CPLD/FPGA的时候也为这个问题头疼过。让我们透过下面这个简单的例子看看CPLD/FPGA设计中如何实现双向信号。

2019-06-11 16:13:51 15

15 一旦仅用于胶合逻辑,FPGA已经发展到可以在单个器件上构建片上系统(SoC)设计的程度。门和功能的数量急剧增加,以与传统上仅通过ASIC设备提供的功能相竞争。本文介绍了FPGA设计方法优于ASIC的一些优势,包括早期上市,轻松过渡到结构化ASIC,以及降低NRE成本。

2019-09-14 12:28:00 2923

2923 本文档的主要内容详细介绍的是使用FPGA实现LED实验的详细资料说明。

2019-12-11 16:23:00 9

9 公司的FPGA和Spasion公司的Nor Flash,详细介绍了Flash控制器设计和在线加载功能的实现方法。

2020-01-27 16:17:00 4257

4257

讨论了利用FPGA工具实现MBUS总线的原理、方法,以实际操作介绍了FPGA设计流程,并给出FPGA常用设计技巧。

2019-12-24 14:54:08 9

9 在数字系统设计中,根据不同的设计需要,经常会遇到偶数分频、奇数分频、半整数分频等,有的还要求等占空比。在基于cpld(复杂可编程逻辑器件)的数字系统设计中,很容易实现由计数器或其级联构成各种形式的偶数分频及非等占空比的奇数分频,但对等占空比的奇数分频及半整数分频的实现较为困难。

2020-06-26 09:36:00 1482

1482

的UART的实现方法,具体描述了发送、接收等模块的设计,恰当使用了有限状态机,实现了FPGA上的UART的设计,给出仿真结果。

2020-07-07 15:51:05 12

12 本文档的主要内容详细介绍的是三种16位整数运算器的ALU设计方法工程文件免费下载。

2020-09-16 17:12:23 26

26 简要介绍广泛应用于雷达信号处理中的恒虚警率( CFAR) 的基本原理。通过对数据流的分析, 依据CFAR 算法规则简单的特点, 提出一种基于FPGA 的实现方案, 并详细介绍用FPGA 实现CFAR 的原理、电路组成和各部分电路的设计方法。

2020-11-05 14:53:00 17

17 功耗是我们关注的设计焦点之一,优秀的器件设计往往具备低功耗特点。在前两篇文章中,小编对基于Freez技术的低功耗设计以及FPGA低功耗设计有所介绍。为增进大家对低功耗的了解,以及方便大家更好的实现低功耗设计,本文将对FPGA具备的功耗加以详细阐述。如果你对低功耗具有兴趣,不妨继续往下阅读哦。

2021-02-14 17:50:00 7165

7165 为了满足整数小波变换实时应用的需要,研究了整数小波变换的FPGA实现问题。相对于DSP等传统实现方式,用FPGA实现整数小波变换具有处理速度快,可重新配置硬件,易于修改移植等优点。论文首先描述了二维

2021-02-01 11:53:33 9

9 基于小波变换的滤波方法应用于红外图像处理中可以在降低噪声的同时提升图像细节,有效改善图像画质。介绍了一种采用FPGA的小波图像处理方法及其硬件处理架构。通过合理有效地进行算法硬件设计,在单片FPGA芯片上实现了图像的实时处理,有利于红外机芯的小型化。

2021-02-01 14:54:00 6

6 简要介绍了CPLD/FPGA器件的特点和应用范围,并以分频比为2.5和1.5的分频器的设计为例,介绍了在MaxPlusII开发软件下,利用VHDL硬件描述语言以及原理图的输入方式来设计数字逻辑电路的过程和方法。该设计具有结构简单、实现方便、便于系统升级的特点。

2021-03-16 09:45:53 10

10 简要介绍了 CPLD/FPGA器件的特点和应用范围,并以分频比为2.5和15的分频器的设计为例,介绍了在 Maxplusll开发软件下,利用ⅤHDL硬件描述语言以及原理图的输入方式来设计数字逻辑电路的过程和方法。该设计具有结构简单、实现方便、便于系统升级的特点。

2021-03-22 16:52:15 5

5 简要介绍了CPLD/FPGA器件的特点和应用范围,并以分频比为25和15的分频器的设计为例,介绍了在 Maxplus开发软件下,利用VHDL硬件描述语言以及原理图的输入方式来设计数字逻辑电路的过程和方法该设计具有结构简单、实现方便、便于系统升级的特点。

2021-04-12 16:29:05 11

11 基于FPGA的神经网络硬件实现方法说明。

2021-06-01 09:35:16 51

51 基于CPLD/FPGA的半整数分频器设计方案

2021-06-17 09:37:02 21

21 基于新型FPGA的FFT设计与实现设计方法。

2021-06-17 17:07:03 49

49 2.3 python整数与浮点数 Python 支持的数字类型有三种:整数、浮点数和复数。 1. 整数(Int) 通常被称为整型,是正或负整数,不带小数点。例如:1,100,-8080,0,等等

2022-02-18 09:09:53 2499

2499 波形,同时在低频的情况下,性噪比不是特别好。 2:采用FPGA+DA的方法实现。这个的做法复杂很多,其中安捷伦的信号源就是这样做法,在这里着重说一下这个的实现方法。 1):正弦波可以采用FPGA内部的DDS或者cordic算法实现,这个根据需求与FPGA资源进行决定。 2):方

2022-03-23 14:06:43 2575

2575 时序至关重要:改善分数分频锁相环合成器中的整数边界杂散状况

2022-11-04 09:50:31 1

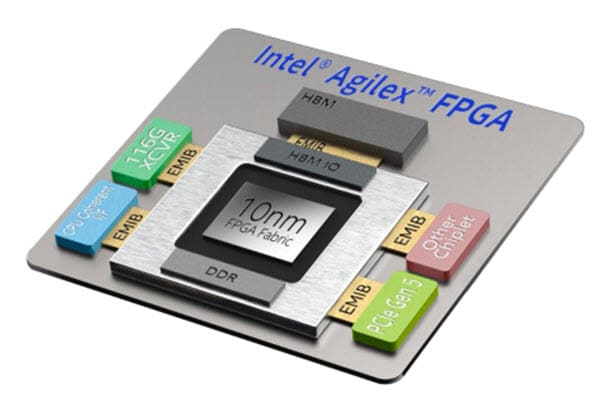

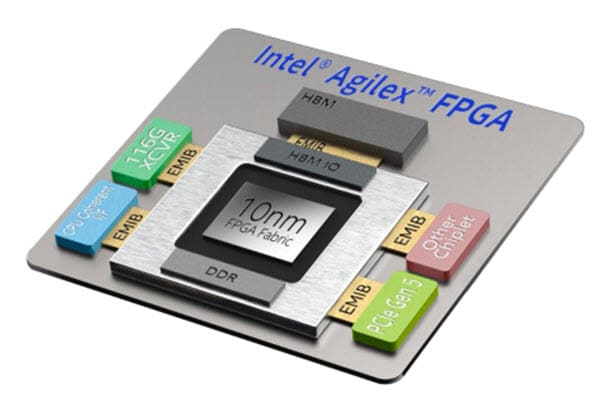

1 使用英特尔® Agilex™ FPGA 解决以数据为中心的挑战

2023-01-04 11:17:19 1334

1334

所谓“分频”,就是把输入信号的频率变成成倍数地低于输入频率的输出信号。数字电路中的分频器主要是分为两种:整数分频和小数分频。其中整数分频又分为偶分频和奇分频,首先从偶分频开始吧,入门先从简单的开始!

2023-03-23 15:06:22 3014

3014

前面分别介绍了偶数和奇数分频(即整数分频),接下来本文介绍小数分频。

2023-03-23 15:08:04 2192

2192

初学 Verilog 时许多模块都是通过计数与分频完成设计,例如 PWM 脉宽调制、频率计等。而分频逻辑往往通过计数逻辑完成。本节主要对偶数分频、奇数分频、半整数分频以及小数分频进行简单的总结。

2023-03-29 11:38:40 6826

6826

是用于满足设计的需求。 分频:产生比板载时钟小的时钟。 倍频:产生比板载时钟大的时钟。 二:分频器的种类 对于分频电路来说,可以分为整数分频和小数分频。 整数分频:偶数分频和奇数分频。 小数分频:半整数分频和非半整数分频。 三:分频器的思想 采用计数器的思想实

2023-11-03 15:55:02 3266

3266

锁相环整数分频和小数分频的区别是什么? 锁相环(PLL)是一种常用的电子电路,用于将输入的时钟信号与参考信号进行同步,并生成输出信号的一种技术。在PLL中,分频器模块起到关键作用,可以实现整数分

2024-01-31 15:24:48 5373

5373 基于FPGA的单芯片实现方法具有低成本和快速面市等优点,是多芯片和ASICSoC非常有吸引力的替代方案

2024-03-21 14:04:56 1408

1408

噪声系数分析仪是一种用于测量接收机、放大器等电子设备噪声系数的仪器。噪声系数是衡量设备在接收信号时引入的噪声水平的指标,对于通信系统的性能至关重要。本文将详细介绍噪声系数分析仪的使用方法和校准规范

2024-06-03 16:12:52 3128

3128 智慧灯杆案例剖析丨北京经开区:以智慧灯杆为入口建设智慧城市

2025-02-20 14:37:58 888

888 AMD UltraScale架构:高性能FPGA与SoC的技术剖析 在当今的电子设计领域,高性能FPGA和MPSoC/RFSoC的需求日益增长。AMD的UltraScale架构凭借其创新的技术和卓越

2025-12-15 14:35:09 246

246

电子发烧友App

电子发烧友App

评论