LED的多种形式封装结构及技术

LED是一类可直接将电能转化为可见光和辐射能的发光器件,具有工作电压低,耗电量小,发光

2009-12-31 09:09:03 1454

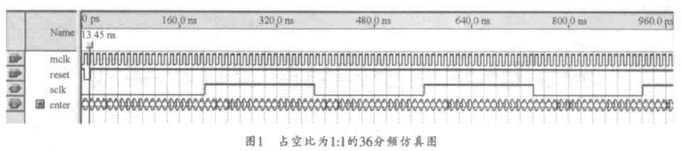

1454 分频器是数字系统设计中的基本电路,根据不同设计的需要,我们会遇到偶数分频、奇数分频、半整数分频等,有时要求等占空比,有时要求非等占空比。在同一个设计中有

2010-09-03 17:04:20 2861

2861

可穿戴设备正在经历高速的发展,更方便的佩戴形式、更先进的数据采集及分析系统,都是它们需要不断完善的。目前,世界上的科技巨头们都在积极分析可穿戴设备的发展及可行性,用于弥补智能手机饱和带来的利润空缺。

2014-02-24 09:31:47 1328

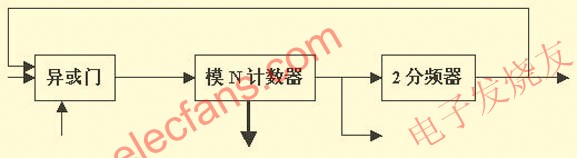

1328 本文首先介绍了各种分频器的实现原理,并在FPGA开发平台上通过VHDL文本输入和原理图输入相结合的方式,编程给出了仿真结果。最后通过对各种分频的分析,利用层次化设计思想,综合设计出了一种基于FPGA的通用数控分频器,通过对可控端口的调节就能够实现不同倍数及占空比的分频器。

2015-05-07 09:43:16 5706

5706

;文献[5]给出了FPGA内部没计TS101链路口的框图,但只给出了简单的介绍,无法给设计者以参考。本文采用Altera公司Cyclone系列芯片EP1C12实现了与TS101/TS201两种芯片的链路口

2019-06-19 05:00:08

;文献[5]给出了FPGA内部没计TS101链路口的框图,但只给出了简单的介绍,无法给设计者以参考。本文采用Altera公司Cyclone系列芯片EP1C12实现了与TS101/TS201两种芯片的链路口

2018-12-04 10:39:29

初学FPGA,听说分频貌似挺重要,是必备的基础技能。小白的我今天就从奇偶分频开始我的FPGA学习成长之路偶数分频很简单的哈,打字蛮累的,直接上代码/*************6分频

2016-03-30 11:35:51

`基于FPGA+的任意小数分频器的设计基于FPGA的多种分频设计与实现基于FPGA的小数分频器的实用Verilog 实现基于FPGA 的通用分频用Verilog+HDL实现基于FPGA的通用分频

2012-02-03 15:02:31

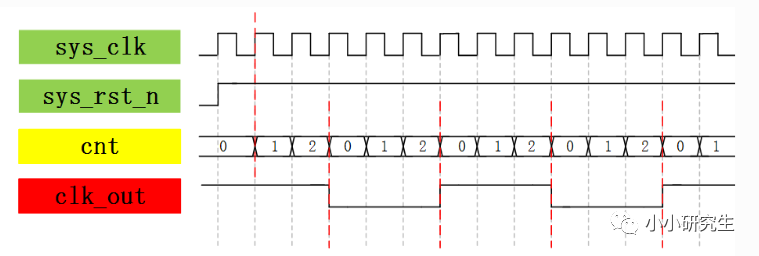

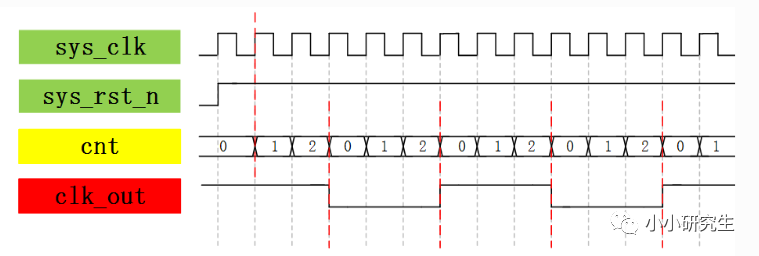

分频器模块实现的基本原理就是设计一个工作在系统时钟下的计数器,循环地递减或者递加计数,在某个计数的固定值将输出翻转,即可实现时钟分频的功能。例如,实验板上的系统时钟是 50MHz,而所需的读写周期

2018-11-15 09:25:35

谁帮忙设计一下模数转换芯片ADC0809以及串行通信部分均需要有相应的时钟驱动。而此次选择的Altera CycloneⅡ系列FPGA中的EP2C5T144C8的系统时钟为20MHz,因此根据需要

2014-05-09 11:53:23

fpga 基于quartus ii的原理图设计 有哪些分频模块啊

2011-11-18 11:03:34

`fpga应用篇(三):你可能用了假分频 分频对于fpga的重要性不言而喻,对于大多数通信方式来说,一个稳定且准确的分频程序对于通信的稳定很重要。为什么你的UART总是不稳定,很有可能你用了一个假

2017-04-07 21:03:07

多种EDA工具的FPGA设计方案

2012-08-17 10:36:17

多种开发板FPGA原理图

2013-10-29 16:47:12

,一旦为低,FPGA指示程序数据加载 CRC校验出错。此时需要复位FPGA,重新加载。4、嵌入式 的驱动实现本文以模块形式实现了运行于上的驱动程序,源文件如下(有关寄存器的设置参考的数据手册,以下源代码

2019-12-10 17:42:18

Actel FPGA PLL锁相环的最大能达到几倍频几分频?我在网上查了一下有人说是20倍频,10分频,但是我没有在芯片手册里面找到资料,想要确认一下。

2014-12-04 11:25:15

GSM赋予基站的无线组网特性使基站的实现形式可以多种多样--宏蜂窝、微蜂窝、微微蜂窝及室内、室外型基站,无线频率资源的限制又使人们更充分地发展着基站的不同应用形式来增强覆盖,吸收话务--远端 TRX、分布天线系统、光纤分路系统、直放站。

2019-10-31 09:11:24

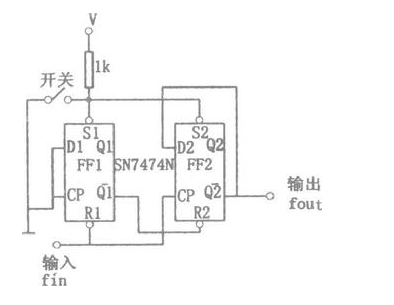

`我想采集电压信号然后将它转换成电流信号,但是它俩差了90度相位角想的是通过先倍频再分频来实现我看了一下网上可以用D触发器来实现,但是这样的倍频与分频过后相位并没有改变这个电路原理上有什么问题?有没有朋友做过类似的电路可以实现这样的功能`

2015-05-13 19:49:35

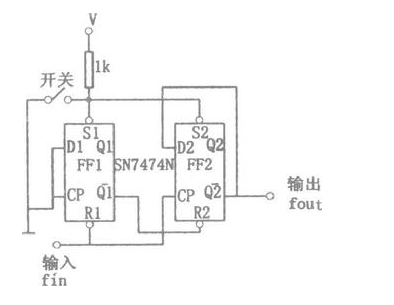

各位FPGA的高手们,小弟再做一个FPGA二分频信号时,有一个很困惑的问题,一直搞不明白,具体要求如下硬件连接,编程要求图中电源电压VCC=3.3V,R1 = 1×(1±10%)KΩ,R2 = 1

2015-03-13 13:35:12

//分频程序修订版,只需要修改一个参数就可以完成指定的分频工作//修改DIV参数即可,最大支持2的32方分频module div(clk_out, clk_in, rst);output

2019-12-12 14:35:25

分频器是FPGA设计中使用频率非常高的基本设计之一,尽管在目前大部分设计中,广泛使用芯片厂家集成的锁相环资源,如赛灵思(Xilinx)的DLL.来进行时钟的分频,倍频以及相移。但是对于时钟要求不高

2019-06-14 06:30:00

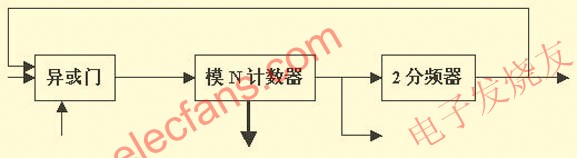

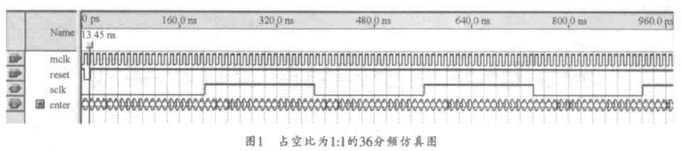

基于FPGACPLD的占空比为1∶n的n分频器的设计

2017-09-30 09:11:08

本帖最后由 weihu_lu 于 2014-6-19 16:25 编辑

作者:卢威虎1、前言 分频器是FPGA设计中使用频率非常高的基本单元之一。尽管目前在大部分设计中还广泛使用集成锁相环(如

2014-06-19 16:15:28

【摘要】:介绍了基于FPGA的任意分频系数的分频器的设计,该分频器能实现分频系数和占空比均可以调节的3类分频:整数分频、小数分频和分数分频。所有分频均通过VHDL语言进行了编译并且给出了仿真图。本

2010-04-26 16:09:01

中从电子设计的外围器件逐渐演变为数字系统的核心。伴随着半导体工艺技术的进步,FPGA器件的设计技术取得了飞跃发展及突破。分频器通常用来对某个给定的时钟频率进行分频,以得到所需的时钟频率。在设计数

2019-10-08 10:08:10

分频器在CPLD/FPGA设计中使用频率比较高,尽管目前大部分设计中采用芯片厂家集成的锁相环资源 ,但是对于要求奇数倍分频(如3、5等)、小数倍(如2.5、3.5等)分频、占空比50%的应用场合却往往不能满足要求。利用CPLD/FPGA设计多功能分频器,我们具体该怎么做呢?

2019-08-12 07:50:25

分频器是FPGA设计中使用频率非常高的基本设计之一,尽管在目前大部分设计中,广泛使用芯片厂家集成的锁相环资源,如赛灵思(Xilinx)的DLL.来进行时钟的分频,倍频以及相移。但是对于时钟要求不高

2019-07-09 09:11:47

怎么设计一款基于FPGA的多种分频设计?

2021-05-08 07:06:43

汽车电子锁有多种形式,常见的是电子钥匙式电子锁。这种电子锁的钥匙内藏电子电路存储密码,通过光、电和磁性等多种形式和主控电路联系。

2020-03-19 09:01:27

我想对2GHz的正弦波(相位噪声很低)进行16分频,分频出来的125M信号输入给FPGA,想选用ADi的分频器实现分频功能,我有以下几个问题:1.我查了ADi的分频器,分为(1)时钟分频器,(2

2019-01-11 13:39:43

进行读写操作和异步读写时钟的FIFO。这是MII接口设计中的难点,本身也具有很高的实用价值。奇偶分频器的实现分频器是数字系统设计中的基本电路,同一个设计中有时要求多种形式的分频。通常由计数器或计数器

2019-04-30 07:00:16

专用协议MAC的形式实现实时功能。而协议的其他功能由运行在嵌入式处理器中的软件堆栈来完成,这些处理器可以是在Cyclone III FPGA中实现的Nios II软核处理器。

2019-07-29 07:40:50

在复杂数字逻辑电路设计中,经常会用到多个不同的时钟信号。介绍一种通用的分频器,可实现2~256 之间的任意奇数、偶数、半整数分频。首先简要介绍了FPGA 器件的特点和应用范

2009-11-01 14:39:19 78

78 本文介绍了一种能够完成半整数和各种占空比的奇/偶数和的通用的分频器设计,并给出了本设计在Altera公司的FLEX10K系列EPF10K10LC84-3型FPGA芯片中实现后的测试数据和设计硬件的测

2009-12-19 16:25:09 65

65 基于FPGA 的等占空比任意整数分频器的设计

给出了一种基于FPGA 的等占空比任意整数分频电路的设计方法。首先简要介绍了FPGA 器件的特点和应用范围, 接着讨论了一

2010-02-22 14:22:32 39

39 简要介绍了CPLD/FPGA器件的特点和应用范围,并以分频比为2.5和1.5的分频器的设计为例,介绍了在MaxPlusII开发软件下,利用VHDL硬件描述语言以及原理图的输入方式来设计数字逻辑电路的过

2010-07-17 17:55:57 36

36 摘要:简要介绍了CPLD/FPGA器件的特点和应用范围,并以分频比为2.5的半整数分频器的设计为例,介绍了在MAX+plus II开发软件下,利用VHDL硬件描述语言以及原理图的输

2006-03-13 19:36:44 1072

1072

用VHDL语言实现3分频电路

标签/分类:

众所周知,分频器是FPGA设计中使用频率非常高的基本设计之一,尽管在目前大部分设计中,广泛使用芯片厂家集成的锁相

2007-08-21 15:28:16 5980

5980 基于多种EDA工具的FPGA设计

介绍了利用多种EDA工具进行FPGA设计的实现原理及方法,其中包括设计输入、综合、功能仿真、实现、时序仿真、配置下载等具体内容。并以实

2009-05-14 18:38:38 1036

1036

摘要:介绍了利用多种EDA工具进行FPGA设计的实现原理及方法,其中包括设计输入、综合、功能仿真、实现、时序仿真、配置下载等具体内容。并以实际操作介绍了

2009-06-20 11:42:45 674

674

摘要:介绍了为PET(正电子发射断层扫描仪)的前端电子学模块提供时间基准而设计的一种新型高频时钟扇出电路。该电路利用FPGA芯片来实现对高频时钟的分频

2009-06-20 12:41:04 1531

1531

摘要:简要介绍了CPLD/FPGA器件的特点和应用范围,并以分频比为2.5的半整数分频器的设计为例,介绍了在MAX+plus II开发软件下,利用VHDL硬件描述语言以及原理图的输

2009-06-20 12:45:00 884

884

用VHDL语言实现3分频电路(占空比为2比1)

分频器是FPGA设计中使用频率非常高的基本设计之一,尽管在目前大部分设计中,广泛使用芯片厂家集成的锁

2009-06-22 07:46:33 8956

8956 基于CPLD/FPGA的多功能分频器的设计与实现

引言

分频器在CPLD/FPGA设计中使用频率比较高,尽管目前大部分设计中采用芯片厂家集成的锁相环资源 ,但是对于要求

2009-11-23 10:39:48 1599

1599

多种EDA工具的FPGA设计方案

概述:介绍了利用多种EDA工具进行FPGA设计的实现原理及方法,其中包括设计输入、综合、功能仿真、实现、时序仿真、配

2010-05-25 17:56:59 895

895

给出了一种小数分频技术的实现方法, 并在实验的基础上进一步证实了小数分频的可行性该法通过微机控制,

2011-02-22 14:58:54 45

45 为了对运动控制系统中的脉冲进行精确控制以减少累计误差,需要对脉冲进行分、倍频和合成处理。介绍了通用的各种形式分频器的实现方法,给出了在Altera公司的Cyclone II系列EP2C8Q208C8型

2011-06-13 16:53:56 66

66 分析了应用于倍频电路的预置可逆分频器的工作原理,推导了触发器的驱动函数。并建立了基于simulink 和FPGA 的分频器模型,实验结果表明分频器可以实现预置模和可逆分频功能,满足倍

2011-08-17 16:50:45 2408

2408

为了对运动控制系统中的脉冲进行精确控制以减少累计误差,需要对脉冲进行分、倍频和合成处理。介绍了通用的各种形式分频器的实现方法,给出了在Altera公司的CyclONe II系列EP2C8Q208C8型

2011-10-21 17:55:34 32

32 该电路是低噪声微波小数N分频PLL的完整实现方案,以 ADF4156 作为核心的小数N分频PLL器件。使用 ADF5001 外部预分频器将PLL频率范围扩展至18 GHz。

2011-10-26 15:02:22 1852

1852

本文给出了分频技术通用模型。并结合最新的一些分频技术,提出了一种基于FPGA全新的分频系统的设计方法,简单的介绍了设计的思路、原理及其算法,并对该方案的性能进行了分析,

2011-11-08 18:03:32 138

138 提出了一种基于FPGA的小数分频实现方法,介绍了现有分频方法的局限性,提出一种新的基于两级计数器的分频实现方法,给出了该设计方法的设计原理以及实现框图

2011-11-09 09:36:22 121

121 给出了一种基于FPGA的分频电路的设计方法.根据FPGA器件的特点和应用范围,提出了基于Verilog的分频方法.该方法时于在FPGA硬件平台上设计常用的任意偶数分频、奇数分频、半整数分频

2011-11-09 09:49:33 355

355 介绍了一种基于FPGA的双模前置小数分频器的分频原理及电路设计,并用VHDL编程实现分频器的仿真.

2011-11-29 16:43:06 48

48 本文详细介绍了已在实际项目中应用的基于FPGA的图形式AMLCD控制器设计,这种设计方法稍作修改即可应用于常见VGA视频接口电路的设计。

2011-12-21 10:38:20 1783

1783

本书比较全面地阐述了fpga在数字信号处理中的应用问题。本书共分8章,主要内容包括典型fpga器件的介绍、vhdl硬件描述语言、fpga设计中常用软件简介、用fpga实现数字信号处理的数据规划、多种

2015-12-23 11:07:46 47

47 用 Verilog实现基于FPGA 的通用分频器的设计时钟分频包括奇数和偶数分频

2016-07-14 11:32:47 46

46 最近正在准备找工作,由于是做FPGA开发,所以verilog实现技术分频电路是一道经常出现的题目,三分频,五分频电路等等;经过一下午时间总结出了一个通用电路,可以实现任意奇数分频电路。

2017-02-09 14:21:08 2935

2935 分频器是FPGA设计中使用频率非常高的基本设计之一,尽管在目前大部分设计中,广泛使用芯片厂家集成的锁相环资源,如赛灵思(Xilinx)的DLL.来进行时钟的分频,倍频以及相移。

2017-02-11 12:33:40 12116

12116 XC5LX50T为例,这款FPGA集成了一个PCIE的Endpoint以及12个可以支持6 Gb/s以上的高速串行接口模块,支持串行RapidIO、fiber channel以及其他多种串行协议。

2018-07-20 11:42:00 2009

2009

DIP(DualIn-linePackage),即双列直插式封装,绝大多数中小规模集成电路均采用这种封装形式,其引脚数一般不超过100个。DIP封装的芯片有两排引脚,分布于两侧,且成直线平行布置

2018-06-14 14:40:00 3505

3505 液晶显示器IC的封装有多种形式,主要有DIP、SOP、SOJ、QFP(PQFP、TQFP)、PLCC和BGA封装等

2018-06-17 09:25:00 4292

4292 设计背景: 分频在 fpga的设计中一直都担任着很重要的角色,而说到分频,我相信很多人都已经想到了利用计算器来计算达到想要的时钟频率,但问题是仅仅利用计数器来分频,只可以实现偶数分频,而如果我需要

2018-06-13 11:21:48 13569

13569

分频器是FPGA设计中使用频率非常高的基本单元之一。尽管目前在大部分设计中还广泛使用集成锁相环(如altera的PLL,Xilinx的DLL)来进行时钟的分频、倍频以及相移设计,但是,对于时钟要求

2019-08-07 08:00:00 10310

10310

VaaS形式化验证平台,采用了多种形式化验证方法,具有验证效率高、自动化程度高、人工参与度低、易于使用、支持多个合约开发语言、可支持大容量区块链底层平台的形式化验证等优点。

2018-12-14 10:18:25 1555

1555 偶数倍分频器的实现非常简单,只需要一个计数器进行计数就能实现。如需要N分频器(N为偶数),就可以由待分频的时钟触发计数器进行计数,当计数器从0计数到N/2-1时,将输出时钟进行翻转,并给计数器一个复位信号,以使下一个时钟开始从零计数。

2019-02-01 01:49:00 1425

1425

分频器是一种基本电路,通常用来对某个给定频率进行分频,得到所需的频率。整数分频器的实现非常简单,可采用标准的计数器,也可以采用可编逻辑器件设计实现。但在某些场合下,时钟源与所需的频率不成整数倍关系,此时可采用小数分频器进行分频。

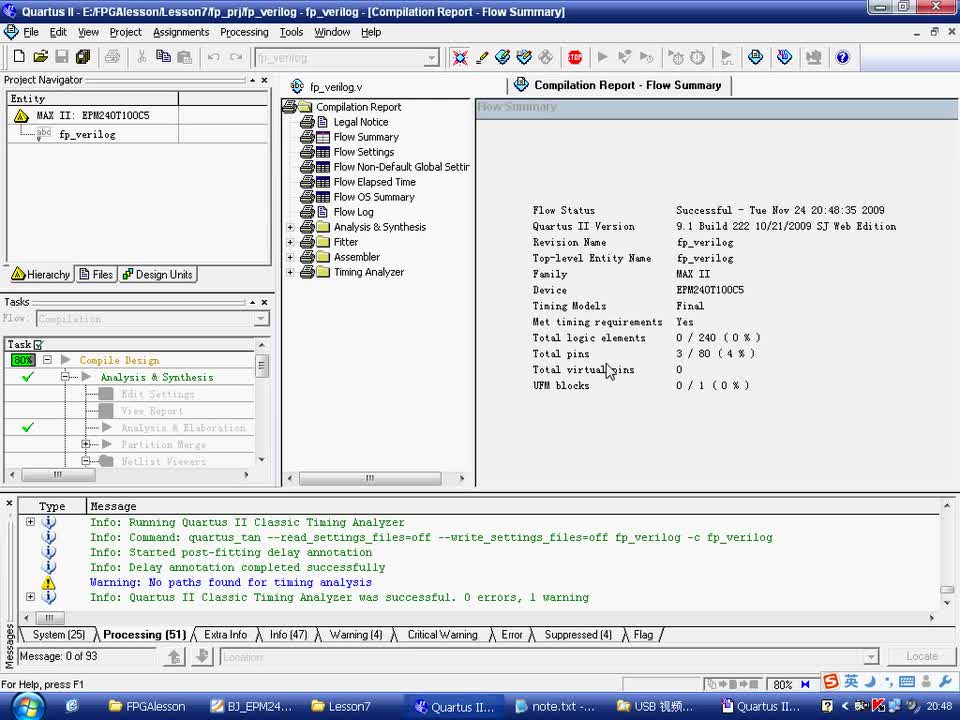

2019-11-20 07:05:00 7995

7995 论文分析了双模前置小数分频器的分频原理和电路实现。结合脉冲删除技术,提出了一种适于硬件电路实现的任意小数分频的设计方案 ,用 VerilogHDL语 言编程 ,在 QuartusII下对 此方案进 行 了仿 真 ,并用 Cyclone 系 列 的 EP1C12Q240C8芯 片来 实 现 。

2019-08-02 08:00:00 5

5 基于提升框架的小波变换方法,利用FPGA 可编程特性可实现多种小波变换。提升框架(LS :Lifting Scheme) 是由Sweldens 等人在近几年提出的一种小波变换方法,用它的框架结构能有效地计算DWT。对于较长的滤波器,LS 的操作次数比滤波器组的操作方式减少将近一半,更适合硬件实现。

2019-08-18 09:47:57 2456

2456

基于提升框架的小波变换方法,利用FPGA 可编程特性可实现多种小波变换。提升框架(LS :Lifting Scheme) 是由Sweldens 等人在近几年提出的一种小波变换方法,用它的框架结构能有

2019-08-25 11:01:31 6724

6724

从分频方式看可以分为两种,一种是主动分频(PassiveCrossover),或者叫电子分频,也可以叫外置分频、有源分频;另一种是被动分频 (ActiveCrossover),或者叫功率分频,也可以叫内置分频、无源分频。

2019-10-08 10:37:42 14230

14230

在数字系统设计中,根据不同的设计需要,经常会遇到偶数分频、奇数分频、半整数分频等,有的还要求等占空比。在基于cpld(复杂可编程逻辑器件)的数字系统设计中,很容易实现由计数器或其级联构成各种形式的偶数分频及非等占空比的奇数分频,但对等占空比的奇数分频及半整数分频的实现较为困难。

2020-06-26 09:36:00 1482

1482

通常情况下,时钟的分频在FPGA设计中占有重要的地位,在此就简单列出分频电路设计的思考思路。

2020-07-10 17:18:03 2928

2928 采用FPGA设计芯片技术对多进制数字通信技术的QPSK调制器实现进行了设计研究,将调制器中原有多种专用芯片的功能集成在一片大规模可编程逻辑器件FPGA芯片上,实现了高度集成化,小型化。实际研究仿真表明,该方案具有突出的灵活性和高效性,为设计者提供了多种可自由选择的设计方法和工具.

2020-07-22 17:51:13 15

15 据介绍,北京京剧院除在园博园阳光剧场上演《四郎探母》《龙凤呈祥》外,将对北京园实施整体打造,采用沉浸式演出、戏剧体验活动、展览等多种形式向观众展示京剧艺术魅力。

2020-10-25 09:53:11 2047

2047 被越来越多的大众熟知。 浅析气体检测技术的多种实现形式 气体传感器是一种将某种气体体积分数转化成对应电信号的转换器,探测头通过气体传感器对气体样品进行调理,通常包括滤除杂质和干扰气体、干燥或制冷处理仪表显示部分。按传感

2020-10-26 12:22:55 4798

4798

信息信号携带要通过链路传送的信息。信息信号呈现多种形式,但最常见的是音频信号、数字数据和视频信号。这些类型中的每一种都可以通过其信息带宽和输出信噪比(SNR)来表征,以确保其与链路另一端用户的通信。

2020-11-16 16:14:24 22701

22701 的设计来例系统地介绍了利用多种EDA工具进行 FPGA协同设计的实现原理及方法近年来,随着微电子学的迅速发展以及SoC(System on Chip ,片上系统) 技术在设计领域引起的深刻变革,EDA(Electornic Design Automatic ,电子设计自动化) 工具在系统设计中的地位愈发重要

2020-11-27 17:57:34 29

29 因为偶数分频器过于简单,所以我们从奇数分频器开始说起8 01 奇数分频器 假设我们要实现一个2N+1分频的分频器,就需要高电平占N+0.5个周期,低电平占N+0.5个周期,这样进行处理的最小

2021-03-12 15:44:54 7139

7139

简要介绍了CPLD/FPGA器件的特点和应用范围,并以分频比为2.5和1.5的分频器的设计为例,介绍了在MaxPlusII开发软件下,利用VHDL硬件描述语言以及原理图的输入方式来设计数字逻辑电路的过程和方法。该设计具有结构简单、实现方便、便于系统升级的特点。

2021-03-16 09:45:53 10

10 简要介绍了 CPLD/FPGA器件的特点和应用范围,并以分频比为2.5和15的分频器的设计为例,介绍了在 Maxplusll开发软件下,利用ⅤHDL硬件描述语言以及原理图的输入方式来设计数字逻辑电路的过程和方法。该设计具有结构简单、实现方便、便于系统升级的特点。

2021-03-22 16:52:15 5

5 简要介绍了CPLD/FPGA器件的特点和应用范围,并以分频比为25和15的分频器的设计为例,介绍了在 Maxplus开发软件下,利用VHDL硬件描述语言以及原理图的输入方式来设计数字逻辑电路的过程和方法该设计具有结构简单、实现方便、便于系统升级的特点。

2021-04-12 16:29:05 11

11 一种基于FPGA的分频器的实现说明。

2021-05-25 16:57:08 16

16 基于CPLD/FPGA的半整数分频器设计方案

2021-06-17 09:37:02 21

21 偶数倍分频器的实现非常简单,只需要一个计数器进行计数就能实现。如需要N分频器(N为偶数),就可以由待分频的时钟触发计数器进行计数,当计数器从0计数到N/2-1时,将输出时钟进行翻转,并给计数器一个复位信号,以使下一个时钟开始从零计数。

2022-11-21 09:41:24 1368

1368 FPGA分频器是一种常用于数字信号处理、通信系统、雷达系统等领域的电路,其作用是将信号分成多个频段。

2023-05-22 14:29:44 3076

3076

对于要求相位以及占空比严格的小数分频,建议采用模拟电路实现。而使用数字电路实现只能保证尽量均匀,在长时间内进行分频。

2023-06-05 17:20:51 2514

2514

板载晶振提供的时钟信号频率是固定的,不一定满足需求,因此需要对基准时钟进行分频。要得到更慢的时钟频率可以 分频 ,要得到更快的时钟频率可以 倍频 。我们有两种方式可以改变频率,一种是 锁相环 (PLL,后面章节会讲解),另一种是用 Verilog代码描述。

2023-06-23 16:52:00 4277

4277

基于FPGA的高频时钟的分频和分频设计

2023-08-16 11:42:47 1

1 如何具体实现输出信号的分频和倍频? 在现代电子系统中,信号分频和倍频是非常常见的技术。它们可以帮助电子设备在处理信号时具有更高的精度和准确性。下面我将详细介绍如何实现输出信号的分频和倍频。 一、分频

2023-10-31 10:33:21 4682

4682 分频器设计 一:分频器概念 板载时钟往往 是 有限个( 50MHZ/100MHZ/24MHZ/60MHZ… ),如果在设计中需要其他时钟时,板载时钟不满足时,需要对板载时钟进行分频 / 倍频,目的

2023-11-03 15:55:02 3266

3266

其实这个分频时钟切换很简单,根本不需要额外的切换电路。一个共用的计数器,加一点控制逻辑,就可以了,而且可以实现2到16任意整数分频率之间的无缝切换。

2023-12-14 15:28:56 1448

1448

电子发烧友App

电子发烧友App

评论