所谓“分频”,就是把输入信号的频率变成成倍数地低于输入频率的输出信号。数字电路中的分频器主要是分为两种:整数分频和小数分频。其中整数分频又分为偶分频和奇分频,首先从偶分频开始吧,入门先从简单的开始!

一、2^n的偶分频器设计

先来看最简单的最常见的一个例子——2分频。

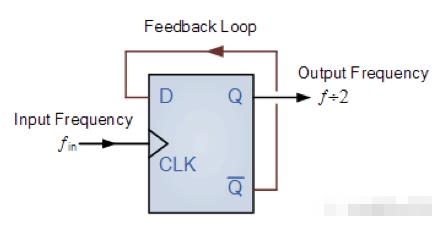

假设输入时钟clk是100MHz(T=10ns),要求得到一个50MHz的输出时钟clk_out,二分频波形应该如下图所示:

该波形的实际电路只需要一个D触发器便可以完成,将Q非的输出接到D端输入,便可以实现二分频电路,如下图所示。

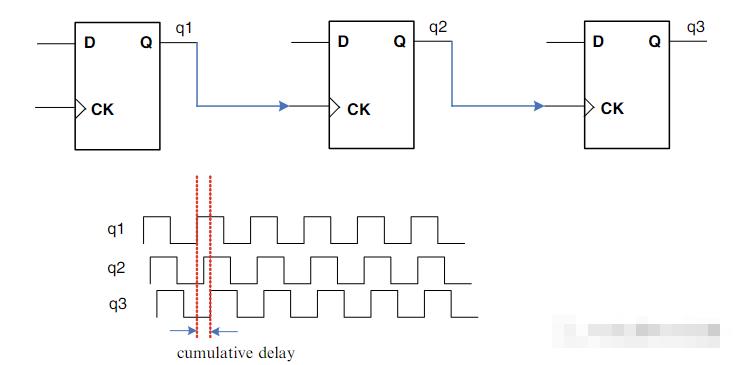

由此可以得出,所有2^n次方的偶分频(即二分频、四分频、八分频等等)都可以用触发器级联的方式得到,例如两个触发器级联就是四分频,三个触发器级联就是八分频,如此类推。

这种级联触发器的方式优缺点分析:

优点:1、能得到占空比为50%的波形;

2、所使用的的资源也比较少。

缺点: 唯一比较大的缺点就是触发器之间有一定的延时。因为驱动clk_out的触发器是由clk作为时钟的,那么这个触发器的Q端变化相比于clk有一个必不可少的clk-to-q延时,例如下图的q3与q1之间的差距就是clk-to-q延时造成的。

这个clk-to-q延时根据不同的工艺,数值会不同。这个clk-to-q的延时在做时钟树综合的时候是要考虑进去的。特别是如果你还期望clk和clk_out是同步的时钟,时钟边沿要对齐的话,在做clock tree的时候要给clk的tree加一些buffer来弥补这个clk-to-q。而如果你是用了好几个分频器级联产生更低频率,那么每一级的分频器都会贡献一个clk-to-q延时,那么你需要平衡时钟的时候就需要插入更多的buffer,这部分buffer又占面积,又耗功耗,甚至可能导致时钟无法平衡。所以这是需要大家在设计的时候考虑进去的。

二、任意偶数的分频器设计

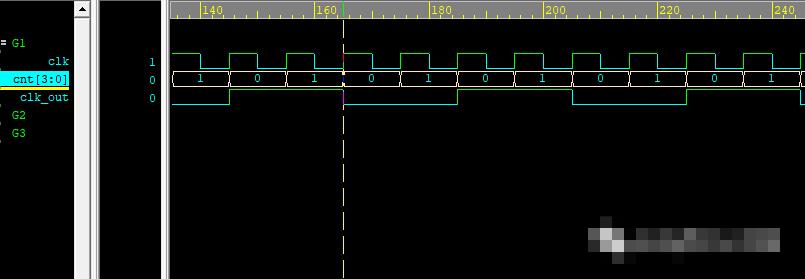

除了上面那种做法之外,对于任意偶数分频的设计还有一种传统的做法就是通过计数器的形式完成设计。例如要设计一个四分频,波形如图所示。cnt计数了DIV_NUM/2-1次之后取反,便可以得到任意偶数分频的波形,任意偶数分频通用代码如下所示。

`timescale 1ns/1ps

module CLK_DIV #(parameter DIV_NUM=4)(

input clk,

input rst_n,

output reg clk_out

);

reg[3:0] cnt;

always@(posedge clk or negedge rst_n)begin

if(!rst_n)

cnt <= 4'b0;

else begin

if(cnt == (DIV_NUM/2)-1)

cnt <= 4'b0;

else

cnt <= cnt + 1'b1;

end

end

always@(posedge clk or negedge rst_n)begin

if(!rst_n)

clk_out <= 1'b0;

else begin

if(cnt == (DIV_NUM/2)-1)

clk_out <= ~clk_out;

end

end

-

分频器

+关注

关注

43文章

536浏览量

52262 -

数字电路

+关注

关注

193文章

1648浏览量

83033 -

分频

+关注

关注

0文章

254浏览量

25277 -

小数分频

+关注

关注

0文章

7浏览量

6759

发布评论请先 登录

基于FPGA 的等占空比任意整数分频器的设计

分频器的作用是什么 半整数分频器原理图分析

基于复杂可编程逻辑器件和VHDL语言实现半整数分频器的设计

偶数分频、奇数分频、半整数分频和小数分频详解

偶数分频器的设计

偶数分频器的设计

评论