分频器设计

一:分频器概念

板载时钟往往是有限个(50MHZ/100MHZ/24MHZ/60MHZ…),如果在设计中需要其他时钟时,板载时钟不满足时,需要对板载时钟进行分频/倍频,目的是用于满足设计的需求。

分频:产生比板载时钟小的时钟。

倍频:产生比板载时钟大的时钟。

二:分频器的种类

对于分频电路来说,可以分为整数分频和小数分频。

整数分频:偶数分频和奇数分频。

小数分频:半整数分频和非半整数分频。

三:分频器的思想

采用计数器的思想实现。

例子1:模10计数器

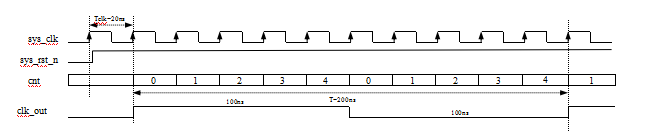

假设系统时钟sys_clk是50MHZ,对应的时钟周期Tclk=20ns,计数器每计数一次需要20ns,那么计数10次需要200ns。

1:整数分频:偶数分频(Duty:50%)

计数器计数10个持续时间为T=200ns,那么输出频率:

F=1/T=1/200ns=10^9/200HZ=5MHZ。

1MHZ=10^3KHZ=10^6HZ

通过模10计数器得到的频率为5MHZ,

占空比:高电平持续时间占整个周期比值。

50MHZ~5MHZ:10分频电路(Duty:50%)

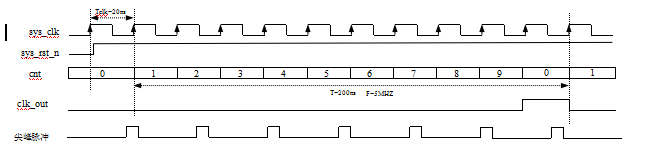

2:整数分频:偶数分频(输出时钟高电平持续系统时钟一个周期:尖峰脉冲信号)

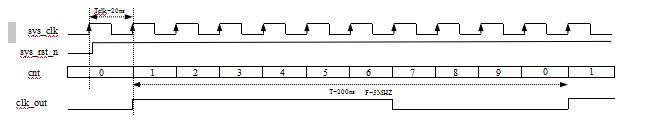

3:整数分频:偶数分频(Duty:60%)

根据上述偶数分频的方式,可以得出以下结论:

Fsys_clk= 50MHZTsys_clk= 1/Fsys_clk= 20ns

如果Fclk_out = 5MHZTclk_out = 1/ Fclk_out = 200ns

以系统时钟上升沿来时,使其计数器加1,换句话说计数器计数一次需要20ns,当满足200ns持续时间时,需要让计数器计数10次。

那么计数器计数最大值cnt_max=10。

推导公式:cnt_max(计数器计数最大值) = 200ns/20ns = Tclk_out/ Tsys_clk= Fsys_clk/ Fclk_out

4:整数分频:奇数分频

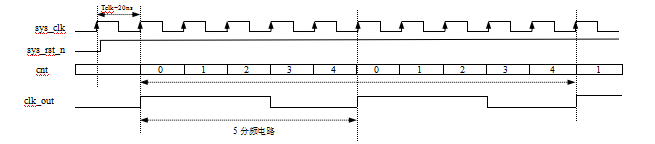

例子1:5分频电路(50MHZ--->10MHZ):Duty=3:2

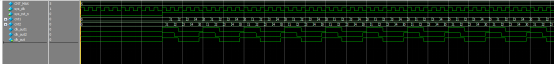

测试3:5分频电路(Duty=3:2)

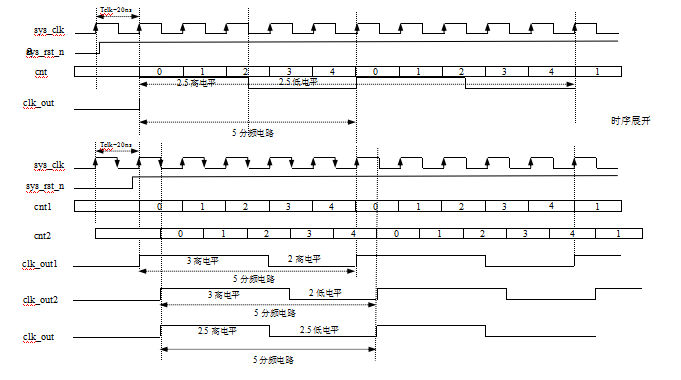

例子2:5分频电路(50MHZ--->10MHZ):Duty=1:1

首先需要设置两个计数器(0~4),第一个计数器以时钟上升沿计数,第二个计数器以时钟下降沿计数,都分别产生5分频电路,且占空比都为3:2,最后输出5分频电路占空比1:1就是由上述两个5分频电路相与得到的。

clk_out = clk_out1 & clk_out2;

如果5分频电路占空比是2:3时,最后输出5分频电路占空比1:1就是由上述两个5分频电路相或得到的。

clk_out = clk_out1 | clk_out2;

测试4:5分频电路(Duty=1:1)

测试5:5分频电路(Duty=1:1)

欢迎加入至芯科技FPGA微信学习交流群,这里有一群优秀的FPGA工程师、学生、老师、这里FPGA技术交流学习氛围浓厚、相互分享、相互帮助、叫上小伙伴一起加入吧!

点个在看你最好看

原文标题:FPGA学习-分频器设计

文章出处:【微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

-

FPGA

+关注

关注

1664文章

22509浏览量

639554

原文标题:FPGA学习-分频器设计

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

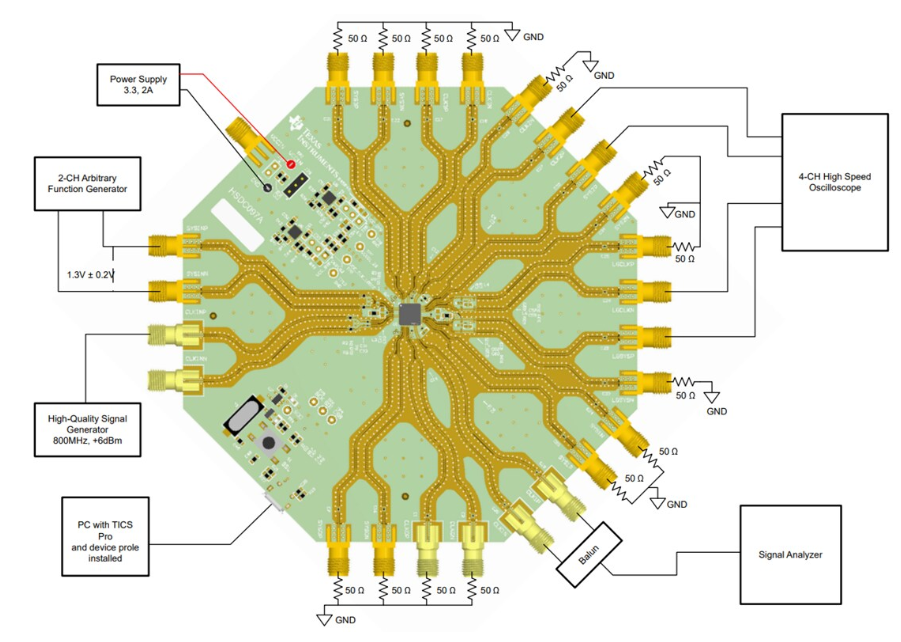

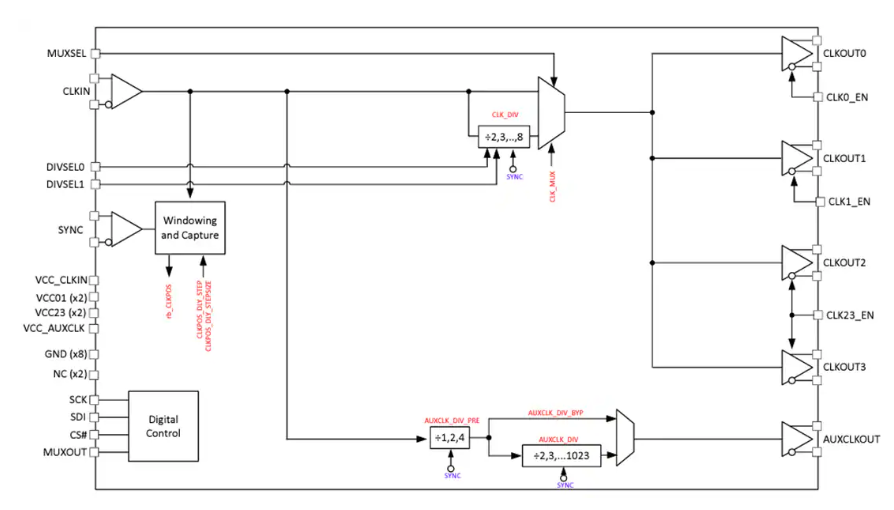

高频分频器/PLL 合成器 ADF4007:技术剖析与应用指南

SN74LS292和SN74LS294可编程分频器与数字定时器的技术解析

CDC5801A:低抖动时钟倍频器与分频器的卓越之选

LMX1214:高性能低噪声时钟缓冲及分频器的技术剖析

LMX1204:低噪声、高频JESD缓冲器/倍增器/分频器的卓越之选

LMX1214:高性能低噪声时钟缓冲与分频器的深度解析

LMX1205-EP:低噪声、高频JESD缓冲器/乘法器/分频器的深度解析

CDC5801A低抖动时钟倍频/分频器技术文档总结

CDCE706 可编程3-PLL时钟合成器/乘法器/分频器技术文档总结

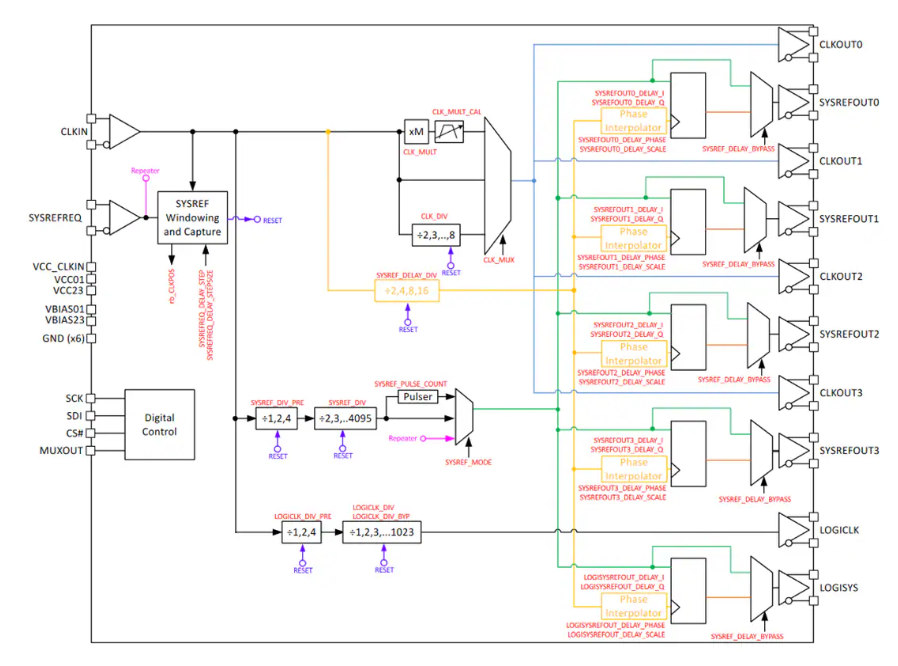

CDCLVD1213 1:4低附加抖动LVDS缓冲器带分频器 技术文档摘要

LMX1204高性能JESD缓冲器/乘法器/分频器技术解析与应用指南

LMX1204 低噪声高频 JESD 缓冲器/乘法器/分频器技术文档总结

LMX1214 低噪声高频缓冲器与分频器技术文档总结

LMX1204低噪声高频JESD缓冲器/倍频器/分频器技术解析

德州仪器LMX1214射频缓冲器与分频器技术解析

FPGA学习-分频器设计

FPGA学习-分频器设计

评论