在Vivado中,VIO(Virtual Input/Output)是一种用于调试和测试FPGA设计的IP核,它允许设计者通过JTAG接口实时读取和写入FPGA内部的寄存器,从而检查设计的运行状态并修改其行为。VIO IP核提供了一个简单易用的接口,使得用户可以轻松地与FPGA内部寄存器进行交互。

2025-06-09 09:32:06 3372

3372

基于FPGA和DDS的信号源设计

1 引言

直接数字频率合成DDS(Direct Digital Synthesizer)是基于奈奎斯特抽样定理理论和现代器件生产技术发展的一种新的频率合成技

2010-02-21 09:15:21 2106

2106

上篇主要是分享了Vivado编译软件远程调试的方法。杰克使用Vivado软件进行远程连接,主要是用于固化程序以及FPGA(PL端)的异常排查。而本篇主要内容是对使用Vitis软件远程调试的方法进行总结和分享。

2023-05-25 14:36:58 4231

4231

调用ISE中DDS的IP核产生1MHZ的正弦波给AD9361,硬件平台是K7的板子。但是通过chipsope抓取DDS产生的信号不对,I路波形和抓取的信号频谱在matlab中如下所示

2019-04-26 15:52:20

或单片机板,利用通过模式控制和频率字控制实时产生点频、扫频、ASK、FSK等各种形式的模拟信号。说明:+5V、+12V、-12V供电,输出双极性信号;同时提供FPGA和单片机控制程序源代码。实验DDS

2013-01-27 19:07:26

DDS的工作原理是什么?基于DSP Builder和DDS设计基于FPGA的DDS设计

2021-05-06 06:27:03

DDS专用芯片与基于FPGA的DDS的区别什么地方,优势在哪?关于DDS选型,DAC的位数影响DDS的什么性能,怎么选择合适DAC位数?AD995X系列与AD991x系列那个相噪性能杂散好?输出约20MHz的时钟,希望能推荐一款相噪和杂散性能好的芯片。

2018-08-06 09:13:36

jtag调试时,fpga能识别到器件,但是下载程序失败,针对这种情况,想问下各位:1、能识别到器件,说明fpga配置电路的哪些部分是正常的2、我描述的这种情况可能是由于什么原因导致的?

2014-05-04 10:50:29

用FPGA做DDS,请教这种由于输出信号的各位跳变时间有差异导致的毛刺怎么解决?

2017-05-17 09:57:54

FPGA实现直接数字频率合成(DDS)的原理、电路结构和优化方法介绍了利用现场可编程逻辑门阵列FPGA实现直接数字频率合成(DDS)的原理、电路结构和优化方法。重点介绍了DDS技术在FPGA中的实现

2012-08-11 18:10:11

下载配置与调试接口电路设计FPGA是SRAM型结构,本身并不能固化程序。因此FPGA需要一片Flash结构的配置芯片来存储逻辑配置信息,用于进行上电配置。以Altera公司的FPGA为例,配置芯片

2019-06-11 05:00:07

,可以尝试对IP软核进行优化。例如,可以调整参数配置、优化布局布线、修改代码等。

在调试过程中,可以利用FPGA开发工具提供的调试功能,如逻辑分析仪、波形查看器等,帮助定位问题和解决问题。

知识产权保护

2024-05-27 16:13:24

ISE软件,使用IP core调用DDS,产生正弦载波,使用调频200M时钟做为DDS输入,功能仿真没问题,但后仿真却不显示波形,只是一根红线,是不是频率过高啊,还是什么设置问题,请各位高人赐教,小弟初学FPGA

2013-03-20 20:37:32

。FPGA 配置部分很好,切换到 UVC 应用程序后,视频流也很好。 然而,在 UVC 应用程序中,UART 无法再发送调试信息。UART 调试在 FPGA 配置期间工作,并为 FPGA 配置过程打印

2024-05-28 07:26:22

调试硬件配置实用程序使您能够连接到在您的开发平台和PC之间提供接口的调试硬件单元。

提供了以下实用程序:

RVI配置IP实用程序使用此实用程序在调试硬件单元上配置IP地址。

这使您能够通过以太网访问

2023-08-12 06:54:13

Gowin® DDS IP 用户指南主要内容包括功能特点、端口描述、时序说明、配置调用、参考设计等。主要用于帮助用户快速了解 DDS IP 的产品特性、特点及使用方法。

2022-10-10 08:36:14

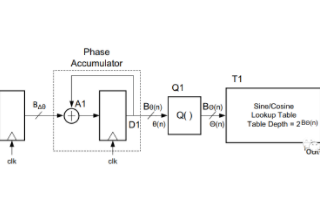

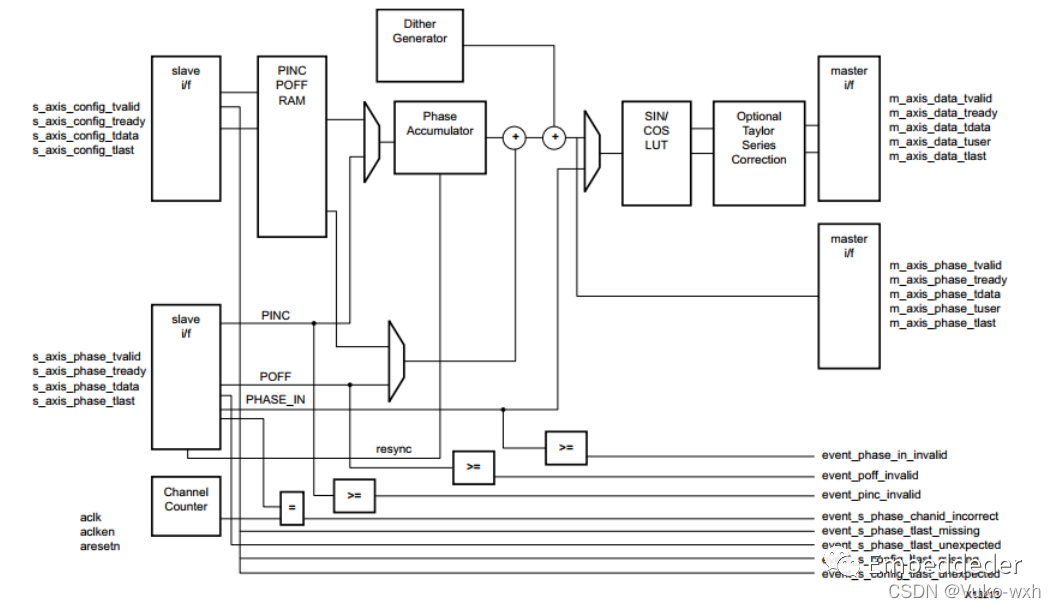

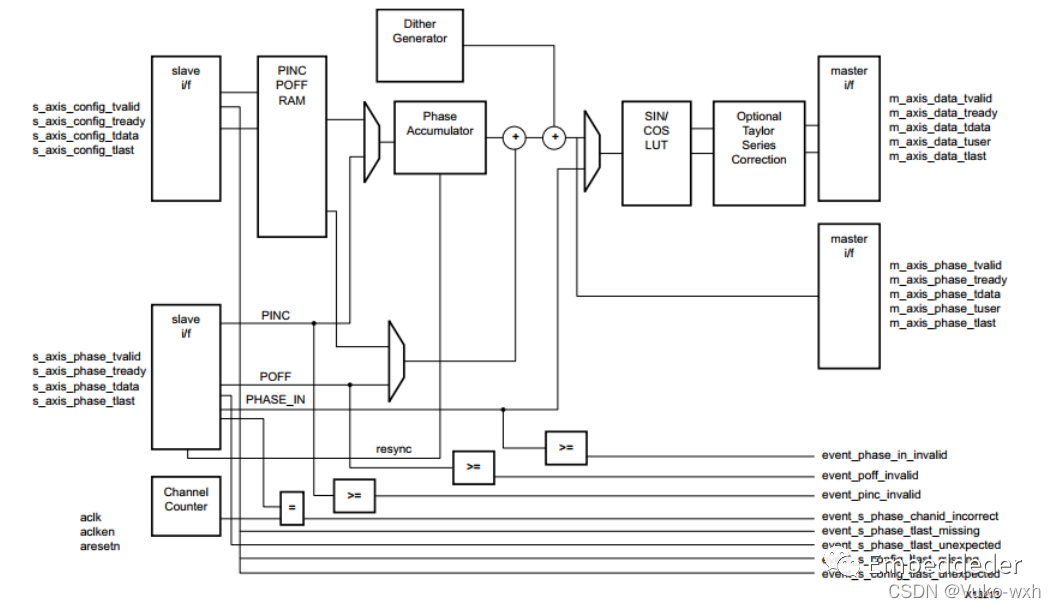

DDS(直接数字合成器) 是一款逻辑 IP 核,它可以提供适用于多种场景的正弦/余弦波形。DDS 主要由相位发生器和正弦/余弦查找表组成。 直接数字合成器也叫做 NCO(Numerically

2023-08-09 06:11:11

IP CORE NCO/DDS SC/SCM CONFIG

2023-03-30 12:01:19

IP CORE NCO/DDS LATTICEXP2 CONF

2023-03-30 12:01:19

IP CORE NCO/DDS LATTICEXM CONF

2023-03-30 12:01:19

; (4) DDS配置-3配置输出信号的频率为 0.5 MHz,结合前面的配置输出 0.5 MHz 的固定的正弦波,其他保持默认; 总结如下,可以看到位宽符合前文的计算。 2. 使用IP核搭建滤波系统

2020-01-18 22:05:50

发生器。函数信号发生器的实现方法通常是采用分立元件或单片专用集成芯片,但其频率不高,稳定性较差,且不易调试,开发和使用上都受到较大限制。随着可编程逻辑器件(FPGA)的不断发展,直接频率合成(DDS)技术

2012-05-12 23:01:54

这是数字信号处理系列的第一篇,以简单的数字混频为例,介绍在FPGA程序设计中很重要的二进制原码、补码;有符号数、无符号数的问题。本文不是像课本那样介绍这些基础概念,而是介绍很实际的设计方法。借助于

2021-07-23 06:38:10

信息显示在LCD液晶显示屏上。各硬件模块之间的协调工作通过嵌入式软核处理器NiosⅡ用编程实现控制。本设计所搭建的LCD12864控制器是通过编程实现的IP核。关键词:DDS;FPGA技术;顺序存储;NiosⅡ;IP核

2019-06-21 07:10:53

基于FPGA 的DDS 调频信号的研究与实现

2012-08-17 11:41:11

求一个基于FPGA的DDS信号发生器设计,最好有DA模块和相位累加器模块的代码。

2019-03-18 22:09:03

本帖最后由 kandy286 于 2013-11-8 00:33 编辑

刚学FPGA,用FPGA+DAC设计的DDS,已实现调频,调相功能。可是调幅该怎么控制呢?有种方案是改变DAC的参考电压

2013-11-08 00:32:04

本帖最后由 eehome 于 2013-1-5 09:51 编辑

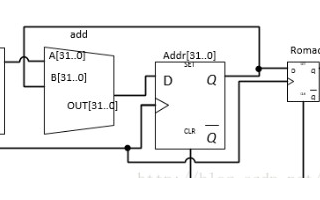

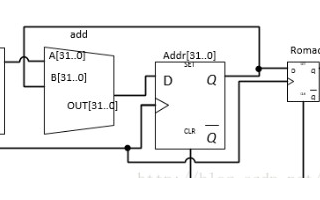

基于FPGA的DDS设计利 用现 场 可 编程 门 阵 列 设 计 并 实 现 直 接 数 字 频 率 合 成 器 结 合

2012-08-11 11:56:30

FPGA dds的全套设计资料分享给51hei的朋友们,有需要可以下载学习。 下面是DDS频率合成器视频教程内容截图(代码讲解): 部分源程序如下: `timescale 1ns / 1ps

2018-07-03 06:06:17

我毕业设计要做一个基于FPGA的IP核的DDS信号发生器,但是我不会用DDS的IP核,有没有好人能发我一份资料如何用IP核的呀。我的浏览器下载不了网站上的资料,所以只能发帖求帮忙了。

2015-03-10 11:46:40

一个DDS应用,我想使用Xilinx DDS IP内核生成任意波形,但我看到的是DDS只能生成正弦或余弦波形数据。你知道如何用其他数据替换正弦波形LUT吗?如果可以修改该LUT,它可以生成任意波形

2019-02-12 08:07:21

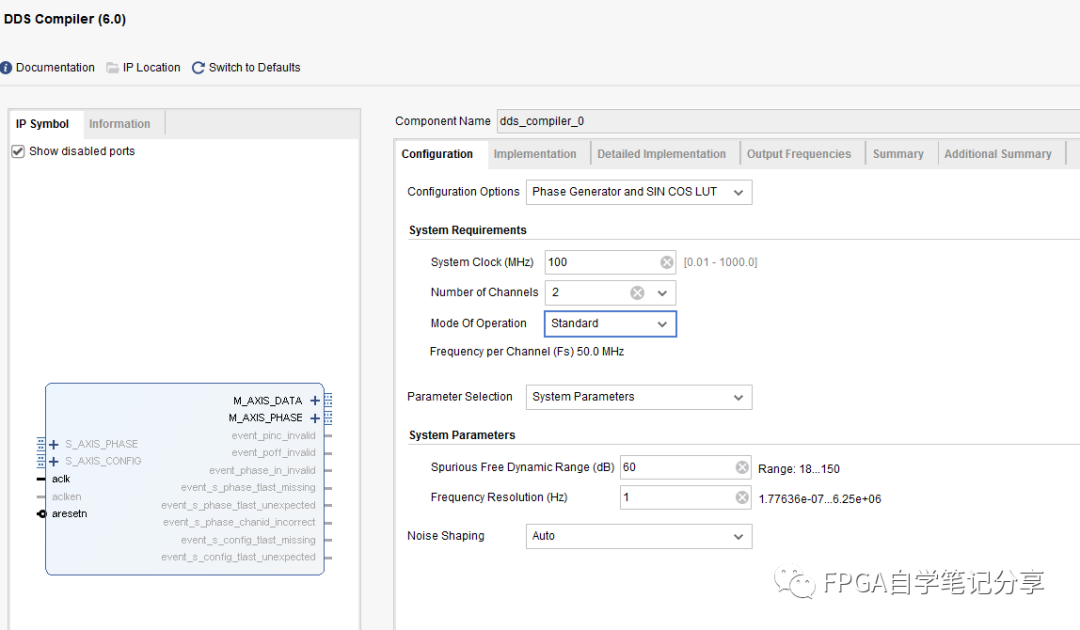

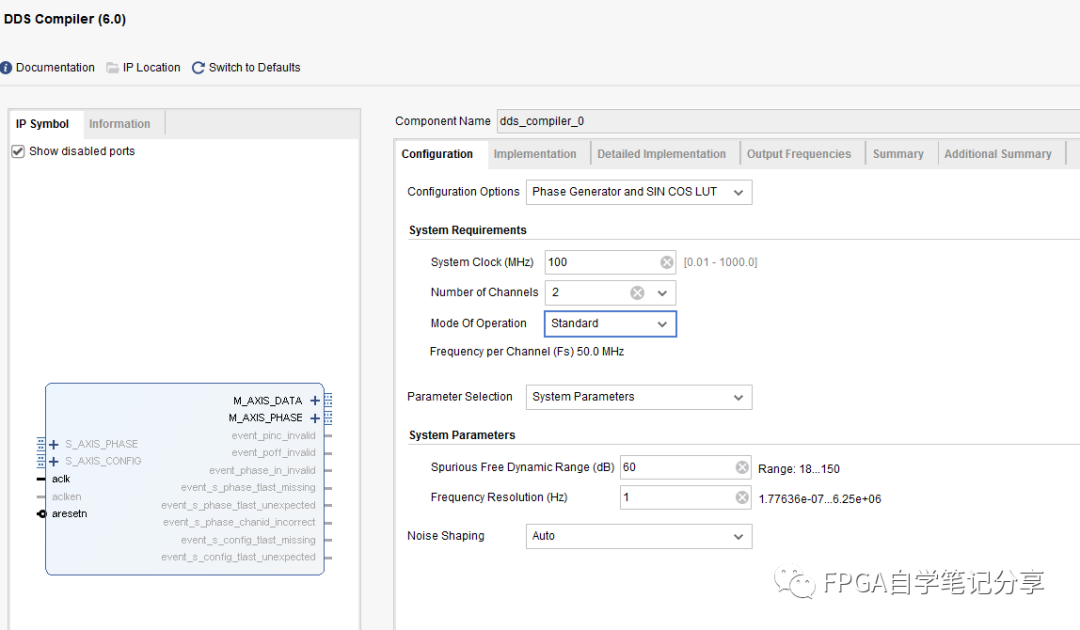

出现在 IP 存储库的列表中时双击它,将弹出一个对话框。单击“Customize IP”按钮,将出现 DDS 编译器的配置窗口。在如上所示的第一个选项卡中,为了我们的目的,保留所有默认设置。在第二个选项卡

2023-02-08 15:39:30

DDS的工作原理和基本结构基于FPGA的DDS信号发生器的设计如何建立顶层模块?

2021-04-09 06:46:42

ACEX 1K具有什么特点DDS电路工作原理是什么如何利用FPGA设计DDS电路?

2021-04-30 06:49:37

介绍了利用现场可编程逻辑门阵列FPGA实现直接数字频率合成(DDS)的原理、电路结构和优化方法。重点介绍了DDS技术在FPGA中的实现方法,给出了采用ALTERA公司的ACEX系列FPGA芯片EP1K30TC进行直接数字频率合成的VHDL源程序。

2021-04-30 06:29:00

针对数据处理速度越来越高的要求,本文提出了基于FPGA+DDS的控制设计,能够快速实现复杂数字系统的功能。

2021-04-30 06:17:49

本文在讨论DDS的基础上,介绍利用FPGA设计的基于DDS的信号发生器。

2021-05-06 09:54:10

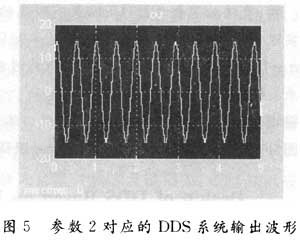

介绍了DDS的发展历史及其两种实现方法的特点,论述了DDS的基本原理,并提出一种基于FPGA的DDS信号发生器的设计方法,使DDS信号发生器具有调频、调相的功能,最后对其性能进行了分析。实验表明该系统具有设计合理、可靠性高、结构简单等特点,具有很好的实用价值。

2021-05-11 06:58:58

大家好,我有一个问题。当我设计DDS IP CORE时,我不知道如何创建不同振幅的sin波。通常我可以创建相同的振幅但不同频率的sin波要叠加。但是,我不知道知道如何实现幅度控制.SFDR的功能是什么?谢谢!

2020-05-13 08:58:43

的MSB来使用Xilinx DDS IP内核? DDS ip是否允许控制生成波形的相移?谢谢您的回答最好的祝福以上来自于谷歌翻译以下为原文Hello,i need to implement an IP

2019-04-04 14:20:38

DDS AD9959应用电路和配置源程序

AD9959是一款有四个DDS通道,最高达500M SPS的数字频率合成芯片。

常用电路接法:

2008-03-12 17:33:23 288

288 FPGA调试工具chipscope,学习与使用FPGA必用的工具。。

2009-03-23 09:45:00 86

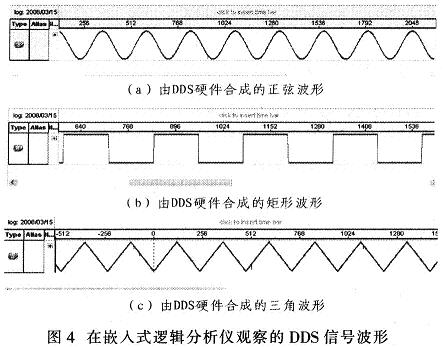

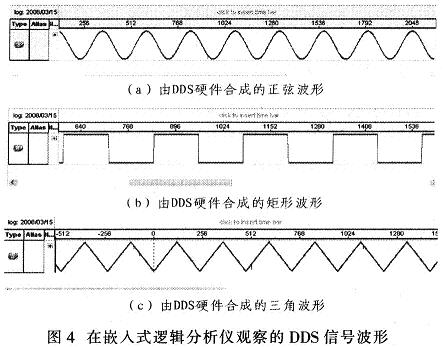

86 本文从DDS 基本原理出发,利用FPGA 来实现DDS 调频信号的产生,重点介绍了其原理和电路设计,并给出了FPGA 设计的仿真和实验,实验结果表明该设计是行之有效的。直接数字频率

2009-06-26 17:29:09 72

72 基于FPGA的DDS信号源设计与实现

利用DDS和 FPGA 技术设计一种信号发生器.介绍了该信号发生器的工作原理、 设计思路及实现方法.在 FPGA 器件上实现了基于 DDS技

2010-02-11 08:48:05 228

228 基于DSP Builder的DDS设计及其FPGA实现

直接数字合成器,是采用数字技术的一种新型频率合成技术,他通过控制频率、相位增量的步长,产生各种不同频率的信号。他具

2010-01-14 09:43:55 1753

1753

FPGA硬件系统的调试方法

在调试FPGA电路时要遵循一定的原则和技巧,才能减少调试时间,避免误操作损坏电路。一般情况下,可以参考以下步骤进行

2010-02-08 14:44:42 3102

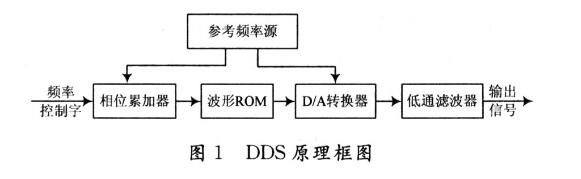

3102 DDS是什么意思,DDS结构,DDS原理是什么

什么叫DDS

直接数字式频率合成器DDS(Direct Digital Synthesizer),实际

2010-03-08 16:56:38 47659

47659 采用VC++程序的FPGA重配置设计方案利用现场可编程逻辑器件FPGA的多次可编程配置特点,通过重新下载存储于存储器的不同系统数据

2010-04-14 15:14:57 767

767

本站提供DDS 调试心得的资料,希望能够帮你学习。

2011-05-25 15:53:06 43

43 文中提出一种基于FPGA的DDS信号发生器。信号发生电路采用直接数字频率合成技术,即DDS(Direct Digital Frequency Synth-esis)。它是以全数字技术,从相位概念出发,直接合成所需波形的一种新的

2011-07-16 10:24:22 2342

2342

基于FPGA、PCI9054、SDRAM和DDS设计了用于某遥测信号模拟源的专用板卡。PCI9054实现与上位机的数据交互,FPGA实现PCI本地接口转换、数据接收发送控制及DDS芯片的配置。通过WDM驱动程序设计及

2012-03-01 15:37:30 83

83 以Altera公司的Quartus Ⅱ 7.2作为开发工具,研究了基于FPGA的DDS IP核设计,并给出基于Signal Tap II嵌入式逻辑分析仪的仿真测试结果。将设计的DDS IP核封装成为SOPC Builder自定义的组件,结合

2012-04-05 16:04:34 85

85 首先介绍了采用直接数字频率合成(DDS)技术的正弦信号发生器的基本原理和采用FPGA实现DDS信号发生器的基本方法,然后结合DDS的原理分析了采用DDS方法实现的正弦信号发生器的优缺点

2012-11-26 16:23:32 49

49 3 FPGA设计流程 完整的FPGA 设计流程包括逻辑电路设计输入、功能仿真、综合及时序分析、实现、加载配置、调试。FPGA 配置就是将特定的应用程序设计按FPGA设计流程转化为数据位流加载

2013-01-16 11:52:22 16

16 This is a VHDL implementation of a UDP/IP core that can be connected to the input and output ports

2015-11-12 14:45:16 8

8 利用现场可编程门阵列(FPGA)设计并实现直接数字频率合成器(DDS)。结合DDS 的结构和原理,给出系统设计方法,并推导得到参考频率与输出频率间的关系。DDS 具有高稳定度,高分辨率和高转换速度,同时利用Altera 公司FPGA 内的Nios 软核设置和显示输出频率,方便且集成度高。

2016-04-01 16:14:19 28

28 基于FPGA的DDS信号源研究与设计_南楠.pdf 关于干扰的,不知道。

2016-05-16 17:15:25 4

4 Xilinx FPGA工程例子源码:基于Spartan3E的串口调试和检测程序

2016-06-07 15:07:45 6

6 在FPGA中嵌入cpu软核,让C语言程序在里面运行。这就涉及到FPGA配置文件的引导,如果C语言程序太大,需要在DDR里面运行的话也涉及到应用程序的引导的问题。我刚接触到xinlinx的spartan3e

2018-02-27 15:33:29 5

5 本文首先介绍了DDS的基本原理和特点,其次介绍了DDS芯片AD9854的概念,最后详细介绍了STM32的AD9854 DDS模块调试经验总结。

2018-05-16 16:43:13 20058

20058

主设备可以为控制器,CPLD等等。当然FPGA也支持通过JTAG的方式进行程序下载,同时也可以通过JTAG进行FPGA时序抓取。 FPGA的配置过程包括以下几方面:复位,程序加载,初始化,最后进入用户

2018-11-18 18:05:01 831

831 ADI公司在Embedded World 2015上展示了采用Zynq SDR套件的DDS HLS IP

2018-11-30 06:44:00 3814

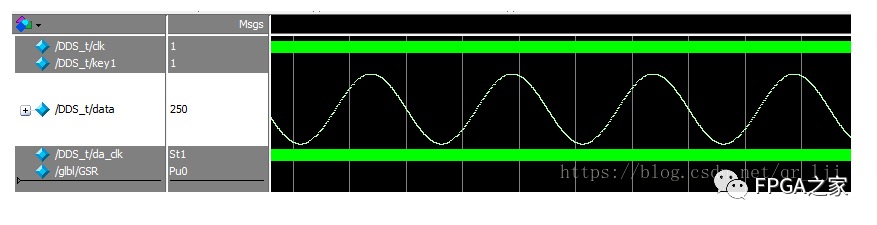

3814 在FPGA上设计一个DDS模块,在DE0 开发板上运行,在FPGA芯片内部合成出数字波形即可。

2018-12-08 09:18:25 2497

2497

主要有AD8950.AD8951等的原理图,介绍,PCB,调试图片和软件介绍

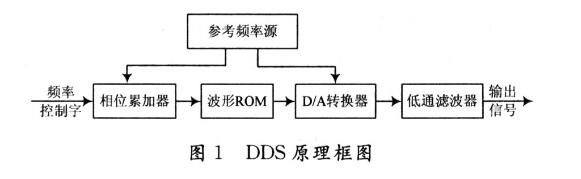

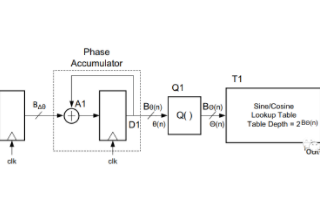

DDS的基本大批量是利用采样定量,通过查表法产生波形。DDS的结构有很多种,其基本的电路原理可用图1来表示。

2019-03-04 08:00:00 9

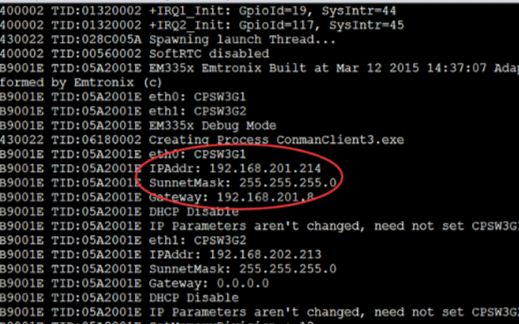

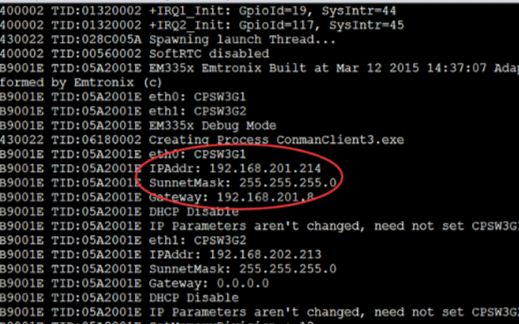

9 为了提高系统效率,WEC2013不再支持基于USB连接的Active sync功能,只能通过网络调试应用程序,获取主板的IP地址是调试程序的第一步。 以预装了正版WEC2013操作系统的英创工控主板

2020-02-03 10:21:14 2355

2355

对于FPGA调试,主要以Intel FPGA为例,在win10 Quartus ii 17.0环境下进行仿真和调试,开发板类型EP4CE15F17。

2020-03-29 11:37:00 1630

1630 FPGA概述FPGA调试介绍调试挑战设计流程概述■FPGA调试方法概述嵌入式逻辑分析仪外部测试设备■使用 FPGAVIEW改善外部测试设备方法■FPGA中高速O的信号完整性测试和分析

2020-09-22 17:43:21 12

12 本文档的主要内容详细介绍的是DDS的FPGA实现电路原理图免费下载。

2020-10-22 12:07:17 29

29 在线调试也称作板级调试,它是将工程下载到FPGA芯片上后分析代码运行的情况。

2020-11-01 10:00:49 5441

5441

本文讨论了基于FPGA芯片的直接数字频率合成器(DDS)的设计方法。因为DDS 的实现依赖于高速、高性能的数字器件,使用现场可编程器件FPGA,利用其高速、高性能及可重构性的特性,就能根据需要方便地实现各种不同频率的信号输出。

2021-03-02 17:11:32 36

36 本次使用Vivado调用DDS的IP进行仿真,并尝试多种配置方式的区别,设计单通道信号发生器(固定频率)、Verilog查表法实现DDS、AM调制解调、DSB调制解调、可编程控制的信号发生器(调频调相)。

2021-04-27 16:33:06 8131

8131

vivado提供了DDS IP核可以输出正余弦波形,配置方法如下

2021-04-27 15:52:10 12327

12327

本次项目我们主要是为了讲解DDS,所以我们使用了混频这个小项目来讲解。DDS自己手写是比较简单且灵活,但是Xilinx给我们提供了相应的IP核,那么这次我们将直接讲解使用IP来产生不同频率的正弦波。

2021-04-27 16:00:05 7980

7980

基于FPGA的DDS设计方案1 DDS技术简介随着电子技术的不断发展,传统的频率合成技术逐渐不能满足人们对于频率转换速度、频率分辨率等方面的追求,直接数字频率合成技术应运而生。 直接数字频率合成技术

2021-06-10 17:54:47 3354

3354

利用DDS IP实现线性调频信号 1 DDS技术简介随着电子技术的不断发展,传统的频率合成技术逐渐不能满足人们对于频率转换速度、频率分辨率等方面的追求,直接数字频率合成技术应运而生。 直接数字

2021-07-02 10:27:58 5285

5285

利用DDS IP实现线性调频信号1 DDS技术简介随着电子技术的不断发展,传统的频率合成技术逐渐不能满足人们对于频率转换速度、频率分辨率等方面的追求,直接数字频率合成技术应运而生。

2021-07-02 10:27:28 8770

8770

基于FPGA和DAC设计的dds发生器(普德新星电源技术有限公司的LoGo)-该文档为基于FPGA和DAC设计的dds发生器总结文档,是一份很不错的参考资料,具有较高参考价值,感兴趣的可以下载看看………………

2021-09-16 12:09:10 42

42 DDS基于FPGA的DDSSPI系统结构功能实现:在SPI接口下挂接上DDS模块,通过单片机向FPGA发送频率字实现任意频率正弦波的波形,并通过DAC模块输出单片机部分通过按键输入待产生的信号频率

2021-12-01 17:36:17 10

10 STM8S103单片机使用IAR进行程序开发和调试1.在程序调试没有错误后 选择 “Options” 进行配置2.选择“Debugger”选项“ST-LINK”3.选择其中一个进行在线调试注:两种调试模式的区别

2021-12-03 10:21:02 16

16 下载硬件配置数据。启动程序中的错误可能会导致CPU停机。您可以使用模块信息工具来诊断和消除编程错误。 通过执行用户程序来检查系统的功能,可以在组织块OB1中逐个调用各个逻辑块,逐步调试程序。对程序的更改应在调试期间保存。调试后,保存调试

2022-01-04 14:08:41 5049

5049 使用Jtag Master调试FPGA程序时用到tcl语言,通过编写tcl脚本,可以实现对FPGA的读写,为调试FPGA程序带来极大的便利,下面对FPGA调试过程中常用的tcl语法进行介绍,并通过tcl读FIFO的例子,说明tcl在实际工程中的应用。

2022-02-19 19:44:34 3645

3645 对FPGA进行上板调试时,使用最多的是SignalTap,但SignalTap主要用来抓取信号时序,当需要发送信号到FPGA时,Jtag Master可以发挥很好的作用,可以通过Jtag Master对FPGA进行读写测试

2022-02-16 16:21:36 3151

3151

电子发烧友网站提供《Gowin DDS IP用户指南.pdf》资料免费下载

2022-09-16 14:32:10 0

0 电子发烧友网站提供《关于Ultra96的Xilinx DDS编译器IP教程.zip》资料免费下载

2022-12-13 10:17:40 1

1 本文是本系列的第六篇,本文主要介绍FPGA常用运算模块-DDS信号发生器,xilinx提供了相关的IP以便于用户进行开发使用。

2023-05-24 10:37:18 7398

7398

本文对DDS以及基于DDS的SOA系统的测试策略进行探讨,并介绍DDS测试方案。

2022-08-04 14:52:04 3569

3569

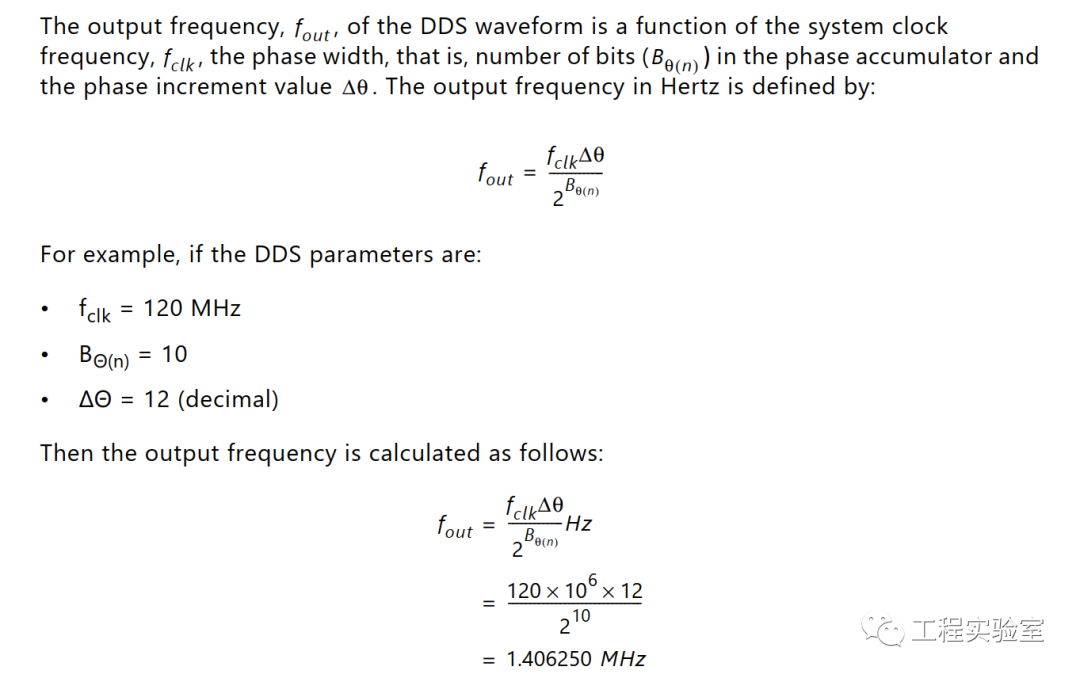

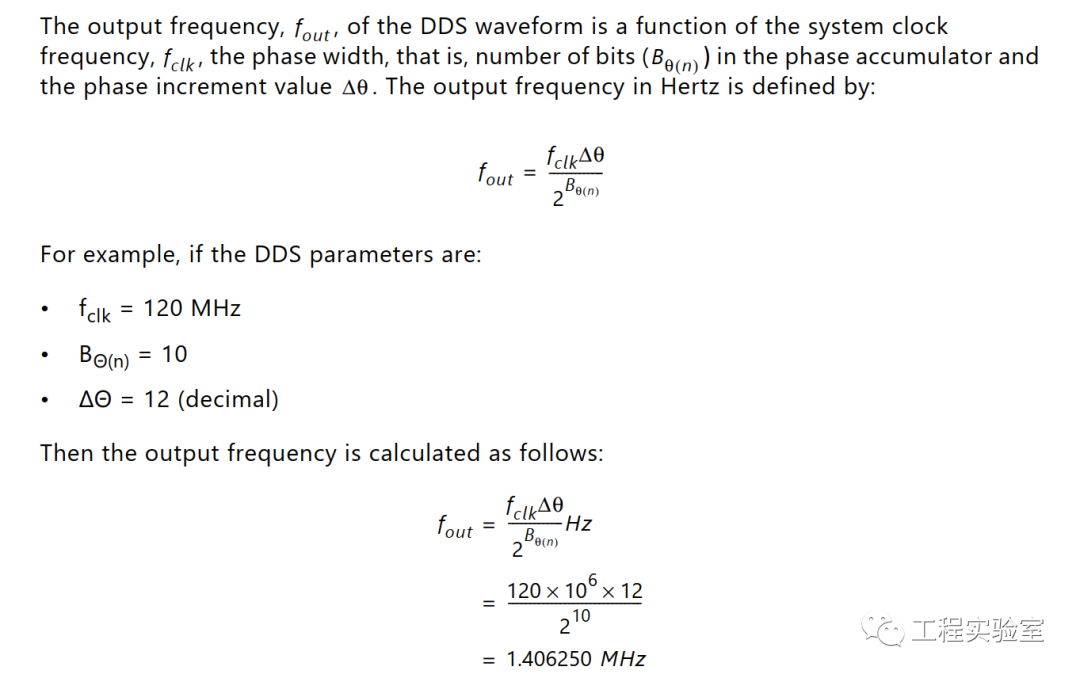

DDS(Direct Digital Frequency Synthesizer) 直接数字频率合成器,本文主要介绍如何调用Xilinx的DDS IP核生成某一频率的Sin和Cos信号。

2023-07-24 11:23:29 8502

8502

DDS,Director Digital Synthesis,直接频率合成技术,是指通过固定频率的参考时钟(采样时钟)生成指定频率的正余弦信号。采用FPGA配合DAC芯片,可以实现频率、相位可调的模拟信号用于一些特定的领域。

2023-08-22 16:30:24 9015

9015

之前的文章对dds ip 的结构、精度、参数、接口进行了详细的说明,本文通过例化仿真对该IP的实际使用进行演示。本文例化固定模式和可配置模式两种模式分别例化ip并仿真,说明该IP的应用。

2023-09-07 18:31:06 4698

4698

电子发烧友网站提供《基于FPGA 的DDS正弦信号发生器的设计和实现.pdf》资料免费下载

2024-03-24 09:34:50 10

10 用RAM实现一个DDS,从原理上来说很简单,在实际使用的时候,可能没有直接使用官方提供的IP核来的方便。这个博客就记录一下,最近使用到的这个DDS IP。

2024-10-25 16:54:11 5872

5872

电子发烧友App

电子发烧友App

评论