在Vivado中,VIO(Virtual Input/Output)是一种用于调试和测试FPGA设计的IP核,它允许设计者通过JTAG接口实时读取和写入FPGA内部的寄存器,从而检查设计的运行状态并修改其行为。VIO IP核提供了一个简单易用的接口,使得用户可以轻松地与FPGA内部寄存器进行交互。

在Vivado中,ILA(Integrated Logic Analyzer)是一种强大的在系统调试工具,它可以捕获并分析FPGA内部的信号。使用ILA时,需要确保ILA的时钟信号与被观察信号的时钟域一致,以避免由于时钟域不匹配导致的数据捕获错误。此外,ILA的探针数量和数据深度应根据实际需求进行配置,以平衡资源消耗和调试需求。

VIO与ILA基本上就是我们在板调试FPGA的主要工具,在vivado中均有相应的IP core,具体的步骤如下:

1. vivado中打开IP Catalog

2. 搜索ila,在Debug&Verification 中选择ILA(Inegrated Logic Analyzer)

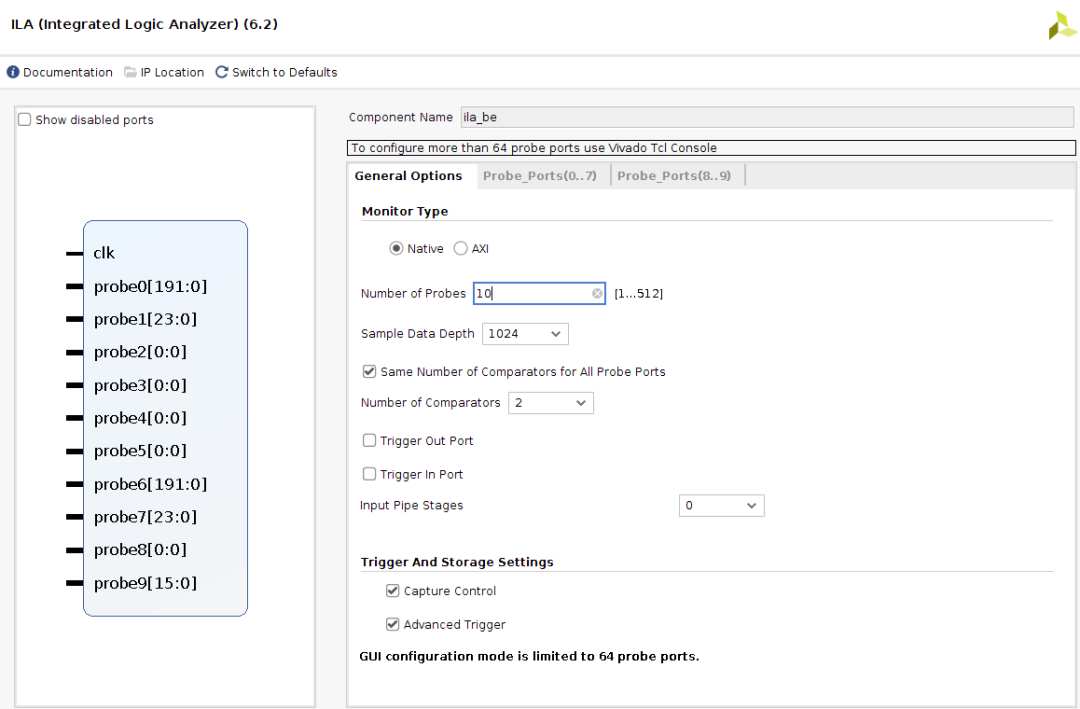

3. 右键Customize IP ,设置参数,多数的选择可以采用默认的选择。

这里对ILA的特殊参数做一点说明:

Capture Control:即可以选择一个条件信号,仅条件信号满足设置要求时,才会进行采样或者触发操作,用于我们在需要某些信号进行触发时勾选;

Advanced Trigger:支持高级触发功能,它允许用户通过编写触发状态机(Trigger State Machine,TSM)来定义更复杂的触发条件。TSM是一个简单的脚本语言,用于定义触发状态机。可以在ILA的属性窗口中编写TSM代码,或者创建一个后缀为.tsm的文件来编写TSM脚本,实现相应的触发设置,可以利用ILA的高级触发功能来更精确地捕获和分析FPGA设计中的信号。

Setup Debug:由于这种Debug方式是将Debug信息写入XDC文件的方式,vivado提示我们需要更新XDC文件,可以选择覆盖overwite现有的XDC文件,该选项并不会删除我们现有的XDC文件约束,而是将Debug信息添加在XDC约束后面,实际操作中会发现,并不是完全将新的ILA约束信息,添加在原有XDC文件之后,而是以vivado自己的方式,重新写我们的约束文件,即如果我们有重要的约束信息,建议新增XDC文件save constraints as,这样可以保障原有XDC信息不被修改。

ILA其他注意事项

(1)ILA核的采样深度不宜过大,采样深度尽量设置在1024bit以内:在每个采样时钟下,ILA都会将捕获到的探针信号的值送入RAM中,由于RAM的存储空间是有限的,其数值越大,消耗的RAM资源也越多,从而对设计性能产生不利影响。

(2)ILA核的采样宽度不宜过大,随探针宽度增加,对资源利用率和时序的影响也会增大。

(3)请确保输入到ILA核的时钟与抓取的信号是同步关系,否则在设计编程到器件中时会产生时序问题并导致通信失败。

(4)抓信号的时钟必须为全局时钟网络。

(5)请尽量确保ILA核选择的时钟均为自由运行的时钟(常开稳定时钟),否则可能造成在器件上加载版本时无法与调试核通信。

(6)请尽量确保FPGA JTAG时钟比Debug Hub时钟慢2.5倍,否则可能出现运行后报错或者运行后不报错但不显示任何结果的情况,ug908。

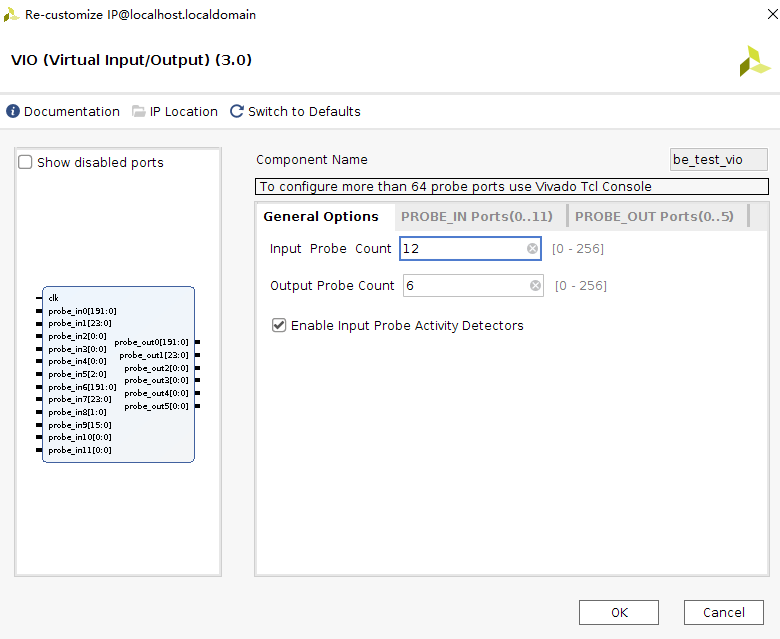

VIO的配置界面中,设置Input Probe Count和Output Probe Count,即输入和输出探头的数量。

Enable Input Probe Activity Detectors:当输入信号发生变化时,Vivado会显示一个活动指示,帮助追踪信号的变化。启用Input Probe Activity Detectors后,你可以在ILA调试波形中看到哪些信号是活动的,这有助于快速定位问题。

-

FPGA

+关注

关注

1664文章

22508浏览量

639408 -

寄存器

+关注

关注

31文章

5620浏览量

130440 -

调试工具

+关注

关注

1文章

59浏览量

13033 -

Vivado

+关注

关注

19文章

860浏览量

71410

原文标题:FPGA上板调试方式总结----VIO/ILA

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

XILINX FPGA Debug with VIO and TCL

玩转Zynq连载5——基于Vivado的在线板级调试概述

chipcope pro核心生成并在设计中使用它们

关于ILA核心使用的一些事情?

Arty是否有可能不支持ILA调试?

Xilinx FPGA ChipScope的ICON/ILA/VIO核使用

FPGA开发要懂得使用硬件分析仪调试——ILA

Vivado调试ILA debug结果也许不对

Vivado之ILA详解

ILA工作原理 ILA使用方法与注意

Vivado之VIO原理及应用

FPGA调试方式之VIO/ILA的使用

FPGA调试方式之VIO/ILA的使用

评论