声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

赛灵思

+关注

关注

33文章

1798浏览量

133682 -

Zynq

+关注

关注

10文章

633浏览量

49590

发布评论请先 登录

相关推荐

热点推荐

AMD Zynq UltraScale+ RFSoC评估套件调试检查表

本篇文章包含一份调试检查表,它是对 AMD Zynq UltraScale+ RFSoC 评估套件(ZCU208、ZCU216、ZCU111 和 ZCU670)上评估板相关问题进行故障排除的重要资源。

请教:6G 确定性通信原型验证,FPGA+SDR 方案该怎么搭?

时间同步

面向卫星 / 工业互联网场景

想请教几个实际问题:

做这类 确定性调度原型 ,用 FPGA + SDR 是不是最稳妥的路线?

基带处理、时间同步、调度仲裁,哪部分适合放FPGA实现?

SDR

发表于 04-11 10:24

HLS设计中的BRAM使用优势

HLS设计的IP可以直接使用BRAM,但Block Memory Generator和AXI BRAM Controller仍然在FPGA设计中发挥着重要作用。

AMD Vivado IP integrator的基本功能特性

我们还将带您了解在 AMD Zynq UltraScale+ MPSoC 开发板与 AMD Versal 自适应 SoC 开发板上使用 IP integrator 时,两种设计流程之间存在的差异。

STM32H743 移植 Micro-XRCE-DDS 时,在调用 gethostbyname() 时出现异常怎么解决?

packagesMicro-XRCE-DDS-Client-latestsrccprofiletransportipudpudp_transport_external.c

uxr_init_udp_platform() 函数调用

host = (struct hostent

发表于 09-22 06:54

DDS-TSN 到底是如何实现的?

概述1.1TSN与DDS的独立优势与局限随着智能网联汽车和车载网络架构的不断迭代,车载网络对实时性、确定性和高效数据分发的需求日益严苛。TSN和DDS的结合为车载以太网提供了确定性实时通信(TSN

如何在Unified IDE中创建视觉库HLS组件

Vivado IP 流程(Vitis Unified),在这篇 AMD Vitis HLS 系列 3 中,我们将介绍如何使用 Unified IDE 创建 HLS 组件。这里采用“自

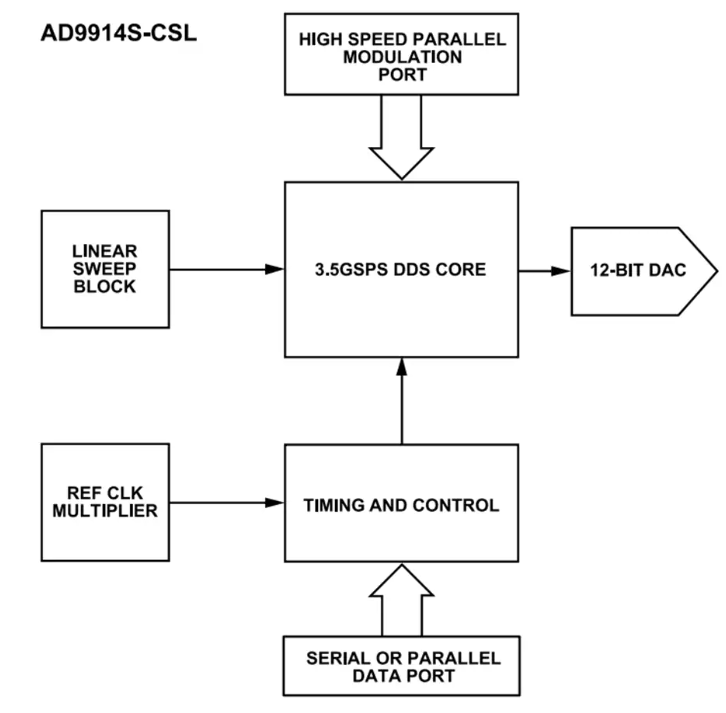

Analog Devices Inc. AD9914S直接数字合成 (DDS)数据手册

Analog Devices Inc. AD9914S直接数字合成 (DDS) 采用12位数模转换器 (DAC)。AD9914S采用先进的DDS技术以及内部高速、高性能DAC,形成数字

使用AMD Vitis Unified IDE创建HLS组件

这篇文章在开发者分享|AMD Vitis HLS 系列 1 - AMD Vivado IP 流程(Vitis 传统 IDE) 的基础上撰写,但使用的是 AMD Vitis Unified IDE,而不是之前传统版本的 Vitis HLS

如何使用AMD Vitis HLS创建HLS IP

本文逐步演示了如何使用 AMD Vitis HLS 来创建一个 HLS IP,通过 AXI4 接口从存储器读取数据、执行简单的数学运算,然后将数据写回存储器。接着会在 AMD Vivado Design Suite 设计中使用此

服务与数据的双螺旋:从SOME/IP到DDS看汽车电子架构的进化之路

底层通信技术的演进始终是由应用需求的不断变化所驱动的。正如“进化论”所强调的,“适者生存”才是核心:并不存在放之四海而皆准的“最优”技术,只有在特定场景下最合适的解决方案。对于SOME/IP和DDS,很多人习惯于直接问“孰优孰劣”,但如果脱离具体的应用场景去讨论优劣,往往

采用Zynq SDR套件的DDS HLS IP

采用Zynq SDR套件的DDS HLS IP

评论