利用DDS IP实现线性调频信号1 DDS技术简介随着电子技术的不断发展,传统的频率合成技术逐渐不能满足人们对于频率转换速度、频率分辨率等方面的追求,直接数字频率合成技术应运而生。

直接数字频率合成技术(DDS) 是把一系列数据量形式的信号通过D/A转换器转换成模拟量形式的信号合成技术。DDS具有很多优点,比如:频率转换快、频率分辨率高、相位连续、低功耗、低成本与控制方便。

DDS技术满足了人们对于速度稳定性的需求,但是在一些控制较为复杂的系统中,DDS专用芯片不能很好的贴合要求。利用现场可编程门阵列(FPGA)实现DDS具有很大的灵活性,基本能满足现在通信系统的使用要求。

2 DDS IP使用说明

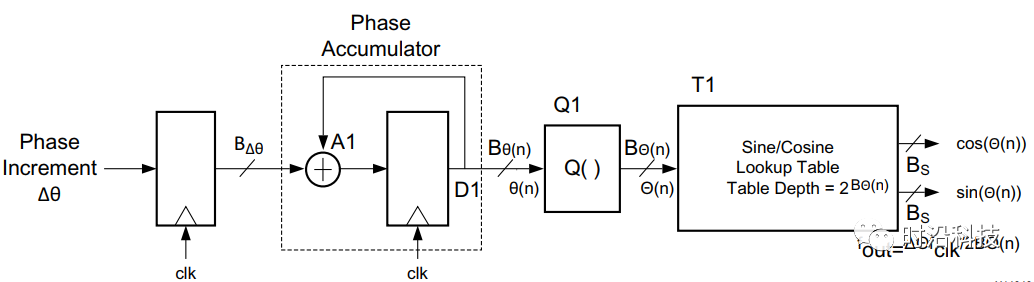

基于FPGA的DDS设计方案

3 线性调频信号

3.1 理论介绍

3.1.1 基本概念

线性调频(LFM)信号是瞬时频率随时间成线性变化的信号。线性调频信号也称为鸟声(Chirp)信号,因为其频谱带宽落于可听范围,听着像鸟声,所以又称Chirp扩展频谱(CSS)技术。

3.1.2 表达公式

本文重点研究Xlinx DDS IP实现线性调频信号,主要关心线性调频信号的相位变化情况,如若想要了解线性调频信号其他方面信息,请参考其他相关文章。

线性调频信号表达式:

线性调频信号数学公式

其中,t是时间,单位为秒(s);T是脉冲持续时间(周期);K是线性调频斜率,单位是Hz/s.

相位表达式:

φ(t)=πKt^2

相位变化率:

∆φ(t)=2πKt

3.1.3 应用范围

LFM技术在雷达、声纳技术中有广泛应用,例如,在雷达定位技术中,它可用来增大射频脉冲宽度、加大通信距离、提高平均发射功率,同时又保持足够的信号频谱宽度,不降低雷达的距离分辨率。

3.2.1 matlab代码

fs = 100e6; %采样率

T = 5e-6; %脉冲宽度

B = 10e6; %信号带宽

K = B/T;%调频斜率

N = round(T*fs);%采样点数

t = linspace(0,T,N);

y = exp(1j*pi*K*t.^2);%LFM信号

theta = pi*K*t.^2; %信号相位

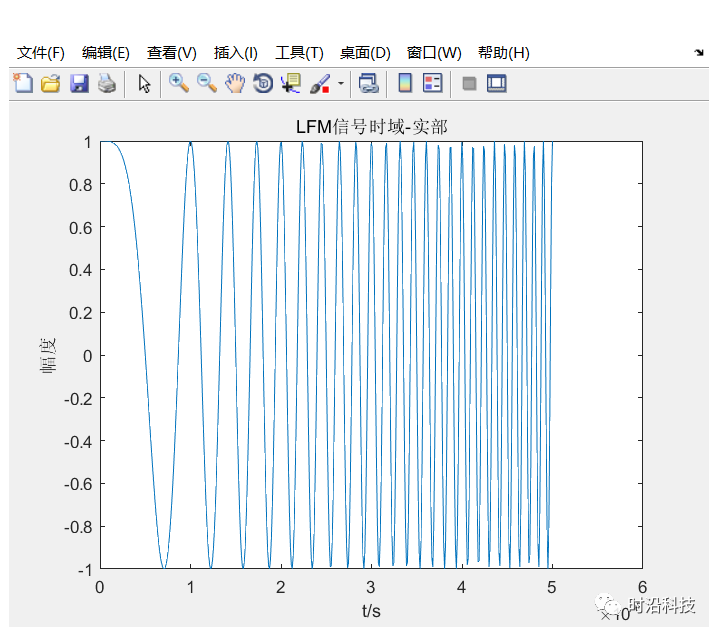

dtheta = pi*K*t; %相位变化量figure;

plot(t,real(y));

title(‘LFM信号时域-实部’);

xlabel(‘t/s’);

ylabel(‘幅度’);

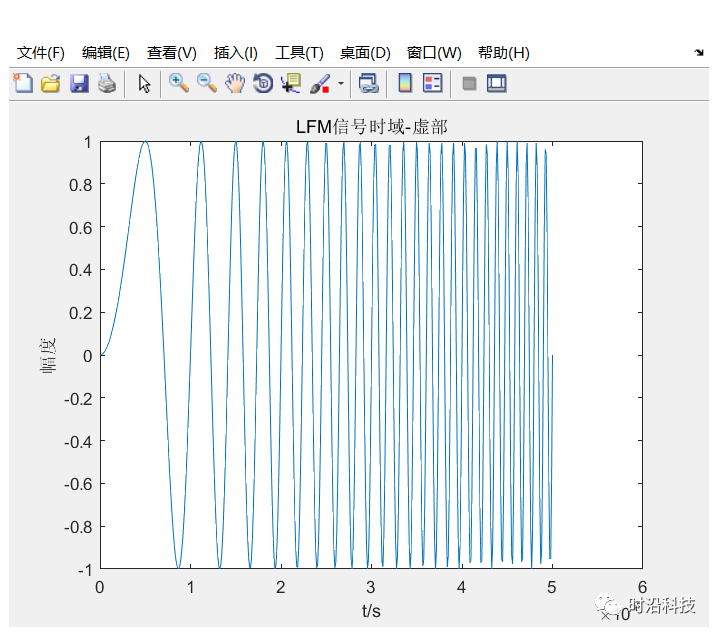

figure;

plot(t,imag(y));

title(‘LFM信号时域-虚部’);

xlabel(‘t/s’);

ylabel(‘幅度’);

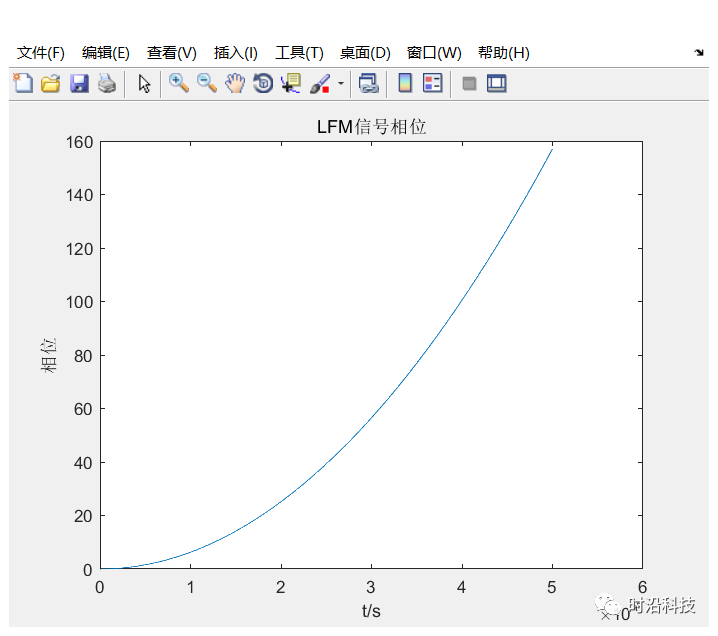

figure;

plot(t,theta);

title(‘LFM信号相位’);

xlabel(‘t/s’);

ylabel(‘相位’);

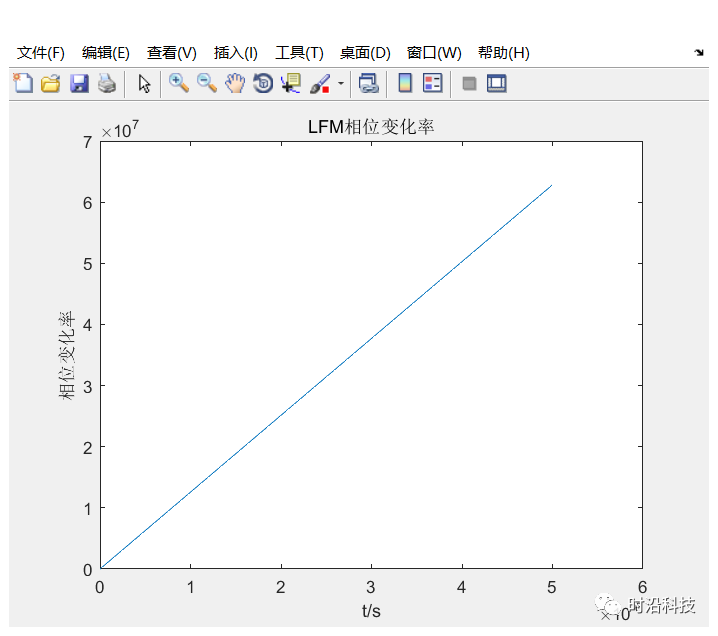

figure;

plot(t,dtheta);

title(‘LFM相位变化率’);

xlabel(‘t/s’);

ylabel(‘相位变化率’);

3.2.2 仿真结果图像

3.3 FPGA实现

3.3.1 参数计算

For example:

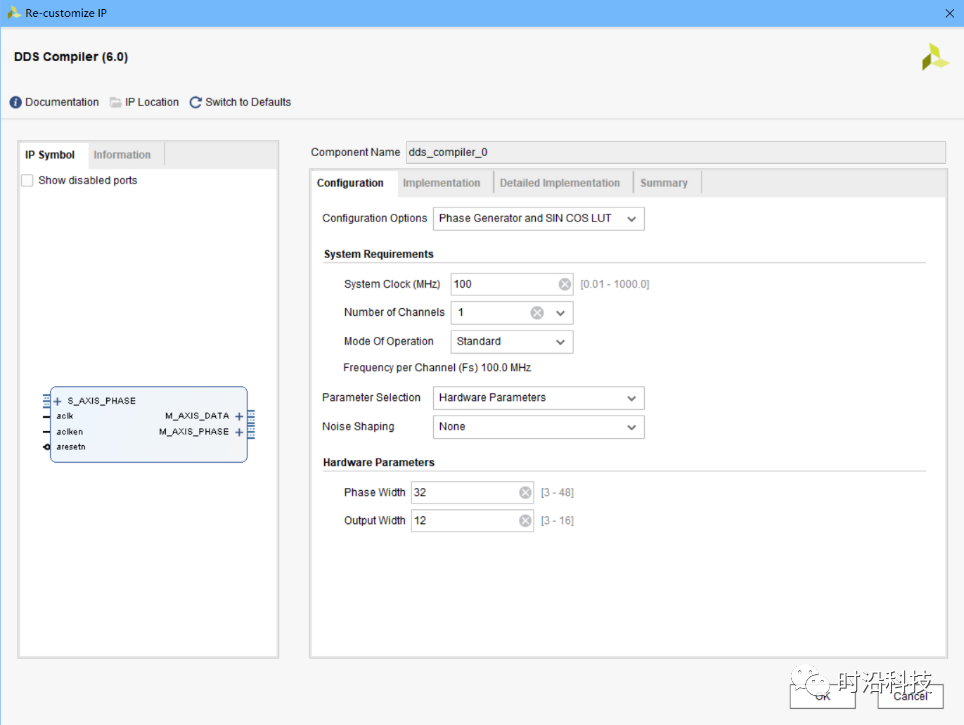

参数与上述matlab参数一致,采样率fs:100MHz,脉冲宽度T:5us,信号带宽B:10MHz,采样点数N:500。Xlinx DDS IP设置如下,假定相位累加器设置为32位,输出信号宽度设置为12位,可以根据自己的需求进行设计:

DDS IP配置界面1

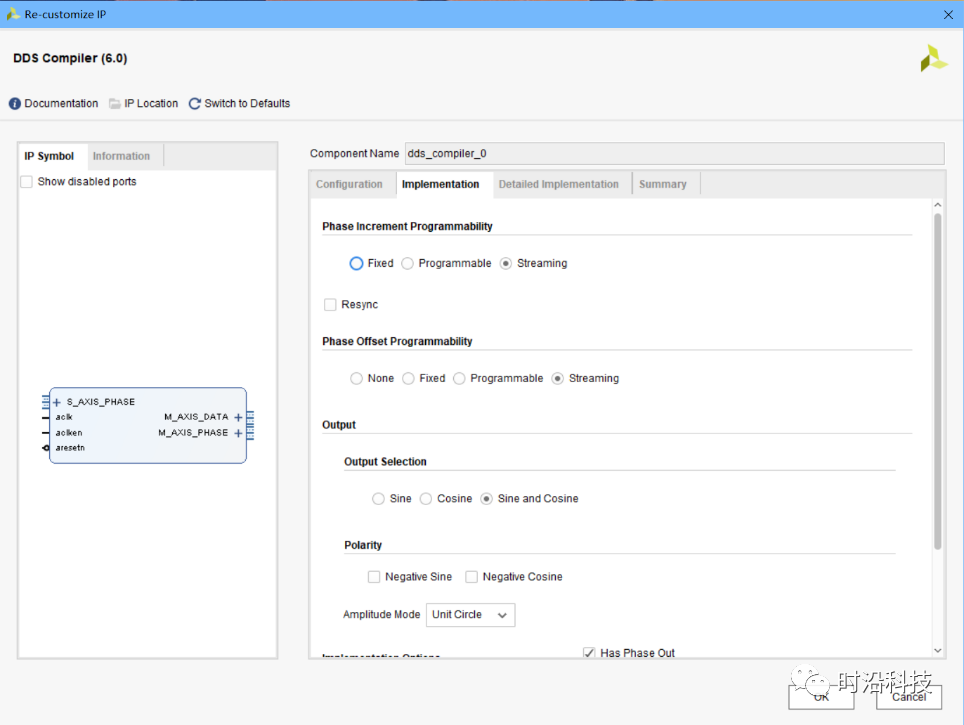

DDS IP配置界面2需要注意的是相位增量不是一个定值,而是随时间呈线性变化的量。根据公式相位表达式φ(t)=πKt^2与相位变化率∆φ(t)=2πKt,端口S_AXIS_PHASE的CHAN_0_POFF 与CHAN_0_PINC设置如下: 当t = 0时φ(t) = πKt^2 = 0;∆φ(t) = 2πKt = 0相位变化率∆φ(t)每次增加的量为2πK∆t:2πK∆t = 2πBT/TNfs = 2πB/N由于DDS IP相位累加器位数Bθ(n)为32,且参数[0,2^32]对于相位弧度[0,1],那么相位增量∆θ公式如下:∆θ = 2πB/N*1/2π*2^Bθ(n)/fs = 858993.4592≈858993综上,CHAN_0_POFF设置为0,CHAN_0_PINC从0开始每次增加∆θ。

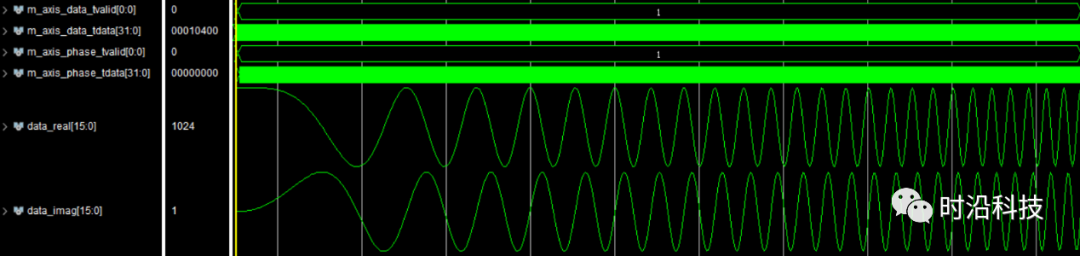

3.3.2 仿真结果

部分代码

//生成chirp信号

dds_compiler_0 suband_reference_waveform_inst (

.aclk (samp_clk),

.aclken (dds_aclken),

.aresetn (dds_aresetn),

.s_axis_phase_tvalid (s_axis_phase_tvalid),

.s_axis_phase_tdata (s_axis_phase_tdata),

.m_axis_data_tvalid (m_axis_data_tvalid),

.m_axis_data_tdata (m_axis_data_tdata),

.m_axis_phase_tvalid (m_axis_phase_tvalid),

.m_axis_phase_tdata (m_axis_phase_tdata)

);

wire signed [15:0] data_real = m_axis_data_tdata[15:0];

wire signed [15:0] data_imag = m_axis_data_tdata[31:16];

仿真波形

线性调频信号FPGA仿真波形

文章出处:【微信公众号:FPGA之家】

责任编辑:gt

-

FPGA

+关注

关注

1655文章

22283浏览量

630188 -

转换器

+关注

关注

27文章

9365浏览量

155105 -

DDS

+关注

关注

22文章

683浏览量

156068

原文标题:利用DDS IP实现线性调频信号(二)

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

音频信号接口浪涌保护器与射频信号接口浪涌保护器综合解决方案

Vivado浮点数IP核的握手信号

普源信号发生器DG5000直接数字合成(DDS)

FPGA利用DMA IP核实现ADC数据采集

基于FPGA的AM调制系统设计方案

电磁环境模拟系统设计方案

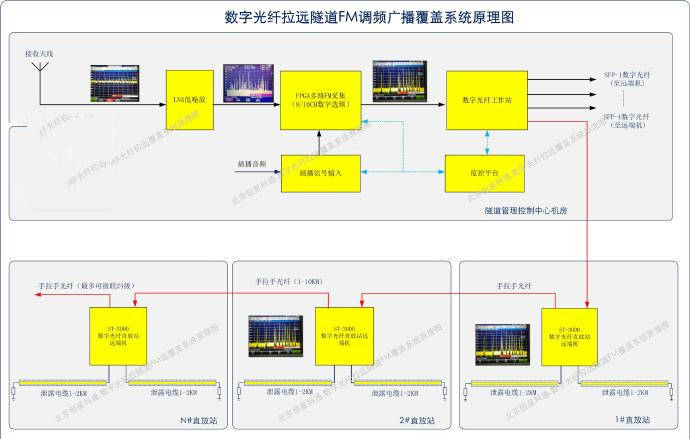

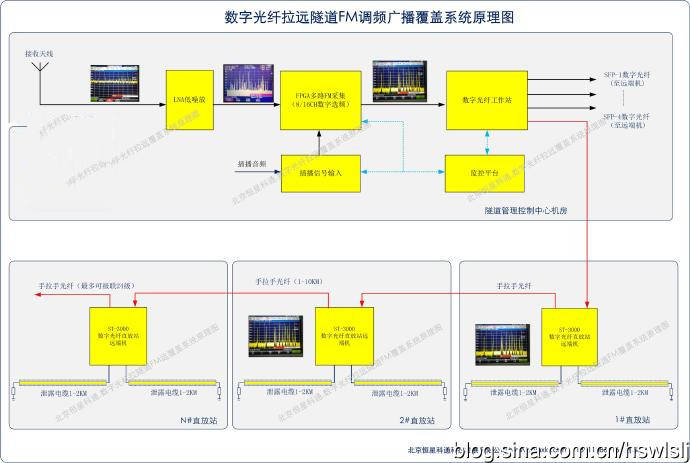

隧道FM广播信号、隧道内调频广播信号覆盖方案选择

使用IP核和开源库减少FPGA设计周期

基于FPGA的DDS IP实现线性调频信号的设计方案

基于FPGA的DDS IP实现线性调频信号的设计方案

评论