首次流片成功取决于整个系统硬件和相关软件的验证,有些公司提供的快速原型生成平台具有许多调试功能,但这些平台的价格非常高。

2011-01-18 12:23:16 1361

1361

在FPGA 上设计一个高性能、灵活的、面积小的通信体系结构是一项巨大的挑战。大多数基于FPGA 的片上网络都是运行在一个单一时钟下。随着FPGA 技术的发展,Xilinx 公司推出了Virtex-4 平台

2011-10-21 16:13:51 1784

1784

什么是FPGA原型? FPGA原型设计是一种成熟的技术,用于通过将RTL移植到现场可编程门阵列(FPGA)来验证专门应用的集成电路(ASIC),专用标准产品(ASSP)和片上系统(SoC)的功能

2022-07-19 16:27:29 2400

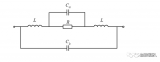

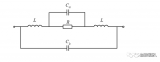

2400 在进行FPGA原型验证的过程中,当要把大型的SoC进行FPGA原型验证时,有时候会遇到一种情况,同样的接口分两组出去到不同的模块,而这两个模块规模较大,又需要分割在两片FPGA中,这时候就会像下图一样:

2023-04-25 11:15:20 2534

2534

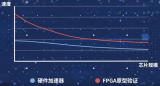

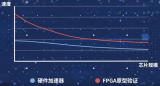

FPGA原型在数字芯片设计中非常重要,因为相比用仿真器,或者加速器等来跑仿真,FPGA的运行速度,更接近真实芯片,可以配合软件开发者来进行底层软件的开发。这一流片前的软硬件的协同开发,是其最不可替代的地方。

2023-05-10 10:44:00 11197

11197

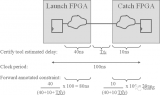

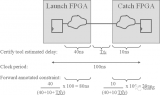

多片FPGA之间的互连,经常提到多路复用的概念,也经常提到TDM的概念,正确理解多路复用在多片FPGA原型验证系统中的机理,尤其是时序机制,对于我们正确看待和理解多片FPGA原型系统的性能有很好的促进作用。下图是一个使用多路复用器后接采样FF的多路复用解决方案的示例。

2023-06-06 10:04:35 2286

2286

今天我们一起来看一下射频电路中的那些无源器件。和数字和低频电路类似,射频电路也分为无源器件和有源器件

2023-10-08 16:03:25 1658

1658

Tape Out并回片后都可以进行驱动和应用的开发。目前ASIC的设计变得越来越大,越来越复杂,单片FPGA已不能满足原型验证要求,多片FPGA验证应运而生。本文我就将与大家探讨FPGA原型验证的几个经典挑战性场景,(具体应对的办法,请戳原文。)容量限制和性能要求

2020-08-21 05:00:12

各位专家好:

关于多片C6678的同步调试问题想咨询下:

我打算做两个板子,每个板子上集成两片C6678的芯片,板间通信打算用光传输,现在想咨询的问题是在用CCS进行调试的时候,这个能不能实现同步调试,比如在某个时间一起停下来,去看看各自寄存器或者变量的值。谢谢。

2018-06-21 02:37:42

用FPGA控制两片AD9739(以下简称A和B),其中A的SYNC_OUT接到了B的SYNC_IN,而A的SYNC_IN和B的SYNC_OUT接到了FPGA中。

现在配置0x10寄存器,采用无同步

2023-11-27 14:45:26

用4片AD9910,各种模式输出单片的调试都没有问题。现在要调多片同步,按照数据手册上的要求进行各个寄存器的配置,25M参考时钟输入,内部用锁相环陪频到1G,就是多片同步不了,12脚一直为高,检测

2018-11-20 09:11:33

多片AFE5818的输入ADC时钟为同步时钟,不同的芯片上LVDS串行数据时钟(DCLKP、DCLKM)和帧时钟(FCLKP、FCLKM)是否是同步的

2024-11-18 07:29:50

工作电路由输入时钟(CLKIN)实现同步,而后端电路由工作时钟(PROCLK)实现同步, 为了使四片DDC和EPLD之间系统时钟同步,系统要求用一个时钟信号源产生四路相干时钟分别分配给EPLD和四片

2019-06-04 05:00:17

通道验证同步和校准软件开发与生产硬件开发并行为了应对这一行业挑战,有一个基于软件可配置的高速转换器的新型多通道RF到位开发平台。该开发平台集成了数据转换器,RF分配,功率调节和时钟,以提供16通道直接S

2020-08-21 14:24:29

在STM32f407XX系列中,系统时钟(SYSTEM)默认的是HSE提供的,这里举例我们就将默认HSE切换成HSI提供。我们先来看一下时钟树(建议保存此图)首先、在系统中时钟都是设置好的,如果不是

2021-08-10 07:57:18

我们来看一下MCU设计中的情况,其中IoT RAM明显比外部DRAM具有优势。在下面的通用MCU图中,工作/静态存储器部分越来越需要扩展。在整个工作空间中使用DRAM会增加系统的功耗,并需要集成刷新

2021-11-10 06:59:22

我有一个应用打算使用4片ADC3853进行4通道的信号同步采集,采样率为64Msps,我希望这4片ADC3583能在同一时刻采集信号(即采样同步),然后将采集到的原始数据(即不抽取)送给FPGA

2024-11-18 06:17:07

原型验证---用软件的方法来发现硬件的问题 在芯片tap-out之前,通常都会计算一下风险,例如存在一些的严重错误可能性。通常要某个人签字来确认是否去生产。这是一个艰难的决定。ASIC的产品NRE

2019-07-11 08:19:24

with Tcl...........................................953.9 Gate Clock 处理............................................993.10 多片 FPGA 验证

2015-09-18 15:26:25

ASIC设计-FPGA原型验证

2020-03-19 16:15:49

如题,在不同时钟域下,多片ADS131E08如何实现不间断的同步采集?

2024-12-05 08:10:33

摘要:随着石油勘探的发展,在地震勘探仪器中越来越需要高精度的同步技术来支持高效采集。基于这种目的,采用FPGA技术设计了一种时钟恢复以及系统同步方案,并完成了系统的固件和嵌入式软件设计。通过室內测试

2019-06-18 08:15:35

在FPGA 上设计一个高性能、灵活的、面积小的通信体系结构是一项巨大的挑战。大多数基于FPGA 的片上网络都是运行在一个单一时钟下。随着FPGA 技术的发展,Xilinx 公司推出了Virtex-4

2019-08-21 06:47:43

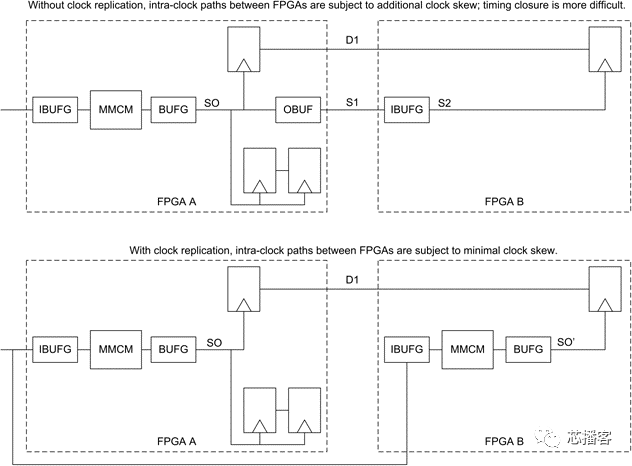

我想做多个FPGA的时钟同步,目前的想法是用一个FPGA的内部时钟,复制到外接IO口,接到另一个FPGA的外部时钟引脚,波形有较小的相移但是可以保证同步。想问一下可以复制多次,驱动多个FPGA的同步吗。对驱动能力有什么要求?其中每一个FPGA都用的是一个EP4CE的最小系统板。

2019-01-21 15:07:41

如果系统中使用多片功放芯片,如何实现时钟同步(例如TAS5622A)?

ST的芯片(如TDA7498)可以支持: Master芯片提供时钟给Slave芯片,从而实现多芯片同步。

2024-10-21 08:06:54

FPGA/CPLD设计(高级篇)(第2版)》选择ALTERA的器件可以看一下这两本《设计与验证Verilog HDL》 吴继华,王诚 这书不错,看电子版就好了《高级FPGA设计结构、实现也优化》(美)克里

2018-08-21 09:20:19

的设计和验证的复杂性需求。随着原型技术在设计分割以及多 FPGA 联 合调试领域的进步,基于FPGA 的原型系统不仅可以满足百万门级的设计需求,还可以实现设计规模高达15 亿门。基 于FPGA

2018-08-07 09:41:23

`板主,注册那天就激活了,但一直显示是待验证会员。按论坛任务提示也找不到“重新接收验证邮件”链接按钮在哪里?麻烦板主看一下是怎么回事,能不能帮忙人工改一下用户组?谢谢。`

2016-12-06 11:33:33

请教大神如何利用FPGA实现原型板原理图的验证?

2021-04-29 06:57:34

和发送数据,处理异步信号,以及为带门控时钟的低功耗ASIC进行原型验证。 这里以及后面章节提到的时钟域,是指一组逻辑,这组逻辑中的所有同步单元(触发器、同步RAM块以及流水乘法器等)都使用同一个网络

2022-10-14 15:43:00

如何将多片AD9361芯片进行相位同步,技术文档有说通过sync管脚进行MCS同步,但是仅仅只针对数据时钟完成同步。个人理解数据相位主要由RF混频处理以及后续数字处理决定,通过sync管教能够完成

2018-12-25 11:42:25

。基于FPGA的原型验证方法凭借其速度快、易修改、真实性的特点,已经成为ASIC芯片设计中重要的验证方法[2].本文主要描述高频RFID芯片的FPGA原型验证平台的设计,并给出验证结果。

2019-06-18 07:43:00

原型验证环境概述一套完整的RFID系统是由阅读器(Reader)、电子标签芯片(Tag)也就是所谓的应答器(Transponder)及应用软件三部分组成。电子标签芯片的FPGA原型验证环境也是一套完整

2019-05-29 08:03:31

在介绍了GPS 同步时钟基本原理和FPGA 特点的基础上,提出了一种基于FPGA 的GPS同步时钟装置的设计方案,实现了高精度同步时间信号和同步脉冲的输出,以及GPS 失步后秒脉冲的平

2009-07-30 11:51:45 45

45 随着大容量高速度的FPGA的出现,在流片前建立一个高性价比的原型验证系统已经成为缩短系统级芯片(SoC)验证时间,提高首次流片成功率的重要方法。本文着重讨论了用FPGA建

2009-09-11 15:50:09 16

16 随着SoC设计复杂度的提高,验证已成为集成电路设计过程中的瓶颈,而FPGA技术的快速发展以及良好的可编程特性使基于FPGA的原型验证越来越多地被用于SoC系统的设计过程。本文讨论

2010-11-11 16:00:07 35

35 设计一种基于FPGA的多通道同步数据采集存储系统,分为多通道同步数据采集模块和数据存储模块。系统设计采用多通道数据的同步实时采集以及坏块检测技术。多通道同步数据采集

2010-12-27 15:31:33 70

70 基于FPGA的提取位同步时钟DPLL设计

在数字通信系统中,同步技术是非常重要的,而位同步是最基本的同步。位同步时钟信号不仅用于监测输入码元信号,确保收发

2010-01-25 09:36:18 3699

3699

基于FPGA的可层叠组合式SoC原型系统设计

在复杂片上系统SoC的设计过程中,验证仿真是影响项目进度的关键因素。随着芯片生产和制造工艺的提高,SoC设计的规模、复杂

2010-01-08 11:18:42 1204

1204

为提高芯片验证与测试的可靠性,针对片上网络核心芯片的结构特点,设计出一种基于宿主机/目标机通信模式的测试系统。重点描述了测试系统软硬件的设计与实现,并采用Stratix系列FPGA芯片进行原型测试和验证。实验结果表明,该系统可对芯片的复位、实现功能及

2011-01-15 15:46:29 31

31 《 FPGA的原型开发方法手册》(FPMM),这是一本介绍如何使用 FPGA 作为平台进行片上系统(SoC)开发的实用指南。FPMM 收录了众多公司的设计团队在设计和验证方面的宝贵经验,

2011-03-14 09:06:50 1099

1099 介绍了一种基于SRAM技术的FPGA可编程逻辑器件的编程方法,能在系统复位或上电时自动对器件编程。有效地解决了基于SRAM的FPGA器件掉电易失性问题,针对当前系统规模的日益增大,本文提出了一种用单片机对多片FPGA自动加载配置的解决方案.

2011-03-15 16:41:22 21

21 新思科技有限公司推出HAPS-600 系列,这是其HAPS系列基于现场可编程门阵列(FPGA)原型验证系统中容量最高的一款产品

2011-03-22 09:32:15 1860

1860 S2C日前宣布其Verification Module技术(专利申请中)已可用于其基于 Xilinx 的FPGA原型验证系统中。V6 TAI Verification Module可以实现在FPGA原型验证环境和用户验证环境之间高速海量数据传输。用户

2011-09-20 09:07:58 1622

1622 新思科技公司日前宣布:该公司推出其Synopsys HAPS®-70系列基于FPGA的原型验证系统,从而扩展了其HAPS产品线以应对系统级芯片(SoC)设计的不断增加的规模及复杂度。

2012-11-27 21:51:39 1766

1766 新增的8种模块使设计者更专注于产品差异化, 并加快产品上市时间 S2C 公司,业内领先的 FPGA 快速原型验证系统供应商, 今日发布8种新的 FPGA 原型验证接口子卡和配件,其旨在加快发展片上

2017-02-08 06:50:11 1106

1106

加速 RTI 前的软件开发。 基于 FPGA 的原型设计,提供精确的周期、较高的执行效率和连接到外部的实际接口。 Synopsys 的混合原型解决方案将虚拟原型和基于 FPGA 的原型优势集于一身,加速了项目周期中软件开发和系统集成的进度。 借助 Synopsys 的混合原型验

2017-02-08 14:32:11 572

572 介绍了精密时钟同步协议(PTP)的原理。本文精简了该协议,设计并实现了一种低成本、高精度的时钟同步系统方案。该方案中,本地时钟单元、时钟协议模块、发送缓冲、接收缓冲以及系统打时标等功能都在FPGA中

2017-11-17 15:57:18 8779

8779

利用Xilinx的FPGA设计了一个FPGA原型验证平台,用于无源高频电子标签芯片的功能验证。主要描述了验证平台的硬件设计,解决了由分立元件实现模拟射频前端电路时存在的问题,提出了FPGA器件选型

2017-11-18 08:42:22 4347

4347

异步复位同步释放 首先要说一下同步复位与异步复位的区别。 同步复位是指复位信号在时钟的上升沿或者下降沿才能起作用,而异步复位则是即时生效,与时钟无关。异步复位的好处是速度快。 再来谈一下为什么FPGA设计中要用异步复位同步释放。

2018-06-07 02:46:00 2563

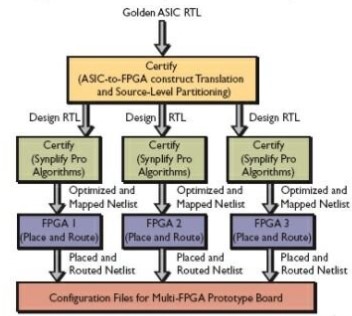

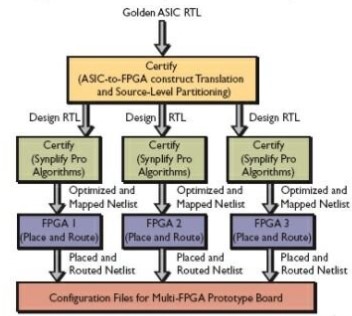

2563 在不太遥远的过去,对ASIC设计团队而言,在这类情况下主要的解决方案就是在内部建立他们自己的定制多个FPGA的原型开发板。然而,今天,使用现成的多个FPGA原型开发板——例如,由Synplicity

2019-05-16 08:07:00 3784

3784

基于FPGA的数字系统设计中大都推荐采用同步时序的设计,也就是单时钟系统。但是实际的工程中,纯粹单时钟系统设计的情况很少,特别是设计模块与外围芯片的通信中,跨时钟域的情况经常不可避免。如果对跨时钟域

2018-09-01 08:29:21 6010

6010

SMART不仅支持利用指令编写高速计数程序的功能,还提供了便捷的高速计数向导功能,只需要简单组态就可以自动生成程序,而且程序未进行加密,生成后可以修改。下面一起来看一下向导如何组态吧

2018-11-20 15:30:09 3836

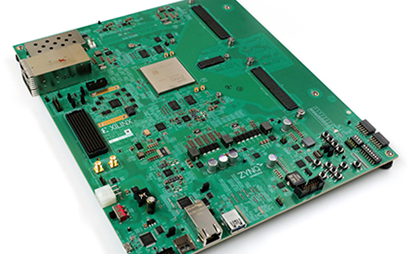

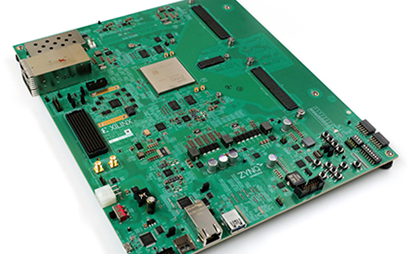

3836 以及ZYNQ 7020模组。XCVU13P主器件具有极其丰富的FPGA可编程逻辑资源,提供了强悍的算法原型验证能力。同时平台板载的ZYNQ 7020器件可用于系统管理并增强系统的灵活性。该平台提供有

2020-05-19 10:50:05 3371

3371 流片成功无疑是所有芯片开发者的共同目标,否则耗时持久的努力和流片所产生的高昂成本都将付诸东流。基于FPGA的原型验证是芯片流片前非常重要的一个步骤,不仅可以提高流片成功率,还可加速软件的开发速度。

2022-01-19 08:54:14 3208

3208 其次,部分FPGA开发板也被用在IP和小型芯片设计的开发验证场景。这部分开发板配备大容量的FPGA芯片,甚至是单板配备多片FPGA芯片来适应开发验证场景,一般由用户自己负责手工实现从设计到FPGA功能原型的流程。

2022-04-28 09:38:33 3563

3563 电路,是可编程的逻辑阵列。FPGA 的基本结构包括可编程输入输出单元、基本可编程逻辑单元、数字时钟管理模块、嵌入式块RAM、丰富的布线资源、内嵌专用硬核,以及底层内嵌功能单元。 图1 某FPGA的基本逻辑单元 市售常见的基于FPGA的平台产品包括FPGA开发板、FPGA原型验证系统。既然

2022-04-28 14:16:59 4031

4031

从系统的特性上看,FPGA 原型系统支持多FPGA、自动分割;性能较高的情况下运行系统软件;仿真加速器的超大容量可以放全芯片的设计,进行全芯片的系统功能/性能/功耗验证。

2022-05-25 09:35:13 10849

10849 往往需要设计各种不同的接口,用以和外界进行数据信号的交换互通,满足不同的使用需求。不同的接口设置与选择,也会极大影响原型验证系统产品的应用范围以及验证效率。因此,如何合理规划接口设置,就成为了一款优秀的原型验证系统必须要考虑的重要问题。 首先和大家介绍下目前

2022-09-19 13:40:03 1200

1200

在现代SoC芯片验证过程中,不可避免的都会使用FPGA原型验证,或许原型验证一词对你而言非常新鲜,但是FPGA上板验证应该是非常熟悉的场景了。

2023-03-28 09:33:16 2001

2001 FPGA原型验证在数字SoC系统项目当中已经非常普遍且非常重要,但对于一个SoC的项目而言,选择合适的FPGA原型验证系统显的格外重要

2023-04-03 09:46:45 2074

2074 当SoC系统的规模很大的时候,单片FPGA验证平台已经无法容纳这么多容量,我们将采取将SoC设计划分为多个FPGA的映射。

2023-04-06 11:20:48 1400

1400 如果SoC设计规模小,在单个FPGA内可以容纳,那么只要系统中的FPGA具有所SoC所设计需要时钟的数量

2023-04-07 09:42:57 1705

1705 FPGA原型设计是一种成熟的技术,用于通过将RTL移植到现场可编程门阵列(FPGA)来验证专门应用的集成电路(ASIC),专用标准产品(ASSP)和片上系统(SoC)的功能和性能。

2023-04-10 09:23:29 2664

2664 FPGA原型验证平台系统灵活性主要体现在其外部连接表现形式,由单片FPGA平台或者2片的FPGA,抑或是4片的FPGA组成一个子系统。

2023-04-11 09:50:03 1543

1543 FPGA原型验证平台系统灵活性主要体现在其外部连接表现形式,由单片FPGA平台或者2片的FPGA,抑或是4片的FPGA组成一个子系统。

2023-04-11 09:50:37 936

936 多片FPGA的原型验证系统的性能和容量通常受到FPGA间连接的限制。FPGA中有大量的资源,但IO引脚的数量受封装技术的限制

2023-04-12 10:14:42 1558

1558 FPGA原型验证系统要尽可能多的复用SoC相关的模块,这样才是复刻SoC原型的意义所在。

2023-04-19 09:08:15 1953

1953 门控时钟是一种在系统不需要动作时,关闭特定块的时钟的方法,目前很多低功耗SoC设计都将其用作节省动态功率的有效技术。

2023-04-20 09:15:13 2065

2065 在进行FPGA原型验证的过程中,当要把大型的SoC进行FPGA原型验证时,有时候会遇到一种情况,同样的接口分两组出去到不同的模块,而这两个模块规模较大,又需要分割在两片FPGA中,这时候就会像下图一样。

2023-05-04 16:21:34 1331

1331

多片FPGA原型验证系统的拓扑连接方式各不相同,理想的多片FPGA原型验证系统应该可以灵活配置,可以使用其相应的EDA工具

2023-05-08 11:51:40 891

891

当SoC的规模在一片FPGA中装不下的时候,我们通常选择多片FPGA原型验证的平台来承载整个SoC系统。

2023-05-10 10:15:16 689

689 SoC的顶层的约束适用于FPGA到其各自时钟域中的各个Flip_Flop,如果定义了跨时钟域,也适用于FPGA之间。当我们可以确保每个FPGA边界都有一个IOFF,它与SoC中相应的元素对齐时,这一点对于性能而言非常重要。

2023-05-13 09:38:09 2408

2408

FPGA原型验证的原理是将芯片RTL代码综合到FPGA上来验证芯片的功能。对于目前主流行业应用而言,芯片规模通常达到上亿门甚至数十亿门,一颗FPGA的容量难以容纳下芯片的所有逻辑功能。

2023-05-18 12:52:52 1145

1145

假如给定FPGA内的时钟没有正确运行,那么我们多片FPGA系统的整体将不能同时启动,这将有可能是致命的。

2023-05-22 09:21:24 621

621

当SoC的规模在一片FPGA中装不下的时候,我们通常选择多片FPGA原型验证的平台来承载整个SoC系统。

2023-05-23 15:31:10 1015

1015 如果SoC设计规模小,在单个FPGA内可以容纳,那么只要系统中的FPGA具有所SoC所设计需要时钟的数量

2023-05-23 15:46:24 1420

1420

FPGA原型验证系统要尽可能多的复用SoC相关的模块,这样才是复刻SoC原型的意义所在。

2023-05-23 16:50:34 1109

1109

多片FPGA的原型验证系统的性能和容量通常受到FPGA间连接的限制。FPGA中有大量的资源,但IO引脚的数量受封装技术的限制,通常只有1000个左右的用户IO引脚。

2023-05-23 17:12:35 2189

2189

我们当然希望在项目中尽快准备好基于FPGA原型验证的代码,以便最大限度地为软件团队和RTL验证人员带来更客观的收益。

2023-05-30 11:10:27 1358

1358

在现代SoC芯片验证过程中,不可避免的都会使用FPGA原型验证,或许原型验证一词对你而言非常新鲜,但是FPGA上板验证应该是非常熟悉的场景了。

2023-05-30 15:04:06 2103

2103

综合工具的任务是将SoC设计映射到可用的FPGA资源中。自动化程度越高,构建基于FPGA的原型的过程就越容易、越快。

2023-06-13 09:27:06 879

879

当SoC系统的规模很大的时候,单片FPGA验证平台已经无法容纳这么多容量,我们将采取将SoC设计划分为多个FPGA的映射。

2023-06-19 15:42:08 1081

1081 引言Preface如何快速便捷的完成巨型原型验证系统的组网,并监测系统的连通性及稳定性?如何将用户设计快速布局映射到参与组网的原型验证系统的每一块FPGA?随着用户设计规模的日益增大,传统基于单片

2022-06-16 10:19:18 1306

1306

丢失。 为了实现FPGA和DSP的同步时钟频率,可以采用以下两种方式: 1. 外部时钟源同步 通过引入外部时钟源,让FPGA和DSP的时钟信号由同一个时钟源提供,以此保证两者的时钟频率保持同步。在这种情况下,需要将时钟源的频率设置为两者的最大频率。 2. PLL同步 如

2023-10-18 15:28:13 2793

2793 FPGA原型设计是一种成熟的技术,用于通过将RTL移植到现场可编程门阵列(FPGA)来验证专门应用的集成电路(ASIC),专用标准产品(ASSP)和片上系统(SoC)的功能和性能。

2024-01-12 16:13:01 2194

2194 proFPGA是mentor的FPGA原型验证平台,当然mentor被西门子收购之后,现在叫西门子EDA。

2024-01-22 09:21:01 3230

3230

FPGA原型验证流程是确保FPGA(现场可编程门阵列)设计正确性和功能性的关键步骤。它涵盖了从设计实现到功能验证的整个过程,是FPGA开发流程中不可或缺的一环。

2024-03-15 15:05:33 3057

3057 FPGA原型验证平台与硬件仿真器在芯片设计和验证过程中各自发挥着独特的作用,它们之间存在明显的区别。

2024-03-15 15:07:03 2340

2340 引言原型验证是一种在FPGA平台上验证芯片设计的过程,通过在FPGA上实现芯片的设计原型,使得开发人员可以在硬件完成之前提前开始软件开发和系统验证。然而,如何快速确保在原型验证平台上开发的软件能

2024-09-30 08:04:29 1651

1651

近日,新思科技宣布推出全新基于AMD Versal™ Premium VP1902自适应系统级芯片(SoC)的HAPS®原型验证系统,以此进一步升级其硬件辅助验证(HAV)产品组合。 此次推出的全新一

2025-02-19 17:12:08 1235

1235

电子发烧友App

电子发烧友App

评论