本文主要介绍的是FPGA的片上资源使用情况,分别是从组合逻辑及时序逻辑来详细的分析。

2018-04-18 09:06:24 18789

18789

信号在FPGA器件中通过逻辑单元连线时,一定存在延时。延时的大小不仅和连线的长短和逻辑单元的数目有关,而且也和器件的制造工艺、工作电压、温度等有关。

2020-03-29 10:27:00 4067

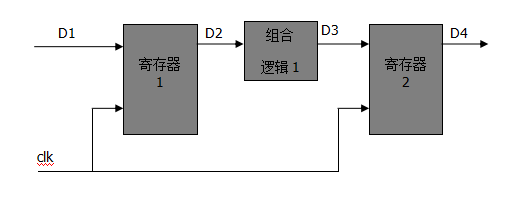

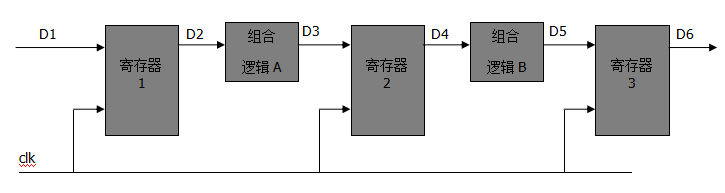

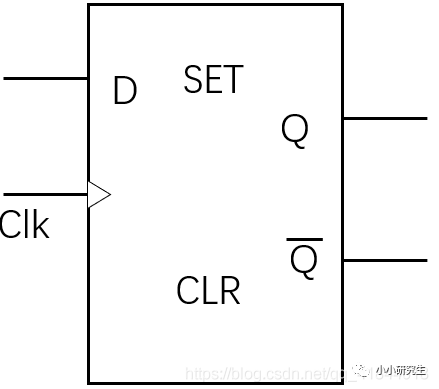

4067 作者: 小鱼,Xilinx学术合作 一. 概述 时序逻辑示意图,如下图所示。数据从一个寄存器出来,经过组合逻辑到达下一个寄存器。 在学习数字电路的过程中,我们都知道时序逻辑,但是大家对时序逻辑真的

2020-12-25 14:39:28 6509

6509

在FPGA设计中经常使用到逻辑复制,逻辑复制也用在很多场合。

2022-09-29 09:17:53 1256

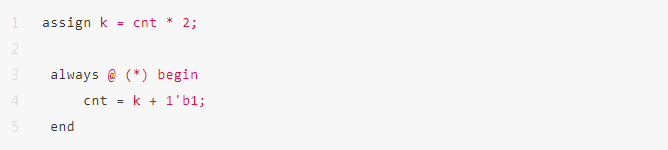

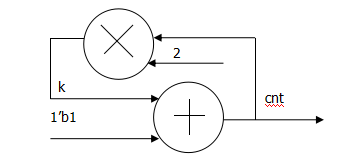

1256 数字电路根据逻辑功能的不同特点,可以分成两大类:一类叫做组合逻辑电路,简称组合电路或组合逻辑;另一类叫做时序逻辑电路,简称时序电路或时序逻辑。

2022-12-01 09:04:04 1445

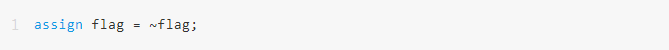

1445 数字门级电路可分为两大类:组合逻辑和时序逻辑。锁存器是组合逻辑和时序逻辑的一个交叉点,在后面会作为单独的主题处理。

2023-01-13 13:57:47 3032

3032

芯片设计是现代电子设备的重要组成部分,其中组合逻辑和时序逻辑是芯片设计中非常重要的概念。组合逻辑和时序逻辑的设计对于构建复杂的电路系统至关重要。

2023-08-30 09:32:15 1843

1843 FPGA中组合逻辑门占用资源过多怎么降低呢?有什么方法吗?

2023-04-23 14:31:17

大神求救!我现在想要用FPGA实现一个数与一个数组(宽度为64)数相乘,累加,再取平均,用的是时序逻辑加上非阻塞赋值的方法实现,即从数组0开始相乘,一直到数组63,当乘完63时,将累加的数取平均输出

2017-09-13 11:02:51

、冒险现象,时序逻辑一般不会出现。●组合逻辑的时序较难保证,时序逻辑更容易达到时序收敛。●组合逻辑只适合简单的电路,时序逻辑能够胜任大规模的逻辑电路。在今天的数字系统应用中,纯粹用组合逻辑来实现一个复杂

2015-01-22 21:46:14

出现。●组合逻辑的时序较难保证,时序逻辑更容易达到时序收敛。●组合逻辑只适合简单的电路,时序逻辑能够胜任大规模的逻辑电路。在今天的数字系统应用中,纯粹用组合逻辑来实现一个复杂功能的应用几乎绝迹了。时序逻辑在时钟

2021-08-18 14:45:34

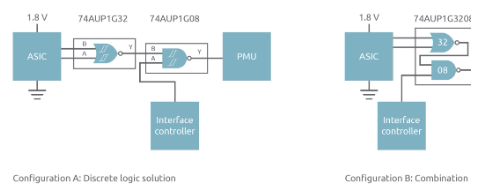

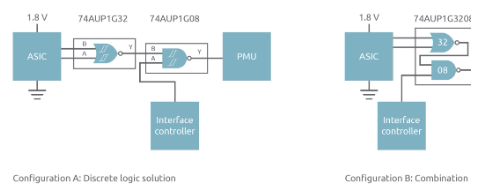

的逻辑粘合。所谓的逻辑粘合,无非是一些与、或、非等逻辑门电路简单拼凑的组合逻辑,没有时序逻辑,因此不需要引入时钟。而今天的FPGA器件的各种资源都非常丰富,已经很少有人只是用其实现简单的组合逻辑功能,而是

2015-06-29 09:31:03

很小的干扰滤除。但是,我们现在是在FPGA器件内部,还真没有这样的条件和可能性这么处理,那么只能放弃这种方案。另一种办法其实也就是引入时序逻辑,用寄存器多输出信号打一拍,这其实也是时序逻辑明显优于组合

2015-07-08 10:38:02

基本的时序分析理论1本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》配套例程下载链接:http://pan.baidu.com/s/1pJ5bCtt 何谓静态时序分析(STA,Static

2015-07-09 21:54:41

Tco(数据在芯片内部的路径延时)、Tsu(建立时间)和Th(保持时间)等,我们也可以用图示的这个模型来剖析一下芯片所给出的这些时序参数的具体路径。在这个模型中,画圈部分所覆盖的路径代表了和FPGA内部

2015-07-20 14:52:19

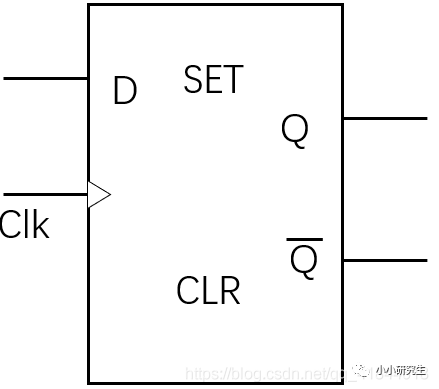

时间;CLK的变化频率会有一定的上限。对于每个具体型号的集成触发器,可以从手册上查到这些动态参数,在工作时应符合这些参数所规定的条件。 组合逻辑电路中,任一时刻的输出信号仅取决于当时的输入信号。时序

2023-02-22 17:00:37

时序电路)。 在组合逻辑电路中,任何时刻的输出仅仅取决于该时刻的输入,与电路原来的状态无关。这就是组合逻辑电路在逻辑功能上的共同特点。在上一节中,设计的三人表决器就是组合逻辑电路,输出与输入一一对应,和其他

2023-02-21 15:35:38

fpga时序逻辑电路的分析和设计 时序逻辑电路的结构及特点时序逻辑电路——任何一个时刻的输出状态不仅取决于当时的输入信号,还与电路的原状态有关。[hide][/hide]

2012-06-20 11:18:44

的逻辑关系;2、状态方程:按触发器的特性表或特性方程分析输入与触发器的输出(触发器的状态)的逻辑关系;3、输出方程:按组合逻辑电路的分析方法,将触发器输出(触发器的状态)与时序逻辑电路输出间的组合

2021-11-18 06:30:00

;nbsp; 在数字电路中,数字电路可分为组合逻辑电路和时序逻辑电路两大类。组合逻辑电路:任何时刻的输出取决于这一

2009-09-16 16:05:29

逻辑电路中,输出始终取决于其输入的组合。因此,组合电路是无记忆的。 因此,如果其输入条件之一从0-1或1-0改变状态,则默认情况下,组合逻辑电路的结果输出也将在其设计中具有“无内存”,“时序”或“反馈回路

2020-12-31 17:01:17

微型电子元件,在极小的空间内实现了复杂的逻辑功能。逻辑电路芯片根据设计不同,可以分为组合逻辑电路和时序逻辑电路两大类。

逻辑电路芯片的应用几乎涵盖了所有电子设备,包括但不限于:

计算机硬件:CPU

2024-09-30 10:47:47

最简与或表达式变换为与非一与非表达式,从而可以用与非门电路来实现。最简与或表达式有以下两个特点: ①与项(即乘积项)的个数最少。 ②每个乘积项中变量的个数最少。 代数法化简逻辑函数是运用逻辑代数

2009-04-07 10:54:26

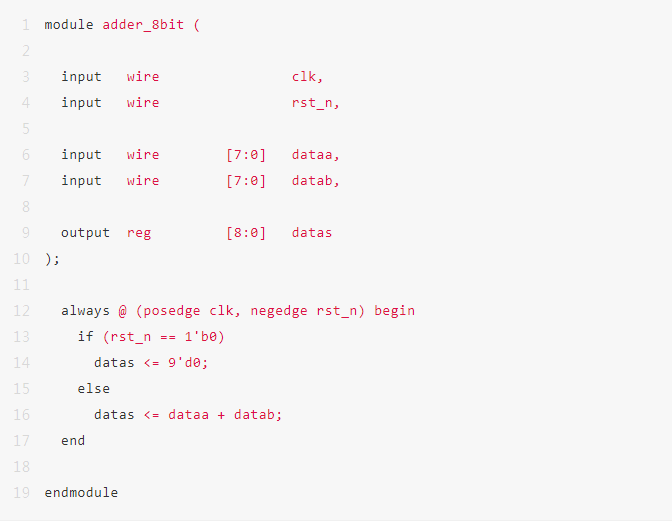

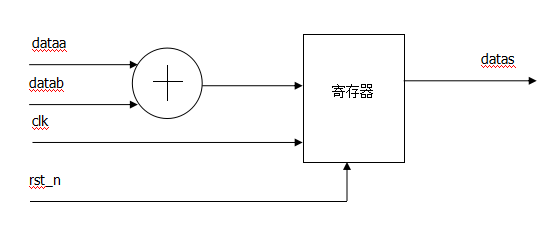

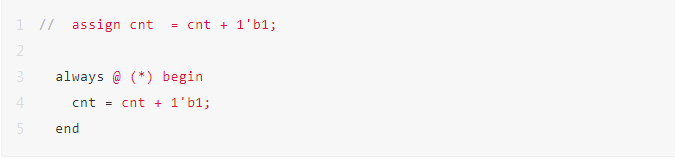

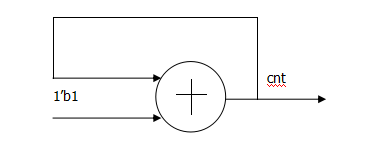

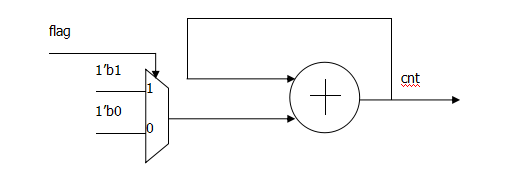

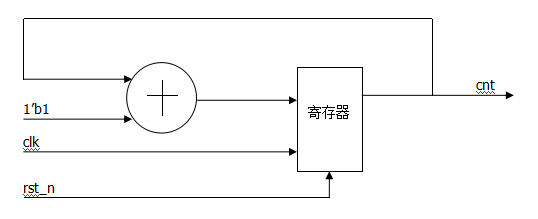

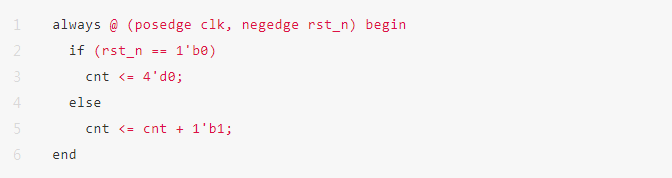

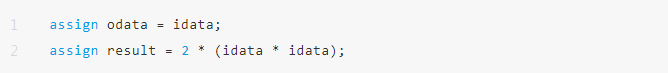

逻辑反映的电路也有不同,时序逻辑相当于在组合逻辑的基础上多了一个D触发器。 波形图层面,组合逻辑的波形是即刻反映变化的,与时钟无关;但是时序逻辑的波形不会立刻反映出来,只有在时钟的上升沿发生变化。用一个

2020-03-01 19:50:27

)来实现组合逻辑,每个查找表连接到一 个D触发器的输入端,触发器再来驱动其他逻辑电路或驱动I/O,由此构成了既可实现组合逻辑功能又可实现时序逻辑功能的基本逻辑单元模块,这些模块间利用 金属连线互相连接或

2019-08-11 04:30:00

为什么FPGA可以用来实现组合逻辑电路和时序逻辑电路呢?

2023-04-23 11:53:26

什么是时序逻辑?时序逻辑由哪几部分构成?

2021-09-17 07:43:37

1、FPGA开发板上组合逻辑电路的设计实现在之前的文章中已经介绍过了安路EG4S20 FPGA开发板以及TD工具的使用,从这篇文章开始,我们将介绍和分享一系列的基础实例,期望能帮助大家逐步

2022-07-21 15:38:45

较难保证,时序逻辑更容易达到时序收敛。●组合逻辑只适合简单的电路,时序逻辑能够胜任大规模的逻辑电路。在今天的数字系统应用中,纯粹用组合逻辑来实现一个复杂功能的应用几乎绝迹了。时序逻辑在时钟驱动下,能够

2017-11-17 18:47:44

的。话不多说,上货。 在FPGA中何时用组合逻辑或时序逻辑 在设计FPGA时,大多数采用Verilog HDL或者VHDL语言进行设计(本文重点以verilog来做介绍)。设计的电路都是利用

2023-03-06 16:31:59

涉及时序逻辑电路的实例,希望能够帮助大家理解在FPGA中实现时序逻辑电路。与组合逻辑电路相比,时序逻辑电路需要时钟的参与,电路中会有存储器件的参与,时序逻辑电路的输出不仅取决于这一时刻的输入,也受此

2022-07-22 15:25:03

Verilog程序模块的结构是由哪些部分组成的?如何去实现时序逻辑电路和组合逻辑电路的设计呢?

2021-11-03 06:35:57

0-1或1-0改变状态,则默认情况下,组合逻辑电路的结果输出也将在其设计中具有“无内存”,“时序”或“反馈环路”。组合逻辑组合逻辑电路由“组合”或连接在一起以产生更复杂的开关电路的基本逻辑“与非”门

2021-01-19 09:29:30

组合逻辑电路的基本模块是什么?时序逻辑电路怎样进行工作的?

2021-09-18 09:19:42

组合逻辑电路(简称组合电路)任意时刻的输出信号仅取决于该时刻的输入信号,与信号作用前电路原来的状态无关时序逻辑电路(简称时序电路)任意时刻的输出信号不仅取决

2009-07-15 18:45:58 0

0 组合逻辑电路电子教案:数字逻辑电路可分为两大类: 一类叫组合逻辑电路;另一类叫时序逻辑电路。本章首先介绍组合逻辑电路的共同特点和描述方法,然后重点介绍组合逻辑电

2009-09-01 08:58:29 0

0 同步时序逻辑电路:本章系统的讲授同步时序逻辑电路的工作原理、分析方法和设计方法。从同步时序逻辑电路模型与描述方法开始,介绍同步时序逻辑电路的分析步骤和方法。然后

2009-09-01 09:06:27 0

0 中规模集成时序逻辑设计:计数器:在数字逻辑系统中,使用最多的时序电路要算计数器了。它是一种对输入脉冲信号进行计数的时序逻辑部件。9.1.1 计数器的分类1.按数制

2009-09-01 09:09:09 13

13 异步时序逻辑电路:本章主要从同步时序逻辑电路与异步时序逻辑电路状态改变方式不同的特殊性出发, 系统的介绍异步时序逻辑电路的电路结构、工作原理、分析方法和设计方法。

2009-09-01 09:12:34 0

0 数字逻辑电路按逻辑功能和电路组成的特点可分为组合逻辑电路和时序逻辑电路两大类。

2010-08-10 11:51:58 39

39 数字逻辑电路可分为组合逻辑电路和时序逻辑电路两大类。组合逻辑电路在任一时刻的稳定输出只取决于当前的输入,而与过去的输入无关。在结构上,组合逻辑电路仅由若干逻

2010-08-12 15:54:42 0

0 数字电路分为组合逻辑电路(简称组合电路)和时序逻辑电路(简称时序电路)两类。在第三章中讨论的电路为组合电路。组合电路的结构模型如图4.1所示,它的输出函数表达式为

2010-08-13 15:23:02 24

24 数字集成电路,根据原理可分为两大类,既组合逻辑电路和时序逻辑电路。

组合逻辑电路的组成是逻辑门电路。电路的输出状态仅由同一时刻的输入状态决定,与电路的原

2010-08-18 15:05:23 55

55 组合逻辑电路的分析与设计-逻辑代数

在任何时刻,输出状态只决定于同一时刻各输入状态的组合,而与先前状态无关的逻辑电路称为组合逻辑电路。

2009-04-07 10:07:57 3922

3922

时序逻辑电路的分析方法

1. 时序逻辑电路的特点 在时序逻辑电路中,任意时刻的输出信号不仅取决于当时的输入信

2009-04-07 23:18:11 9154

9154

时序逻辑电路的特点

在第三章所讨论的组合逻辑电路中,任一时刻的输出信号仅仅取决于该时刻的输入信号,而与电路原来

2009-09-30 18:19:22 10881

10881

逻辑电路按其逻辑功能和结构特点可分为组合逻辑电路和时序逻辑电路。

2017-05-22 15:15:59 77018

77018

数字电路根据逻辑功能的不同特点,可以分成两大类,一类叫组合逻辑电路(简称组合电路),另一类叫做时序逻辑电路(简称时序电路)。组合逻辑电路在逻辑功能上的特点是任意时刻的输出仅仅取决于该时刻的输入

2017-11-20 12:26:21 9235

9235 数字电路根据逻辑功能的不同特点,可以分成两大类,一类叫组合逻辑电路(简称组合电路),另一类叫做时序逻辑电路(简称时序电路)。组合逻辑电路在逻辑功能上的特点是任意时刻的输出仅仅取决于该时刻的输入,与电路原来的状态无关。

2018-01-30 16:24:25 40173

40173

逻辑电路按其逻辑功能和结构特点可分为组合逻辑电路和时序逻辑电路。单一的与门、或门、与非门、或非门、非门等逻辑门不足以完成复杂的数字系统设计要求。组合逻辑电路是采用两个或两个以上基本逻辑门来实现更实用、复杂的逻辑功能。

2018-01-30 17:05:44 67767

67767

组合逻辑电路和时序逻辑电路都是数字电路,组合逻辑电路在逻辑功能上的特点是任意时刻的输出仅仅取决于该时刻的输入,与电路原来的状态无关。而时序逻辑电路在逻辑功能上的特点是任意时刻的输出不仅取决于当时的输入信号,而且还取决于电路原来的状态,或者说,还与以前的输入有关。

2018-01-30 17:26:04 94951

94951

分析时序逻辑电路也就是找出该时序逻辑电路的逻辑功能,即找出时序逻辑电路的状态和输出变量在输入变量和时钟信号作用下的变化规律。上面讲过的时序逻辑电路的驱动方程、状态方程和输出方程就全面地描述了时序逻辑电路的逻辑功能。

2018-01-30 18:55:32 128321

128321

本文开始介绍了时序逻辑电路的特点和时序逻辑电路的三种逻辑器件,其次介绍了时序逻辑电路的组成与时序逻辑电路检修方法,最后介绍了时序逻辑电路的应用举例。

2018-03-01 10:53:38 112182

112182

模块的模板包括了输入输出信号列表、信号定义,组合逻辑和时序逻辑等,这是一个模块常用的组件。学员只需要理解各个部分的意义,按要求来填空就可以,完全没有必要去记住。我看很多学员刚开始学习时,花费大量的时间去记住、背熟模块,这是没有意义的。

2018-04-20 15:40:00 1957

1957

根据逻辑功能的不同,可把数字电路分为组合逻辑电路(Combinational Logic Circuit)和 时序逻辑电路(Sequential Logic Circuit)两大类。

2018-07-20 08:00:00 0

0 数字电路根据逻辑功能的不同特点,可以分成两大类,一类叫组合逻辑电路(简称组合电路),另一类叫做时序逻辑电路(简称时序电路)。组合逻辑电路在逻辑功能上的特点是任意时刻的输出仅仅取决于该时刻的输入

2019-02-26 15:22:20 32847

32847 时序逻辑电路是由组合逻辑电路与记忆电路(又称存储电路) 组合而成的。 常见时序逻辑电路有触发器、 寄存器和计数器等。

2019-02-26 15:25:01 52417

52417 组合逻辑电路是任意时刻的输出仅仅取决于该时刻的输入,与电路原来的状态无关。而时序逻辑电路不仅仅取决于当前的输入信号,而且还取决于电路原来的状态,或者说,还与以前的输入有关。

2019-02-26 15:32:30 67227

67227 本文档的主要内容详细介绍的是FPGA视频教程之FPGA设计中时序逻辑设计要点的详细资料说明免费下载。

2019-03-27 10:56:04 20

20 数字电路根据逻辑功能的不同特点,可以分成两大类,一类叫组合逻辑电路(简称组合电路),另一类叫做时序逻辑电路(简称时序电路)。组合逻辑电路在逻辑功能上的特点是任意时刻的输出仅仅取决于该时刻的输入

2019-05-16 18:32:37 8978

8978

本课程以目前流行的Xilinx 7系列FPGA的开发为主线,全面讲解FPGA的原理及电路设计、Verilog HDL语言及VIVADO的应用,并循序渐进地从组合逻辑、时序逻辑的开发开始,深入到FPGA的基础应用、综合应用和进阶应用。

2019-12-05 07:08:00 3476

3476

本课程以目前流行的Xilinx 7系列FPGA的开发为主线,全面讲解FPGA的原理及电路设计、Verilog HDL语言及VIVADO的应用,并循序渐进地从组合逻辑、时序逻辑的开发开始,深入到FPGA的基础应用、综合应用和进阶应用。

2019-12-03 07:04:00 3009

3009

组合逻辑电路是无记忆数字逻辑电路,其任何时刻的输出仅取决于其输入的组合.

2019-06-22 10:53:20 50945

50945

逻辑电路在任何时刻产生的稳定的输出信号仅仅取决于该时刻的输入信号,而与过去的输入信号无关,即与输入信号作用前的状态无关,这样的电路称为组合逻辑电路。

2020-08-08 10:40:00 6454

6454

本文档的主要内容详细介绍的是组合逻辑电路和时序逻辑电路的学习课件免费下载包括了:任务一 组合逻辑电路,任务二 编码器,任务三 译码器,任务四 集成触发器,任务五 寄存器,任务六 计数器。

2020-10-27 15:58:24 31

31 组合逻辑电路是指在任何时刻,输出状态只决定于同一时刻各组合逻辑电路输入状态的组合,而与电路以前状态无关而与其他时间的状态无关。如:加法器、编码器、译码器、选择器等

2020-12-09 14:49:02 12

12 本文档的主要内容详细介绍的是华为FPGA硬件的静态时序分析与逻辑设计包括了:静态时序分析一概念与流程,静态时序分析一时序路径,静态时序分析一分析工具

2020-12-21 17:10:54 22

22 从今天开始新的一章-Circuits,包括基本逻辑电路、时序电路、组合电路等。

2022-10-10 15:39:01 2278

2278 在进行MCU开发时,有时需要用到一些简单的数字逻辑电路,LPC804与LPC55XX系列集成了PLU(Programmable Logic Unit),即可编程逻辑单元,可创建小型组合与时序逻辑电路,降低成本。

2022-12-01 09:17:42 2388

2388 数字门级电路可分为两大类:组合逻辑和时序逻辑。锁存器是组合逻辑和时序逻辑的一个交叉点,在后面会作为单独的主题处理。

2022-12-21 09:18:32 1882

1882 本文介绍开发组合逻辑电路时可能发生的意外开关事件,称为危险。 本文是关于使用逻辑门进行组合电路设计和仿真的介绍性系列文章的第二部分。在上一篇文章中,我们介绍了 组合逻辑电路 以及如何简化它们

2023-01-27 14:18:00 2709

2709

组合逻辑在单个微型逻辑包中集成了至少两种不同的逻辑功能。这些功能可以在内部级联或完全独立。无论如何,组合逻辑都支持使用一个设备而不是多个设备。这降低了功耗和引脚数,并显著节省了空间,因为内部信号共享电源和接地。

2023-02-10 10:01:09 1231

1231

数字门级电路可分为两大类:组合逻辑和时序逻辑。锁存器是组合逻辑和时序逻辑的一个交叉点,在后面会作为单独的主题处理。

2023-02-12 10:28:36 2026

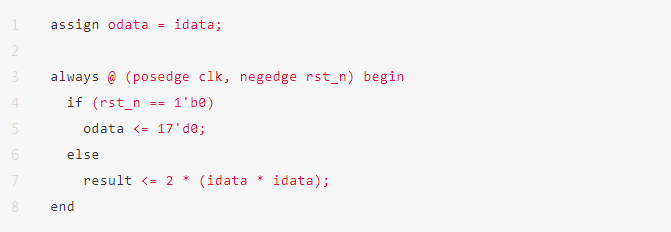

2026 使用always_ff和在灵敏度列表中指定一个时钟边沿并不意味着过程中的所有逻辑都是时序逻辑。综合编译器将推断出每个被非阻塞赋值的变量的触发器。阻塞赋值也可能推断出触发器,这取决于赋值语句相对于程序中其他赋值和操作的顺序和上下文。

2023-02-20 10:38:06 1208

1208 数字电路根据逻辑功能的不同特点,可以分成两大类,一类叫组合逻辑电路(简称组合电路),另一类叫做时序逻辑电路(简称时序电路)。组合逻辑电路在逻辑功能上的特点是任意时刻的输出仅仅取决于该时刻的输入

2023-03-14 17:06:50 8730

8730

本系列将带来FPGA的系统性学习,从最基本的数字电路基础开始,最详细操作步骤,最直白的言语描述,手把手的“傻瓜式”讲解,让电子、信息、通信类专业学生、初入职场小白及打算进阶提升的职业开发者都可以有

2023-03-21 09:50:03 1682

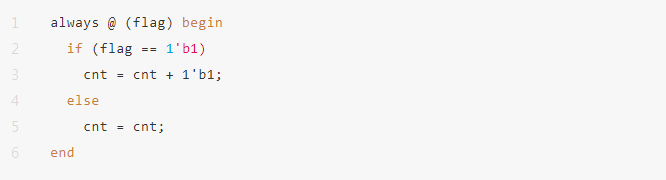

1682 时序逻辑的代码一般有两种: 同步复位的时序逻辑和异步复位的时序逻辑。在同步复位的时序逻辑中复位不是立即有效,而在时钟上升沿时复位才有效。 其代码结构如下:

2023-03-21 10:47:07 1239

1239 组合逻辑最大的缺点就是会存在竞争冒险,使用时序逻辑就可以极大地避免这种问题,从而使系统更加稳定。

2023-05-22 15:30:24 2544

2544

时序逻辑电路分析和设计的基础是组合逻辑电路与触发器,所以想要分析和设计,前提就是必须熟练掌握各种常见的组合逻辑电路与触发器功能,尤其是各种触发器的特征方程与触发模式,因此前几文的基础显得尤为重要。 本文主要介绍时序逻辑电路的分析方法。

2023-05-22 18:24:31 5502

5502

电子发烧友网站提供《在Artix 7 FPGA上使用Vivado的组合逻辑与顺序逻辑.zip》资料免费下载

2023-06-15 09:14:49 0

0 当逻辑电路由多个逻辑门组成且不含存储电路,对于给定的输入变量组合将产生确定的输出,则这种逻辑电路称为组合逻辑电路。

2024-02-04 11:46:36 3337

3337

组合逻辑电路和时序逻辑电路是数字电路中两种重要的逻辑电路类型,它们主要区别在于其输出信号的依赖关系和对时间的敏感性。

2024-02-04 16:00:27 7168

7168 时序逻辑电路是一种能够存储信息并根据时钟信号按照特定顺序执行操作的电路。它是计算机硬件中非常重要的一部分,用于实现存储器、时序控制器等功能。与之相对的是组合逻辑电路,它根据输入信号的组合情况,立即

2024-02-06 11:18:34 13635

13635 组成:组合逻辑电路和时钟电路。组合逻辑电路是一种基本的逻辑电路,其输出仅仅取决于当前的输入信号,与时间无关。组合逻辑电路由门电路(如与门、或门、非门等)组成,通过门的组合和连接构成了复杂的逻辑功能。时序逻辑电路将

2024-02-06 14:30:23 4293

4293 什么是组合逻辑电路和时序逻辑电路?时序逻辑电路和组合逻辑电路的区别是什么 组合逻辑电路和时序逻辑电路是数字电路中两种基本类型的电路设计。 组合逻辑电路是由逻辑门组成的,逻辑门的输出仅由它的当前输入

2024-03-26 16:12:14 6631

6631 、组合逻辑控制器概述 1.1 定义 组合逻辑控制器是一种基于组合逻辑电路的控制器,它通过逻辑运算来实现对系统中各个组件的控制和管理。组合逻辑控制器的核心是逻辑门,包括与门、或门、非门、异或门等基本逻辑门,以及由它们

2024-06-30 10:11:28 1147

1147 一、引言 组合逻辑电路是数字电路中的重要组成部分,它仅由逻辑门电路(如与门、或门、非门等)和输入/输出端组成,不包含任何存储元件。组合逻辑电路的输出仅取决于当前的输入信号,与电路的历史状态无关。因此

2024-07-30 14:38:04 3066

3066 组合逻辑电路是数字逻辑电路的一种,其特点是输出只依赖于当前的输入状态,而与输入信号的变化历史无关。组合逻辑电路广泛应用于数字系统中,如计算机、通信设备、控制设备等。以下是对常用的组合逻辑电路的介绍

2024-07-30 14:41:37 4783

4783 当前的输入信号,还取决于电路的历史状态。与组合逻辑电路不同,组合逻辑电路的输出仅取决于当前的输入信号,而时序逻辑电路的输出则受到电路内部状态的影响。时序逻辑电路通常由触发器(Flip-flops)、寄存器(Registers)和计数器

2024-07-30 15:02:11 3419

3419 时序逻辑电路形成对比,后者具有记忆功能,输出不仅取决于当前输入,还与过去的状态有关。 并行处理能力 :组合逻辑电路可以同时处理多个输入信号,实现并行运算。这种并行处理能力使得组合逻辑电路在处理速度上具有优势。 可

2024-08-11 11:14:59 2615

2615 的状态确定,组合逻辑电路的输出状态也就随之确定。换句话说,组合逻辑电路的输出是输入信号现态的逻辑函数,没有记忆功能,也没有时序或反馈回路。 无关因素 输出信号的现态 :组合逻辑电路的输出状态与输出信号的先前状态无关。

2024-08-11 11:24:35 2579

2579 时序逻辑电路本身并不直接“产生”锁存器,但锁存器是时序逻辑电路中的重要组成部分。时序逻辑电路(Sequential Logic Circuits)与组合逻辑电路(Combinational

2024-08-28 11:03:47 1319

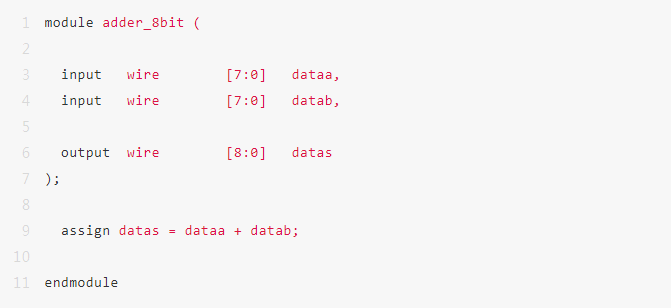

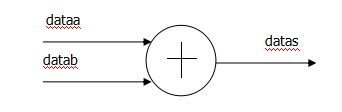

1319 加法器不是时序逻辑电路 ,而是组合逻辑电路的一种。时序逻辑电路和组合逻辑电路的主要区别在于它们如何处理输出信号。 组合逻辑电路的输出仅依赖于当前的输入信号,而不依赖于电路之前的状态或输入历史。这

2024-08-28 11:05:51 2051

2051 时序逻辑电路是数字电路中的一种重要类型,其特点是电路的输出不仅取决于当前的输入,还取决于电路的状态。时序逻辑电路广泛应用于计算机、通信、控制等领域。 1. 引言 在数字电路设计中,时序逻辑电路是实现

2024-08-28 11:41:38 1914

1914 Logic Circuit)是一种在数字电路中,其输出不仅取决于当前输入,还取决于过去输入历史的电路。与组合逻辑电路(Combinational Logic Circuit)不同,组合逻辑电路的输出仅取决于当前的输入,而时序逻辑电路则具有记忆功能,能够根据输入信号的变化顺序来

2024-08-28 11:45:49 5359

5359 时序逻辑电路确实具有记忆功能 。这一特性是时序逻辑电路与组合逻辑电路的本质区别之一。

2024-08-29 10:31:28 2362

2362

电子发烧友App

电子发烧友App

评论