前边写了很多关于板上外围器件的评测文章,这篇是FPGA纯逻辑设计,是FPGA的另一部分——算法实现,上篇文章做了HDC1000传感器的使用,当时说FPGA是不支持小数的,本篇记述的是FPGA如何去做

2020-06-17 10:17:27 8274

8274

数字电路根据逻辑功能的不同特点,可以分成两大类:一类叫做组合逻辑电路,简称组合电路或组合逻辑;另一类叫做时序逻辑电路,简称时序电路或时序逻辑。

2022-12-01 09:04:04 1445

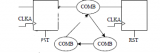

1445 数字逻辑电路分为组合逻辑电路和时序逻辑电路。时序逻辑电路是由组合逻辑电路和时序逻辑器件构成(触发器),即数字逻辑电路是由组合逻辑和时序逻辑器件构成。

2023-03-21 09:49:49 1443

1443 芯片设计是现代电子设备的重要组成部分,其中组合逻辑和时序逻辑是芯片设计中非常重要的概念。组合逻辑和时序逻辑的设计对于构建复杂的电路系统至关重要。

2023-08-30 09:32:15 1843

1843 影响电路工作的可靠性、稳定性,严重时会导致整个数字系统的误动作和逻辑紊乱。下面就来讨论交流一下FPGA 的竞争冒险与毛刺问题。

在数字电路中,常规介绍和解释:

什么是竞争与冒险现象:

在组合电路中

2023-11-02 17:22:20

FPGA中组合逻辑门占用资源过多怎么降低呢?有什么方法吗?

2023-04-23 14:31:17

图像采集系统的结构及工作原理是什么FPGA逻辑设计中的常见问题有哪些

2021-04-29 06:18:07

请教各位,FPGA在逻辑设计中有哪些注意事项?

2021-05-07 07:21:53

以及高速数字电路的时序设计与优化。相信通过三天的学习,将会对学员在逻辑设计领域的工作和学习大有裨益。课程时间的安排上授课占60%,实验占40%。五、培训对象课程适合于使用FPGA器件进行科研、教学和产品

2009-07-24 13:13:48

应该的状态,它也就是这个组合逻辑的毛刺。(特权同学,版权所有)图5.15 逻辑延时波形既然我们的多个输入信号的变化前后取值都保持高电平,那么这个低脉冲的毛刺其实不是我们希望看到的,也很可能在后续电路中

2015-07-08 10:38:02

的瞬间,组合逻辑的输出常常产生一些小的尖峰,即毛刺信号,这是由FPGA内部结构特性决定的。毛刺现象在FPGA的设计中是不可避免的,有时任何一点毛刺就可以导致系统出错,尤其是对尖峰脉冲或脉冲边沿敏感

2012-09-06 14:37:54

,提高电路的稳定性,而且其先进的开发工具使整个系统的设计调试周期大大缩短。而在FPGA设计中也存在一些难点问题,本文将主要分析、讨论毛刺信号的产生原因及消除毛刺的方法。通过综合运用这些方法,可以最大

2009-04-21 16:47:58

实战应用,这种快乐试试你就会懂的。话不多说,上货。 数字电路中的组合逻辑 根据逻辑功能的不同特点,可以将数字电路分为两大类,一类称为组合逻辑电路(简称组合电路),另一类称为时序逻辑电路(简称

2023-02-21 15:35:38

;nbsp; 同时随着FPGA在整个系统中开始扮演越来越重要的角色,FPGA的接口技术,以及与外部处理器、功能芯片之间甚至是其他系统之间的接口技术也成为FPGA

2010-03-10 17:52:19

;nbsp; 同时随着FPGA在整个系统中开始扮演越来越重要的角色,FPGA的接口技术,以及与外部处理器、功能芯片之间甚至是其他系统之间的接口技术也成为FPGA

2010-03-10 17:58:29

"。如果一个组合逻辑电路中有"毛刺"出现,就说明该电路存在"冒险"。(与分立元件不同,由于PLD内部不存在寄生电容电感,这些毛刺将被完整的保留并向下一级传递

2012-02-10 09:50:36

组合逻辑电路PPT电子教案学习要点: 组合电路的分析方法和设计方法 利用数据选择器和译码器进行逻辑设计的方法 加法器、编码器、译码器等中

2009-09-16 16:05:29

的分析和设计方法。 2. 掌握译码器、编码器和数据选择器的功能及在组合逻辑设计中的应用。 &

2009-09-16 15:09:13

逻辑电路中,输出始终取决于其输入的组合。因此,组合电路是无记忆的。 因此,如果其输入条件之一从0-1或1-0改变状态,则默认情况下,组合逻辑电路的结果输出也将在其设计中具有“无内存”,“时序”或“反馈回路

2020-12-31 17:01:17

本帖最后由 gk320830 于 2015-3-9 20:12 编辑

组合逻辑设计原则--Combinational logic design principles-数字电路 (数字设计原理)[hide][/hide]

2009-09-26 12:51:11

组合逻辑设计实践- Combinational logic design practices-(数字设计原理与实践)

2009-09-26 12:52:53

偏硬件:接口电路中的门组合电路;偏软件:算法、接口控制器实现中的状态机群或时序电路。随着逻辑设计的深入,复杂功能设计一般基于同步时序电路方式。此时,逻辑设计基本上就是在设计状态机群或计数器等时序电路

2021-11-10 06:39:25

后加入深圳某500强通信企业网络产品线逻辑综合开发部,从事接入网FPGA业务逻辑开发工作至今。参与或直接负责接入逻辑OLT设备中QM队列调度模块逻辑设计,VMAC协议逻辑设计,以太OAM协议逻辑设计

2015-03-11 16:13:48

`MCS-51单片机与FPGA接口的逻辑设计.........`

2013-06-08 11:25:29

MPEG-2编码复用器中的FPGA逻辑设计,看完你就懂了

2021-04-29 06:13:34

根据逻辑电路的不同特点,数字电路分为组合逻辑和时序逻辑,明德扬粉丝里的同学提出,无法正确区分,今天让我跟一起来学习一下两种逻辑的区别以及使用环境。·时序逻辑和组合逻辑的区别关于组合逻辑和时序逻辑

2020-03-01 19:50:27

(Interconnect)三个部分。 现场可编程门阵列(FPGA)是可编程器件,与传统逻辑电路和 门阵列(如PAL,GAL及CPLD器件)相比,FPGA具有不同的结构。FPGA利用小型查找表(16×1RAM

2019-08-11 04:30:00

为什么FPGA可以用来实现组合逻辑电路和时序逻辑电路呢?

2023-04-23 11:53:26

FPGA开发板上组合逻辑电路的实现,这些实例包括在数字逻辑设计课程中所熟知的部分中规模集成电路:优先编码器、多路复用器以及加法器,最后还将介绍算术逻辑单元ALU的实现。优先编码器实验原理在数字系统中

2022-07-21 15:38:45

```勇敢的芯伴你玩转Altera FPGA连载25:组合逻辑与时序逻辑特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1i5LMUUD 数字电路按照逻辑

2017-11-17 18:47:44

单片机与FPGA总线接口逻辑设计1、利用FPGA内部RAM存储256个字节数据,并将数据发送到单片机并在串口调试工具显示;2、通过串口调试工具经单片机发送数据到FPGA,并通过LED显示。

2012-03-04 13:09:58

的。话不多说,上货。 在FPGA中何时用组合逻辑或时序逻辑 在设计FPGA时,大多数采用Verilog HDL或者VHDL语言进行设计(本文重点以verilog来做介绍)。设计的电路都是利用

2023-03-06 16:31:59

了如何通过FPGA实现RS 232接口的时序逻辑设计。关键词:FPGA;时序电路;RS 232;串行通信

2019-06-19 07:42:37

夏宇闻数字逻辑设计,学习FPGA的前提经典功课教程。

2013-02-06 21:45:42

本文使用符合PCI电气特性的FPGA芯片进行简化的PCI接口逻辑设计,实现了33MHz、32位数据宽度的PCI从设备模块的接口功能,节约了系统的逻辑资源,且可以将其它用户逻辑集成在同一块芯片,降低了成本,增加了设计的灵活性。

2021-05-08 08:11:59

前言FPGA 可以实现高速硬件电路,如各种时钟,PWM,高速接口,DSP计算等硬件功能。这是Cortex-M 处理器软件无法比拟的。要实现FPGA 的逻辑设计,对于嵌入式系统工程师又是比较复杂和具有

2021-12-21 06:13:49

本帖最后由 daworencai 于 2016-1-21 14:46 编辑

岗位职责:1.负责部门存储系列产品的逻辑设计开发工作;2.负责存储系列产品的BCH算法优化、高速存储技术实现等;负责

2016-01-21 14:42:39

数字电路与逻辑设计数字逻辑电路的分析和方法,常用集成数字逻辑电路的功能和应用;主要内容包括:逻辑代数基础、组合逻辑电路分析和设计、常用组合逻辑电路及MSI组合电路模块的应用,时序逻辑电路的分析

2021-08-06 07:33:41

。

但是和所有的数字电路一样,FPGA 电路中也存在毛刺问题。它的出现会影响电路工作的可靠性、稳定性,严重时会导致整个数字系统的误动作和逻辑紊乱。下面就来讨论交流一下FPGA 的竞争冒险与毛刺

2023-05-30 17:15:28

要使用哪种方法去验证 FPGA 的逻辑设计?FPGA的优缺点是什么?

2021-04-08 06:57:32

消除组合逻辑产生的毛刺—PLD设计技巧 Design of Combinational Circuit

What is Combinational Circuit

Combinational Circuit if

2008-09-11 09:34:18 29

29 组合逻辑电路电子教案:数字逻辑电路可分为两大类: 一类叫组合逻辑电路;另一类叫时序逻辑电路。本章首先介绍组合逻辑电路的共同特点和描述方法,然后重点介绍组合逻辑电

2009-09-01 08:58:29 0

0 中规模集成时序逻辑设计:计数器:在数字逻辑系统中,使用最多的时序电路要算计数器了。它是一种对输入脉冲信号进行计数的时序逻辑部件。9.1.1 计数器的分类1.按数制

2009-09-01 09:09:09 13

13 基于PLD芯片的时序逻辑设计与实现:原理图输入设计直观、便捷、操作灵活;1-1、原理图设计方法简介QuartusII已包含了数字电路的基本逻辑元件库(各类逻辑门及触发器),宏

2009-10-29 22:03:10 0

0 本文介绍了一种基于FPGA 的用自定义串口命令的方式实现MDIO 接口逻辑设计的方法,并对系统结构进行了模块化分解以适应自顶向下的设计方法。所有功能的实现全部采用VHDL 进行描

2009-12-26 16:48:44 103

103 电子技术--组合逻辑电路掌握组合逻辑电路的分析方法与设计方法掌握利用二进制译码器和数据选择器进行逻辑设计的方法理解加法器、编码器、译码器等中规模集成电

2010-04-12 17:52:29 0

0 摘要:给出了基于A S M 图的数字集成电路控制器的设计的主要电路实现方法,并给出了目前最常采用的方法——EDA法.关键词: A S M 图; 逻辑设计; E DA; On e Ho t

2010-04-26 11:25:44 14

14 ASIC与大型逻辑设计实习课

AgendaCell Base IC DesignModelSimLibraryProjectVHDL Compiler & SimulationSimulation WindowsTutorialLab

2010-06-19 09:45:20 0

0 目的: 掌握基本组合逻辑电路的实现方法。

2010-07-17 16:29:17 12

12 摘要:简要介绍了现场可编程门阵列(FPGA)的特性,并结合MPEG-2编码复用器开发过程中的经验,给出了在MAX+ PLUS II提供的设计环境下FPGA逻辑设计的

2006-05-26 21:52:22 1039

1039

基本组合逻辑电路

一、 实验目的?⒈ 掌握一般组合逻辑电路的分析和设计方法。?⒉ 熟悉集成优先编码器的逻辑功能及简单应用。

2008-09-24 22:14:03 2886

2886 组合逻辑电路的分析与设计-逻辑代数

在任何时刻,输出状态只决定于同一时刻各输入状态的组合,而与先前状态无关的逻辑电路称为组合逻辑电路。

2009-04-07 10:07:57 3922

3922

组合逻辑电路的分析

分析组合逻辑电路的目的是为了确定已知电路的逻辑功能,其步骤大致如下: 1.由逻辑图写出各输出端的逻辑表达式; 2.化简和变换各

2009-04-07 10:11:55 8346

8346

组合逻辑电路的设计

组合逻辑电路的设计与分析过程相反,其步骤大致如下: (1)根据对电路逻辑功能的要求,列出真值表; (2)由真值表写出逻辑表达

2009-04-07 10:12:22 14015

14015

组合逻辑电路中的竞争冒险

前面分析组合逻辑电路时,都没有考虑门电路的延迟时间对电路产生的影响。实际上,从信号输入到稳定输出需要一定的时间。由于从输入

2009-04-07 10:13:03 11802

11802

摘要:简要介绍了现场可编程门阵列(FPGA)的特性,并结合MPEG-2编码复用器开发过程中的经验,给出了在MAX+ PLUS II提供的设计环境下FPGA逻辑设计的一些方法和技巧。设计的逻

2009-06-20 14:40:35 784

784

组合逻辑中的竞争与冒险及毛刺的处理方法 在组合逻辑中,由于门的输入信号通路中经过了不同的延时,导致到达该门的时间不一致叫竞争。产生毛刺叫冒险。如果布尔式中有相反的信号则可能产生竞争和冒险现象。解决方法:一是添加布尔式的(冗余)消去项,但是不

2011-01-24 18:12:53 0

0 组合逻辑设计实例_国外:

2011-12-16 15:08:59 24

24 《数字电路与逻辑设计》答案

2012-06-25 08:19:15 23

23 多分辨率图像实时采集系统的FPGA逻辑设计

2016-08-29 15:02:03 6

6 组合逻辑中的竞争与冒险及毛刺的处理方法

2017-01-17 19:54:24 7

7 和所有的数字电路一样,毛刺也是FPGA电路中的棘手问题,它的出现会影响电路工作的稳定性,可靠性,严重时会导致整个数字系统的误动作和逻辑紊乱。

2017-02-11 03:59:38 2361

2361

使用标准集成电路的逻辑设计课题

2017-09-19 11:41:06 19

19 数字电路根据逻辑功能的不同特点,可以分成两大类,一类叫组合逻辑电路(简称组合电路),另一类叫做时序逻辑电路(简称时序电路)。组合逻辑电路在逻辑功能上的特点是任意时刻的输出仅仅取决于该时刻的输入

2017-11-20 12:26:21 9235

9235 深入地分析。FPGA以其容量大、功能强以及可靠性高等特点,在现代数字通信系统中得到广泛的应用。采用FPGA设计数字电路已经成为数字电路系统领域的主要设计方式之一。

2017-11-22 14:24:54 10629

10629 逻辑电路按其逻辑功能和结构特点可分为组合逻辑电路和时序逻辑电路。单一的与门、或门、与非门、或非门、非门等逻辑门不足以完成复杂的数字系统设计要求。组合逻辑电路是采用两个或两个以上基本逻辑门来实现更实用、复杂的逻辑功能。

2018-01-30 17:05:44 67767

67767

组合逻辑电路和时序逻辑电路都是数字电路,组合逻辑电路在逻辑功能上的特点是任意时刻的输出仅仅取决于该时刻的输入,与电路原来的状态无关。而时序逻辑电路在逻辑功能上的特点是任意时刻的输出不仅取决于当时的输入信号,而且还取决于电路原来的状态,或者说,还与以前的输入有关。

2018-01-30 17:26:04 94951

94951

本文档的主要内容详细介绍的是FPGA视频教程之FPGA设计中时序逻辑设计要点的详细资料说明免费下载。

2019-03-27 10:56:04 20

20 本课程以目前流行的Xilinx 7系列FPGA的开发为主线,全面讲解FPGA的原理及电路设计、Verilog HDL语言及VIVADO的应用,并循序渐进地从组合逻辑、时序逻辑的开发开始,深入到FPGA的基础应用、综合应用和进阶应用。

2019-12-05 07:08:00 3476

3476

组合逻辑电路是无记忆数字逻辑电路,其任何时刻的输出仅取决于其输入的组合.

2019-06-22 10:53:20 50945

50945

本文档的主要内容详细介绍的是Verilog HDL语言组合逻辑设计方法以及QuartusII软件的一些高级技巧。

2019-07-03 17:36:12 20

20 组合逻辑电路的设计就是将实际的,有因果关系的问题用一个较合理、经济、可靠的逻辑电路来实现。一般来说在保证速度、稳定、可靠的逻辑正确的情况下,尽可能使用最少的器件,降低成本是逻辑设计者的任务。本文将

2020-01-21 16:46:00 3470

3470

组合逻辑设计法适合于设计开关量控制程序,它是对控制任务进行逻辑分析和综合,将元件的通、断电状态视为以触点通、断状态为逻辑变量的逻辑函数,对经过化简的逻辑函数,利用PLC逻辑指令可顺利地设计出满足要求且较为简练的程序。这种方法设计思路清晰,所编写的程序易于优化。

2020-05-22 08:49:00 4637

4637 本文档的主要内容详细介绍的是数字电路与逻辑设计实验报告模板。

2020-06-05 08:00:00 8

8 组合逻辑电路是指在任何时刻,输出状态只决定于同一时刻各组合逻辑电路输入状态的组合,而与电路以前状态无关而与其他时间的状态无关。如:加法器、编码器、译码器、选择器等

2020-12-09 14:49:02 12

12 本文档的主要内容详细介绍的是华为FPGA硬件的静态时序分析与逻辑设计包括了:静态时序分析一概念与流程,静态时序分析一时序路径,静态时序分析一分析工具

2020-12-21 17:10:54 22

22 一、逻辑设计 (1)组合逻辑设计 下面是一些用Verilog进行组合逻辑设计时的一些注意事项: ①组合逻辑可以得到两种常用的RTL 级描述方式。第一种是always 模块的触发事件为电平敏感信号列表

2021-06-23 17:45:10 6056

6056

和所有的数字电路一样,毛刺也是FPGA电路中的棘手问题,它的出现会影响电路工作的稳定性,可靠性,严重时会导致整个数字系统的误动作和逻辑紊乱。

2022-08-25 09:01:52 2434

2434 组合逻辑电路的特点是输入的变化直接反映了输出的变化,其输出的状态仅取决于输入的当前状态,与输入、输出的原始状态无关。如果从电路结构上来讲,组合逻辑电路是没有触发器组件的电路。

2022-10-24 16:02:32 1770

1770 我在数字逻辑设计方面并没有经验。也就是说,直到最近我才决定尝试设计自己的 CPU,并在 FPGA 上运行!如果你也是一名软件工程师,并对硬件设计有兴趣,那么我希望这一系列关于我所学到的知识的文章能够对你有所帮助,并让你感到有趣。本系列文章的第一部分中,将回答以下问题:

2022-11-01 09:25:03 2703

2703 上文中我们指出,不管我们是创建自定义 ASIC 芯片还是配置 FPGA,都可以使用相同的数字逻辑设计工具。

2022-11-01 09:23:39 3201

3201 本文介绍开发组合逻辑电路时可能发生的意外开关事件,称为危险。 本文是关于使用逻辑门进行组合电路设计和仿真的介绍性系列文章的第二部分。在上一篇文章中,我们介绍了 组合逻辑电路 以及如何简化它们

2023-01-27 14:18:00 2709

2709

数字电路中的组合逻辑电路的设计与分析过程相反,本文小编主要跟大家介绍一下关于组合逻辑电路的设计步骤,顺便回顾一下组合逻辑电路的分析方法。

2023-02-03 09:56:23 8000

8000 所谓组合逻辑电路的分析,就是根据给定的逻辑电路图,求出电路的逻辑功能。

2023-03-06 14:37:26 5871

5871 电子发烧友网站提供《在Artix 7 FPGA上使用Vivado的组合逻辑与顺序逻辑.zip》资料免费下载

2023-06-15 09:14:49 0

0 CMOS成像系统是基于CMOS图像传感器的一种适用于机载应用环境的图像采集系统。可有效解决机载复杂环境下常规工业相机的各种缺陷和应用问题,满足市场的应用需求。 FPGA 逻辑设计是车载CMOS成像系统的关键设计,本文将探讨关于的CMOS图像传感器的FPGA逻辑

2023-09-19 10:15:02 2869

2869

当逻辑电路由多个逻辑门组成且不含存储电路,对于给定的输入变量组合将产生确定的输出,则这种逻辑电路称为组合逻辑电路。

2024-02-04 11:46:36 3337

3337

组合逻辑电路和时序逻辑电路是数字电路中两种重要的逻辑电路类型,它们主要区别在于其输出信号的依赖关系和对时间的敏感性。

2024-02-04 16:00:27 7168

7168 电子发烧友网站提供《数字电路与逻辑设计.ppt》资料免费下载

2024-03-11 09:21:44 12

12 电子发烧友网站提供《基于VHDL的组合逻辑设计.ppt》资料免费下载

2024-03-11 09:23:29 2

2 一、引言 组合逻辑电路是数字电路中的重要组成部分,它仅由逻辑门电路(如与门、或门、非门等)和输入/输出端组成,不包含任何存储元件。组合逻辑电路的输出仅取决于当前的输入信号,与电路的历史状态无关。因此

2024-07-30 14:38:04 3066

3066 组合逻辑电路是数字电路中的一种基本类型,它由逻辑门组成,根据输入信号的组合产生相应的输出信号。组合逻辑电路广泛应用于计算机、通信、控制等领域。设计组合逻辑电路需要遵循一定的步骤,以确保电路的正确性

2024-07-30 14:39:55 2311

2311

电子发烧友App

电子发烧友App

评论