表。 这4类路径中,我们最为关心是②的同步时序路径,也就是FPGA内部的时序逻辑。 时序模型 典型的时序模型如下图所示,一个完整的时序路径包括源时钟路径、数据路径和目的时钟路径,也可以表示为触发器+组合逻辑+触发器的模型。 该

2020-11-17 16:41:52 3687

3687

习时把这一章分为两节,它们分别是:§5、1 时序电路的概述§5、2 触发器 5、1 时序电路的概述 这一节我们来学习一些关于时序电路的概念,在学习时要注意同步时序电路和异步时序电路的区别一:时序

2018-08-23 10:36:20

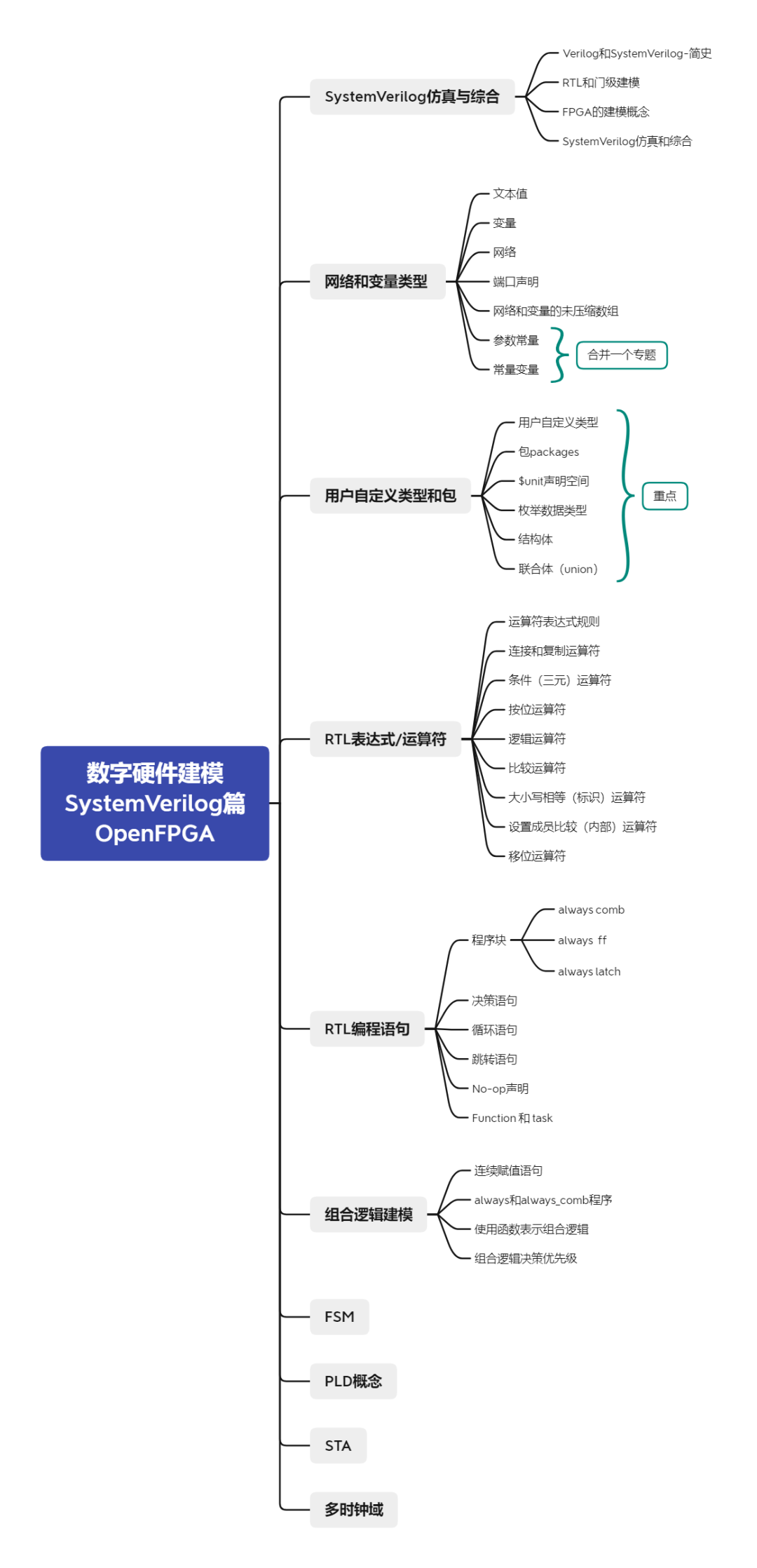

时序逻辑电路设计6.1 基本D触发器的设计6.2 JK触发器6.3 带异步复位/置位端的使能T触发器6.4 基本计数器的设计6.5 同步清零的计数器6.6 同步清零的可逆计数器6.7 同步预置数的计数器

2009-03-20 10:04:53

触发器PPT电子教案:触发器是构成时序逻辑电路的基本逻辑部件。? 它有两个稳定的状态:0状态和1状态;? 在不同的输入情况下,它可以被置成0状态或1状态;? 当输入信号消失后,所置成的状态能够保持

2009-09-16 16:06:45

触发器实验1)熟悉常用触发器的逻辑功能及测试方法。2)了解触发器逻辑功能的转换。三.实验内容及步骤 (1) 基本RS触发器逻辑功能测试(2) JK触发器逻辑功能测试(3) D触发器逻辑功能的测试

2009-03-20 10:01:05

边沿型触发器的输出有两个稳定状态: 高电平或者低电平。为保证可靠操作, 必须要满足触发器的时序要求,也就是我们熟知的建立时间和保持时间。如果输入信号违反了触发器的时序要求, 那么触发器的输出信号就有

2012-12-04 13:51:18

同步复位D触发器复位信号在所需时钟边沿才有效,复位操作需要同步于时钟故称作同步复位。代码如下[code]module d_ff (input clk,input rst_n,input D

2012-03-05 14:02:11

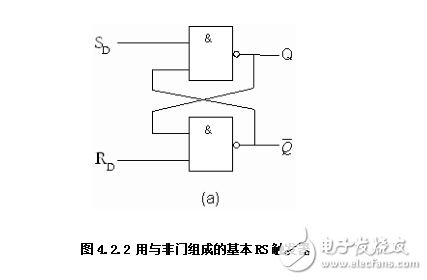

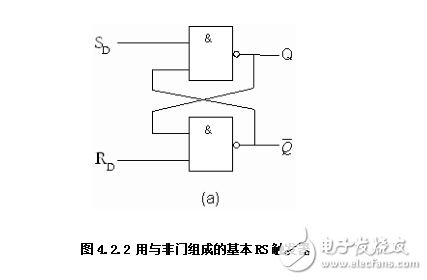

基本的SR NAND触发器电路具有许多优点,并在顺序逻辑电路中使用,但是它存在两个基本的开关问题。1.必须始终避免设置= 0和复位= 0条件(S = R = 0)2.如果在启用(EN)输入为高时设置

2021-02-01 09:15:31

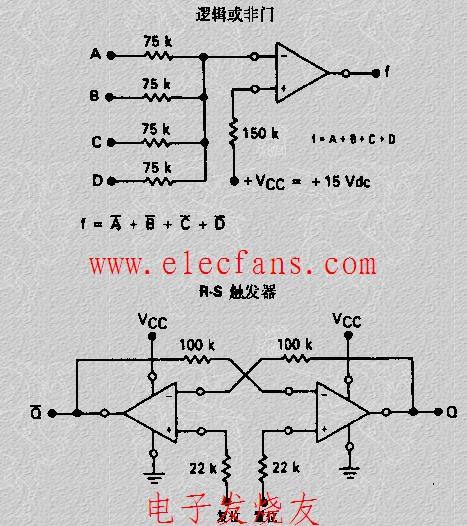

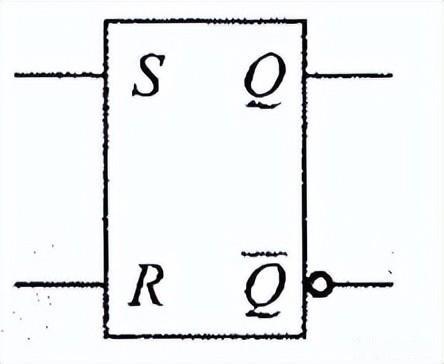

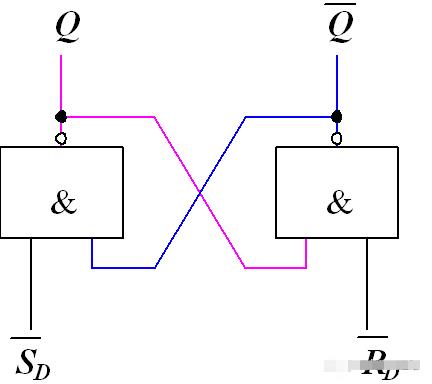

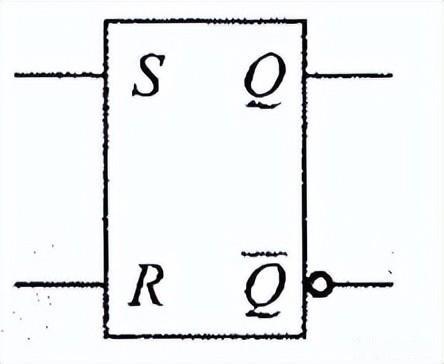

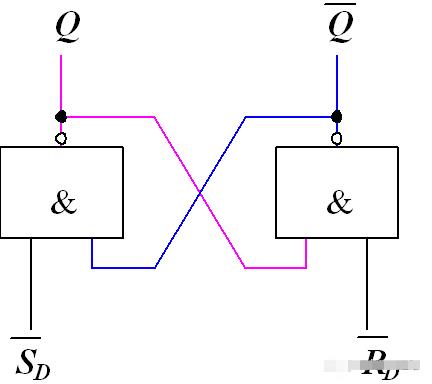

R-S触发器是最基本的一种触发器,它由两个“与非”门组成。它有两个输入端,分别称为置“0”端(也称为复位端、R端)和置“1”端(也称为置位端、S端);它有两个输出端,分别称为Q端和Q端。并且规定:当

2019-12-25 17:21:56

专用的全局时钟输入引脚驱动单个主时钟去控制设计项目中的每一个触发器。同步设计时, 全局时钟输入一般都接在器件的时钟端,否则会使其性能受到影响。 对于需要多时钟的时序电路, 最好选用一个频率是它们

2012-03-05 14:29:00

、加/减计数器,又称可逆计数器。按计数器中触发器翻转是否同步可分为:异步计数器和同步计数器 。2.寄存器寄存器是存放数码、运算结果或指令的电路,移位寄存器不但可存放数码,而且在移位脉冲作用下,寄存器中

2016-10-25 23:03:31

什么是同步逻辑和异步逻辑?同步电路和异步电路的区别在哪?为什么触发器要满足建立时间和保持时间?什么是亚稳态?为什么两级触发器可以防止亚稳态传播?

2021-08-09 06:14:00

本文来自芯社区,谢谢。1:什么是同步逻辑和异步逻辑? 同步逻辑是时钟之间有固定的因果关系。异步逻辑是各时钟之间没有固定的因果关系。 同步时序逻辑电路的特点:各触发器的时钟端全部连接在一起,并接在系统

2021-07-26 08:26:57

寄存器,由寄存器又可以组成存储器。触发器是由基本逻辑门电路构成的,它有两种输出稳定状态,称作为“1”状态和“0”状态,分别代表它所寄存的代码为“1”和“0”;它有两个输入端,用于接收代码“1”和“0

2019-12-25 17:09:20

触发器没有使用相同的时钟信号,需要分析哪些触发器时钟有效哪些无效分析步骤和同步时序电路一样,不过要加上时钟信号有关D触发器的例题抄自慕课上的一个题目,注意第二个触发器反相输出端同时连接到复位端JK

2021-09-06 08:20:26

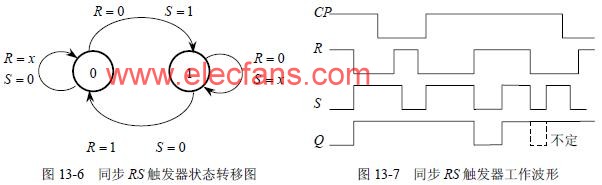

新课第五章 触发器5.1 概述1、触发器具有“记忆”功能,它是构成时序逻辑电路的基本单元。本章首先介绍基本RS触发器的组成原理、特点和逻辑功能。然后引出能够防止“空翻”现象的主从触发器和边沿触发器。同时,较详细地讨论RS触发器、JK触发器、D触发器、T触发器、T'触发器的逻辑功能及其描述方法。

2009-04-02 11:58:41

触发器是构成时序逻辑电路的基本单元电路。

触发器具有记忆功能,能存储一位二进制数码。

2025-03-26 14:21:19

RTL模型综合结果。示例5-6:使用归约运算符:使用异或的奇偶校验//// Book, "RTL Modeling with SystemVerilog for ASIC and FPGA

2022-10-20 15:03:15

一、实验目的1、掌握基本RS、JK、D和T触发器的逻辑功能2、掌握集成触发器的逻辑功能及使用方法3、熟悉触发器之间相互转换的方法二、实验原理触发器具有两个稳

2008-12-19 00:40:23 49

49 实验五 触发器逻辑功能测试一、 实验目的1、 熟悉并掌握RS、D、JL触发器的构成、工作原理和功能测试方法2、 学会正确使用触发器集成芯片二、 实

2009-03-20 17:56:32 108

108 同步时序逻辑电路:本章系统的讲授同步时序逻辑电路的工作原理、分析方法和设计方法。从同步时序逻辑电路模型与描述方法开始,介绍同步时序逻辑电路的分析步骤和方法。然后

2009-09-01 09:06:27 0

0 提出了从状态转换图中直接求得触发器的置位和复位函数,从而确定触发器的驱动方程这样一种设计同步时序逻辑电路的新方法.设计原理简单,易于理解,适合于所有同步时序

2010-02-28 19:23:02 15

15 5.1 基本RS触发器5.2 时钟控制的触发器5.3 集成触发器5.4 触发器的逻辑符号及时序图

2010-08-10 11:53:23 0

0 触发器是时序逻辑电路中完成记忆功能的电路,是最基本的时序逻辑电路。

2010-08-12 16:20:24 0

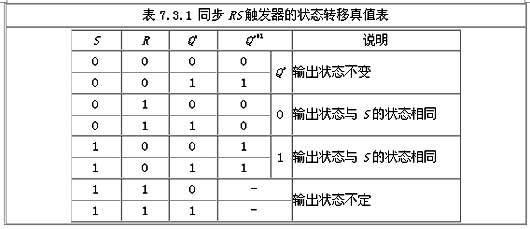

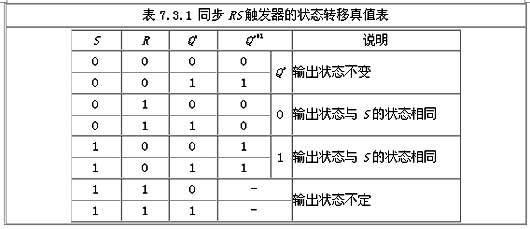

0 教学目标:1、 掌握钟控同步RS触发器的电路组成2、 掌握钟控同步RS触发器的工作原理及逻辑功能3、 了解触发器的应用教学重难点:重点:钟控同步 RS 触

2010-08-18 14:57:41 16

16 一、基本要求1、理解R-S触发器、J-K触发器和D触发器的逻辑功能;2、掌握触发器构成的时序电路的分析,并了解其设计方法;3、理解计数器和寄存器的概念和功能,并掌握它

2010-08-26 11:40:22 57

57 组合电路和时序电路是数字电路的两大类。门电路是组合电路的基本单元;触发器是时序电路的基本单元。

2010-08-29 11:29:04 67

67 触发器是时序逻辑电路的基本构成单元,按功能不同可分为 RS 触发器、 JK 触发器、 D 触发器及 T 触发器四种,其功能的描述可以使用功能真值表、激励表、状态图及特性方程。

2010-09-30 16:03:26 90

90

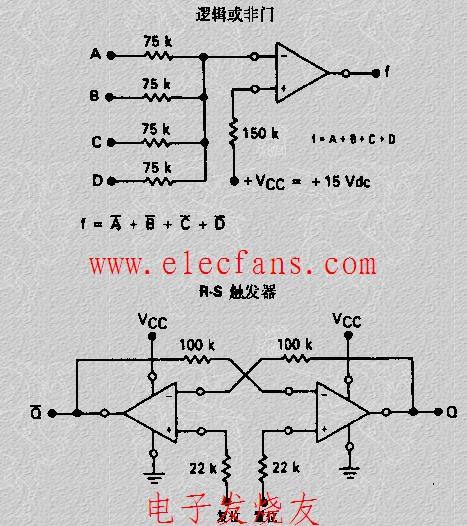

逻辑或非门-RS触发器电路

2008-06-12 23:24:00 2898

2898

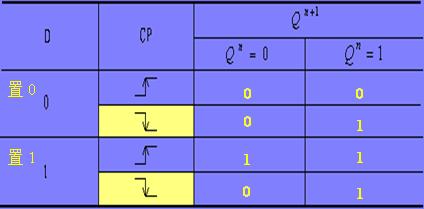

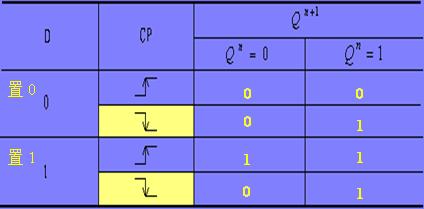

D触发器

同步式D触发器逻辑电路图

D触发器功能

2008-10-20 09:57:54 2818

2818

同步式D触发器逻辑电路图

2008-10-20 09:58:19 9218

9218

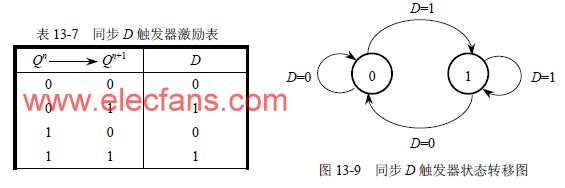

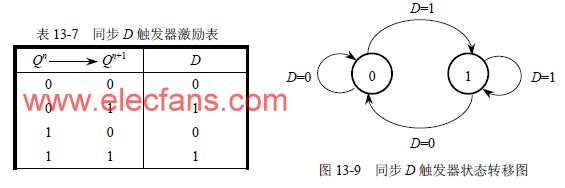

D触发器逻辑功能表

同

2009-03-18 20:13:59 48810

48810

触发器

一、 实验目的

1. 学会测试触发器逻辑功能的方法。 2. 进一步熟悉RS触发器

2009-03-28 10:02:34 11216

11216

4.2.2 同步触发器二、同步D触发器1.电路结构2.逻辑功能3.特性方程4.状态转换图三、同步JK触发器1.电路结构2.逻辑功能3.特性方程4.状态转换

2009-03-30 16:17:07 5250

5250

第二十七讲 同步时序逻辑电路的设计

7.5 同步时序逻辑电路的设计用SSI触发器16进制以内7.5.1 同步时序逻辑电路的设计方法

2009-03-30 16:31:56 4192

4192

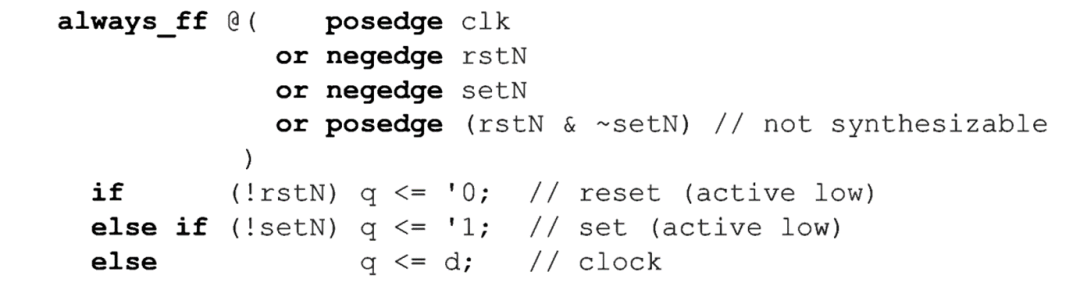

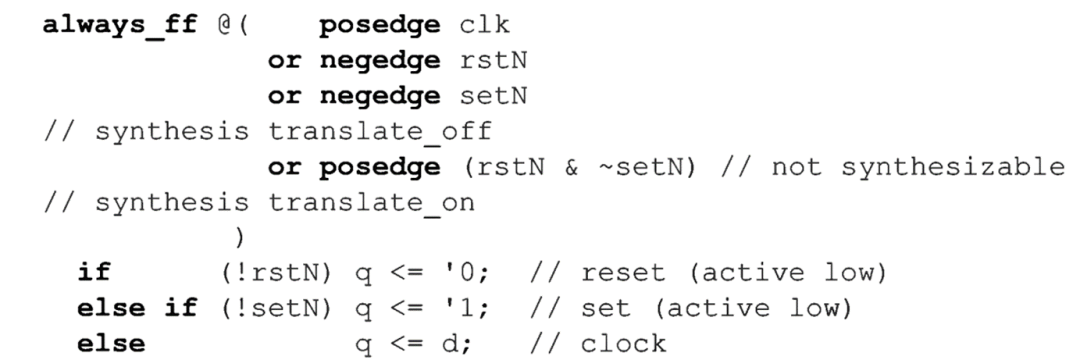

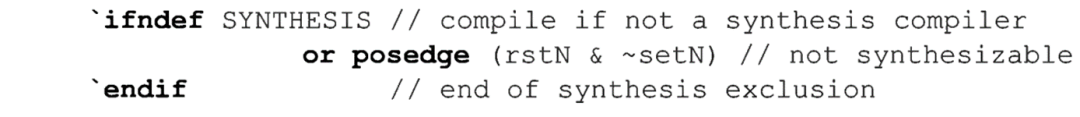

Verilog HDL语言实现时序逻辑电路

在Verilog HDL语言中,时序逻辑电路使用always语句块来实现。例如,实现一个带有异步复位信号的D触发器

2010-02-08 11:46:43 5099

5099 时序逻辑电路实例解析

一、触发器 1、电位触发方式触发器

2010-04-15 13:46:25 6161

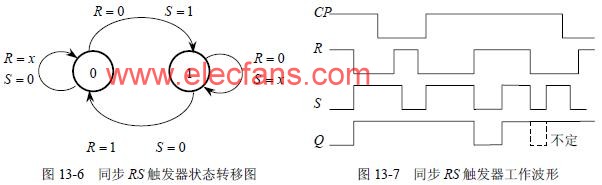

6161 由与非门构成的同步RS触发器如图13-5(a)所示,其逻辑符号如图13-5(b)所示。图中门A和B构成基本触发器,门C和E构成触发引导电路。由图13-5(a)可见,基本触发器的输

2010-08-18 09:00:00 17146

17146

为了避免同步RS触发器的输入信号同时为1,可以在S和R之间接一个“非门”,信号只从S端输入,并将S端改称为数据输入端D,如图15-8所示。这种单输入的触发器称为

2010-08-18 09:06:00 13148

13148

一、空翻问题由于在CP=1期间,同步触发器的触发引导门都是开放的,触发器都可以接收输入信号而翻转,所以在CP=1期间,如果输入信号发生多次变化,触发器的

2010-08-18 09:08:32 22815

22815

本次重点内容:1、触发器的概念和分类。2、同步触发器、主从触发器、边沿触发器的含义。

4.1.1 触发器概述一、触发

2010-08-19 08:57:47 20522

20522 0 引言 触发器是具有存储功能的器件,在数字电子技术中用于构成各种时序逻辑电路。触发器有多

2010-10-11 10:20:17 15534

15534 触发器是一个具有记忆功能的,具有两个稳定状态的信息存储器件,是构成多种时序电路的最基本逻辑单元,也是数字逻辑电路中一种重要的单元电路。在数字系统和计算机中有着广泛的应用。触发器具有两个稳定状态,即“0”和“1”,在一定的外界信号作用下,可以从一个稳定状态翻转到另一个稳定状态。

2017-08-19 09:21:00 17038

17038

触发器是一个具有记忆功能的,具有两个稳定状态的信息存储器件,是构成多种时序电路的最基本逻辑单元,也是数字逻辑电路中一种重要的单元电路。在数字系统和计算机中有着广泛的应用。触发器具有两个稳定状态.

2017-11-02 08:53:42 61658

61658 触发器是一个具有记忆功能的,具有两个稳定状态的信息存储器件,是构成多种时序电路的最基本逻辑单元,也是数字逻辑电路中一种重要的单元电路。在数字系统和计算机中有着广泛的应用。触发器具有两个稳定状态

2017-12-12 17:20:40 86395

86395

按照稳定工作状态分,可分为双稳态触发器、单稳态触发器、无稳态触发器(多谐振荡器)等;按照逻辑功能划分,可分为RS触发器、D触发器、T触发器、JK触发器等几类;按照电路结构划分,可分为基本RS触发器、同步触发器(时钟控制的触发器)、主从型触发器、维持-阻塞型触发器和边沿触发器等几种类型。

2018-01-31 15:02:50 29042

29042

时序逻辑电路是由组合逻辑电路与记忆电路(又称存储电路) 组合而成的。 常见时序逻辑电路有触发器、 寄存器和计数器等。

2019-02-26 15:25:01 52417

52417 将驱动方程代入相应触发器的特性方程中,便得到该触发器的次态方程。时序逻辑电路的状态方程由各触发器次态的逻辑表达式组成。

2019-02-28 14:06:14 25600

25600 D触发器是一个具有记忆功能的,具有两个稳定状态的信息存储器件,是构成多种时序电路的最基本逻辑单元,也是数字逻辑电路中一种重要的单元电路。

2019-12-02 07:06:00 8199

8199

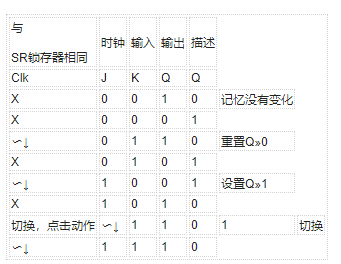

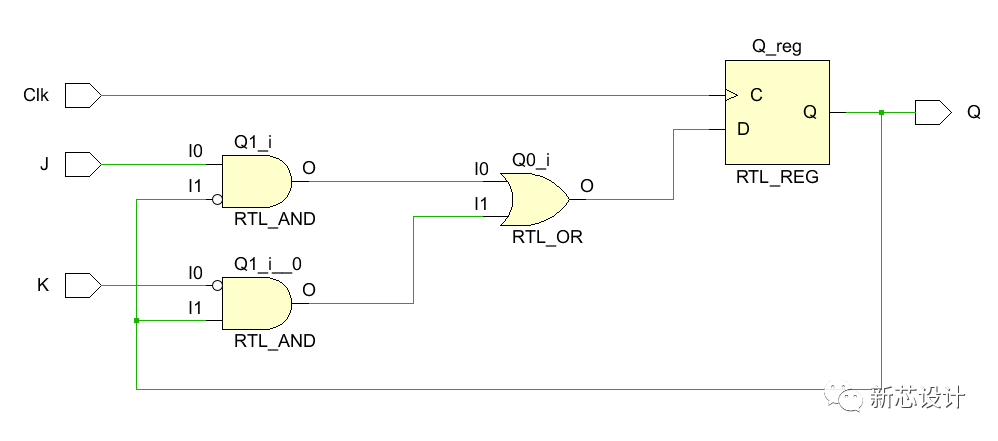

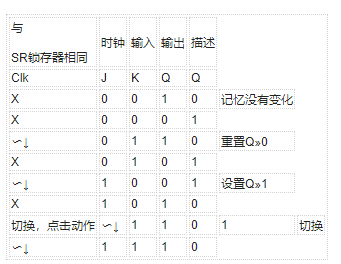

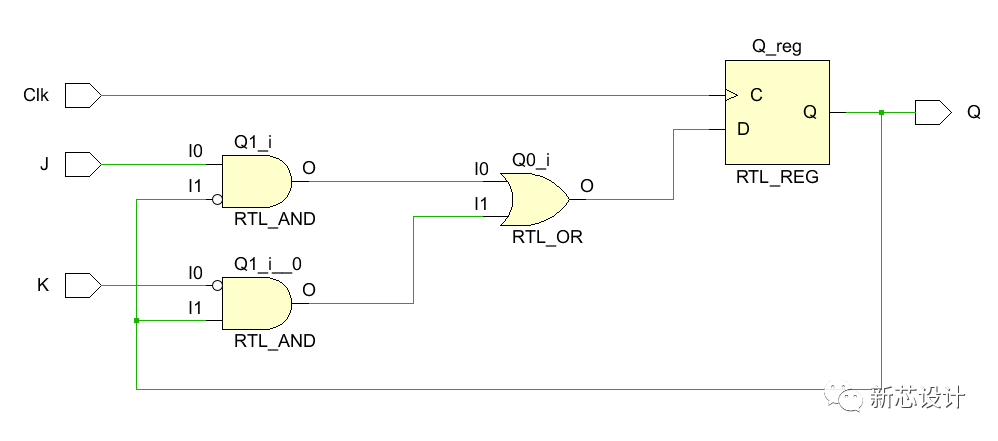

JK触发器类似于SR触发器,但当J和K输入均为低电平时,状态没有变化,JK触发器的顺序操作与前一个具有相同“设置”和“复位”输入的SR触发器完全相同。这次的不同之处在于,即使 S 和 R 都处于逻辑“1”,“JK触发器”也没有SR Latch的无效或禁止输入状态。

2019-06-26 15:56:51 7221

7221

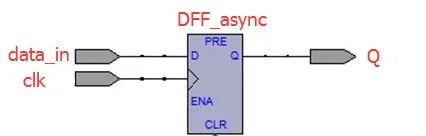

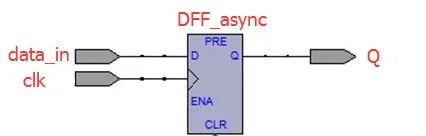

首选我们来聊聊时序逻辑中最基础的部分D触发器的同步异步,同步复位即复位信号随系统时钟的边沿触发起作用,异步复位即复位信号不随系统时钟的边沿触发起作用,置数同理,rst_n表示低电平复位,我们都知道D

2019-07-26 10:17:16 27982

27982

JK触发器是数字电路触发器中的一种基本电路单元。JK触发器具有置0、置1、保持和翻转功能,在各类集成触发器中,JK触发器的功能最为齐全。在实际应用中,它不仅有很强的通用性,而且能灵活地转换其他类型的触发器。由JK触发器可以构成D触发器和T触发器。

2019-11-08 14:48:44 96918

96918

产生毛刺,且易受环境的影响,不利于器件的移植; 同步电路 1. 电路的核心逻辑是由各种各样的触发器实现的,所以比较容易使用寄存器的异步复位/置位端,以使整个电路有一个确定的初始状态; 2. 整个电路是由时钟沿驱动的; 3. 以触发器为主体的同步时序电

2020-12-05 11:53:41 12647

12647 复位/置位触发器(R、S分别是英文复位,置位的缩写)也叫做基本R-S触发器,是最简单的一种触发器,是构成各种复杂触发器的基础。

2021-06-30 17:13:06 116513

116513

没有任何寄存器逻辑,RTL设计是不完整的。RTL是寄存器传输级或逻辑,用于描述依赖于当前输入和过去输出的数字逻辑。

2022-03-15 10:56:04 4623

4623 明德扬有完整的时序约束课程与理论,接下来我们会一章一章以图文结合的形式与大家分享时序约束的知识。要掌握FPGA时序约束,了解D触发器以及FPGA运行原理是必备的前提。今天第一章,我们就从D触发器开始讲起。

2022-07-11 11:33:10 6143

6143

复位信号在数字电路里面的重要性仅次于时钟信号。对一个芯片来说,复位的主要目的是使芯片电路进入一个已知的,确定的状态。主要是触发器进入确定的状态。在一般情况下,芯片中的每个触发器都应该是可复位的。

2022-09-19 10:07:20 35609

35609 什么是RS触发器 其中R、S分别是英文复位 Reset 和置位 Set 的缩写,作为最简单的一种触发器,是构成各种复杂触发器的基础。RS触发器的逻辑电路图如下图所示。 RS触发器可以用与非门实现或者

2022-10-19 17:49:59 15092

15092

SystemVerilog有三种在可综合RTL级别表示组合逻辑的方法:连续赋值语句、always程序块和函数。接下来几篇文章将探讨每种编码风格,并推荐最佳实践编码风格。

2022-12-07 15:31:47 2361

2361 其中R、S分别是英文复位Reset和置位Set的缩写,作为最简单的一种触发器,是构成各种复杂触发器的基础。RS触发器的逻辑电路图如下图所示。

2023-02-08 09:19:45 11327

11327 带复位功能的双 JK 触发器;下降沿触发-74HC73

2023-02-15 19:33:13 3

3 带复位功能的双 JK 触发器;下降沿触发-74HC_HCT107

2023-02-16 19:58:24 2

2 时序逻辑的代码一般有两种: 同步复位的时序逻辑和异步复位的时序逻辑。在同步复位的时序逻辑中复位不是立即有效,而在时钟上升沿时复位才有效。 其代码结构如下:

2023-03-21 10:47:07 1239

1239 在电路中,触发器(Flip-flop)是一种组合逻辑电路,可以存储1个二进制位的信息。 触发器有两个稳定的状态:SET(置位)和RESET(复位)。 当输入信号满足某些条件时,触发器可以从一个状态转换到另一个状态。

2023-03-23 11:45:39 16377

16377

触发器是构成时序逻辑电路的基本单元。它是一种具有记忆功能,能储存1位二进制信息的逻辑电路。在之前的文章中已经介绍过触发器了,这里再介绍一下其他类型的触发器。

2023-03-23 15:13:26 19700

19700

本文旨在总结近期复习的数字电路D触发器(边沿触发)的内容。

2023-05-22 16:54:29 22343

22343

时序逻辑电路分析和设计的基础是组合逻辑电路与触发器,所以想要分析和设计,前提就是必须熟练掌握各种常见的组合逻辑电路与触发器功能,尤其是各种触发器的特征方程与触发模式,因此前几文的基础显得尤为重要。 本文主要介绍时序逻辑电路的分析方法。

2023-05-22 18:24:31 5502

5502

异步复位触发器则是在设计触发器的时候加入了一个复位引脚,也就是说**复位逻辑集成在触发器里面**。(一般情况下)低电平的复位信号到达触发器的复位端时,触发器进入复位状态,直到复位信号撤离。带异步复位的触发器电路图和RTL代码如下所示:

2023-05-25 15:57:17 1867

1867

RS触发器是一种常见的数字逻辑门电路元件,它由两个相互反馈的逻辑门组成。RS触发器的逻辑功能可以描述为存储器元件或双稳态开关。

2023-08-07 16:17:32 18971

18971 zabbix触发器表达式 基本RS触发器表达式 rs触发器的逻辑表达式 Zabbix是一款开源的监控软件,它能通过监控指标来实时监测服务器和网络的运行状态,同时还能提供警报和报告等功能来帮助管理员

2023-08-24 15:50:08 2335

2335 触发器(Flip-Flop)是数字电路中的一种时序逻辑元件,用于存储二进制位的状态。它是数字电路设计中的基本构建块之一,常用于存储数据、实现状态机、控制信号的生成等。触发器可以看作是一种特殊

2023-08-31 10:50:19 20343

20343

在数字电路中,RS触发器(也称为RS锁存器)是一种基本的双稳态触发器,它可以通过特定的输入信号来实现置位(Set)和复位(Reset)操作。

2023-09-28 16:31:07 11269

11269 D触发器,是时序逻辑电路中必备的一个基本单元,学好 D 触发器,是学好时序逻辑电路的前提条件,其重要性不亚于加法器,二者共同构成数字电路组合、时序逻辑的基础。

2023-10-09 17:26:57 6026

6026

JK 触发器的 Verilog 代码实现和 RTL 电路实现

2023-10-09 17:29:34 6642

6642

的逻辑功能及其应用。 首先,RS触发器的逻辑功能包括两个主要部分:设置和复位。设置输入(S)用于设置触发器的输出为“1”,即存储1的功能;复位输入(R)用于复位触发器的输出为“0”,即清零的功能。RS触发器的逻辑功能可以通过其

2023-11-17 16:01:56 7552

7552 RS触发器是一种经典的数字逻辑电路元件,用于存储和控制信息流。它是由两个反馈作用的逻辑门组成,常用于时序电路和数据存储。 RS触发器由两个互补的输出Q和~Q组成,其中Q表示触发器的状态为"1",~Q

2023-11-17 16:14:28 4298

4298 端的状态。在本文中,我将详细介绍置位和复位的含义、功能和应用。 首先,让我们来解释置位和复位的意思。在RS触发器中,置位就是将输出端Q置为高电平(逻辑1),而复位则是将输出端Q置为低电平(逻辑0)。当R和S输入均为逻辑0时,无论之前输出是什么,触发器

2023-11-17 16:19:45 10681

10681 电子发烧友网站提供《rs触发器的逻辑功能.zip》资料免费下载

2023-11-20 14:18:26 0

0 回路。在RS触发器中,R和S分别代表复位(Reset)和设置(Set)输入。当RS触发器处于不稳定状态时,这两个输入可以控制其状态改变。 以下是RS触发器的逻辑表达式: Q(t+1) = (S' * Q(t)) + (R * Q'(t)) 其中,Q(t+1)是触发器的下一个状态,表示在时间

2024-01-12 14:09:48 4551

4551 如果只做一级触发器同步,如何? 一级触发器同步是指只考虑最基础的触发信息进行同步,而不考虑更高层次的关联触发信息。在这篇文章中,我将详细介绍一级触发器同步的概念、原理、应用和局限性,以及一些相关

2024-01-16 16:29:35 1027

1027 RS触发器是一种基本的数字逻辑电路,它由两个互补的反馈连接组成。RS触发器可以用作其他高级逻辑电路的构建模块,如计数器、移位寄存器和内存单元等。本文将详细介绍RS触发器的实现原理、功能和应用。 一

2024-01-17 14:24:17 5885

5885 RS触发器与SR触发器都是基本的数字逻辑电路元件,常用于存储、控制和时序电路中。

2024-01-29 14:15:08 8676

8676 D触发器是一种常见的数字逻辑电路,它在数字系统和计算机中扮演着重要的角色。本文将详细探讨D触发器的逻辑功能、工作原理以及RD(Reset-D)触发器和SD(Set-D)触发器的作用。 首先,我们先来

2024-02-06 13:52:14 52523

52523 触发器是数字电路中常用的组合逻辑电路,在现代电子系统中有着广泛的应用。其中,最常用的两种触发器是T触发器和JK触发器。本文将详细介绍T触发器和JK触发器的区别和联系。 一、T触发器 T触发器是一种单

2024-02-06 14:04:55 7821

7821 的触发器,其输入信号作用于触发器,触发器将根据输入信号进行状态切换。本文将详细介绍如何使用JK触发器构成T触发器,并介绍T触发器的逻辑功能。 一、JK触发器的逻辑功能 JK触发器具有四种基本的逻辑功能,分别是保持、复位、设置和反转。 保持:

2024-02-06 14:11:11 12517

12517 在数字电路设计中,触发器和时序逻辑电路是构建复杂数字系统不可或缺的基础元素。触发器(Flip-Flop)作为基本的存储单元,能够存储一位二进制信息,并在特定的时钟信号控制下更新其状态。而时序逻辑

2024-07-18 17:43:41 4403

4403 JK触发器的置位(Set)和复位(Reset)是其在数字电路中的两种基本状态控制功能,它们在操作原理、输入条件以及触发器输出状态的变化上有所区别。以下是对JK触发器置位和复位的详细分析。

2024-07-27 14:50:54 4926

4926 定义: 主从触发器(Master-Slave Trigger)是一种用于实现时钟同步的触发器结构,它由两个触发器组成,一个为主触发器(Master Trigger),另一个为从触发器(Slave

2024-08-11 09:21:38 2229

2229 在数字电路设计中,触发器是一种非常重要的基本逻辑元件,用于存储一位二进制信息。触发器的种类繁多,但主要分为两大类:主从触发器(Master-Slave Flip-Flop)和边沿触发器

2024-08-11 09:35:02 4850

4850 RS触发器是一种常见的数字逻辑门电路元件,其逻辑功能可以描述为存储器元件或双稳态开关。它由两个相互反馈的逻辑门组成,通常是非门或与非门的组合,具有两个输入端(R和S)和两个输出端(Q和Q')。这里的R和S分别代表“Reset”(复位)和“Set”(置位),它们共同控制触发器的输出状态。

2024-08-12 10:19:04 13909

13909 同步触发器和边沿触发器是数字电路中两种常见的触发器类型,它们在触发方式、工作原理、性能特点以及应用场景等方面存在显著的差异。

2024-08-12 11:26:01 3572

3572 是一种具有记忆功能的数字电路元件,可以存储一位二进制信息。它通常由逻辑门、触发器存储元件和反馈回路组成。触发器的输出状态取决于输入信号和当前状态。 1.2 触发器的分类 触发器按照功能和结构的不同,可以分为多种类型,如SR触发器、JK触

2024-08-22 10:33:51 3765

3765 引言 数字电路是现代电子技术的基础,广泛应用于计算机、通信、控制等领域。触发器是数字电路中的一种基本逻辑元件,具有存储和传递信息的功能。 触发器的基本概念 触发器是一种具有记忆功能的数字电路元件

2024-08-22 10:37:33 5059

5059 JK触发器 :具有四种基本的逻辑功能,分别是保持、复位、设置和反转。这些功能由J和K两个输入端口的信号共同决定。 T触发器 :具有单一的输入端口T,用于控制触发器的状态翻转。当T=1时,触发器在时钟信号的触发下翻转状态;当T=0时,触发器保持当

2024-08-28 09:41:19 6044

6044 边沿JK触发器是一种数字逻辑电路,广泛应用于数字电路设计中。它具有多种功能,包括同步操作、存储数据、实现时序逻辑等。以下是对边沿JK触发器功能的分析: 同步操作 边沿JK触发器是一种同步触发器,它在

2024-08-28 09:50:12 2291

2291 时序逻辑电路是数字电路中的一种重要类型,它具有存储和处理信息的能力。时序逻辑电路的结构特点主要包括以下几个方面: 存储元件 时序逻辑电路中最基本的存储元件是触发器(Flip-flop)。触发器是一种

2024-08-28 11:07:26 1505

1505 状态信息和当前的输入信号来产生输出。 具体来说,时序逻辑电路中的存储电路通常由触发器(Flip-flops)组成,触发器是时序逻辑电路的基本存储单元。触发器可以存储一位二进制信息,并在时钟信号的控制下根据输入信号的变化改变其

2024-08-28 14:12:09 1490

1490 RS触发器(也称为置位/复位触发器)是一种基本的数字逻辑电路,用于存储一位二进制信息。它有两个输入端:置位(Set)和复位(Reset),以及两个输出端:Q和Q'(Q的反相输出)。 RS触发器

2024-10-21 10:03:07 2198

2198 RS触发器(Reset-Set触发器)是一种基本的数字逻辑电路,用于存储一位二进制信息。它由两个输入端(R和S)和一个输出端(Q)组成,其中R代表复位(Reset),S代表置位(Set)。RS触发器

2024-10-21 10:04:23 7434

7434

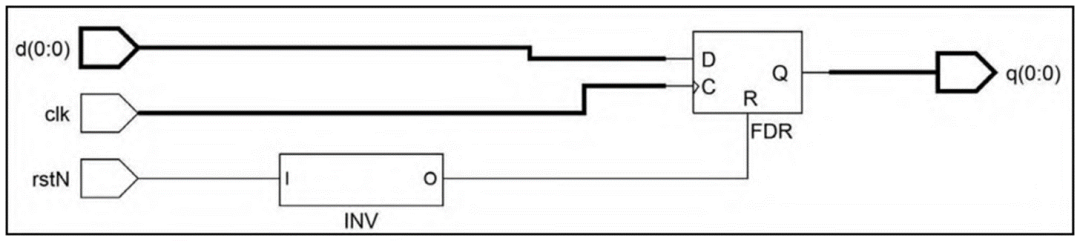

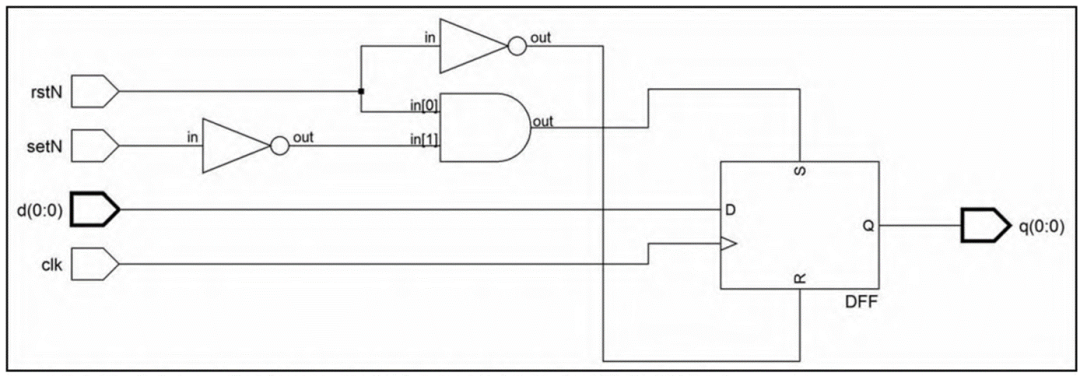

图 8-7: 综合结果。异步复位DFF映射到Xilinx Virtex -7 FPGA中

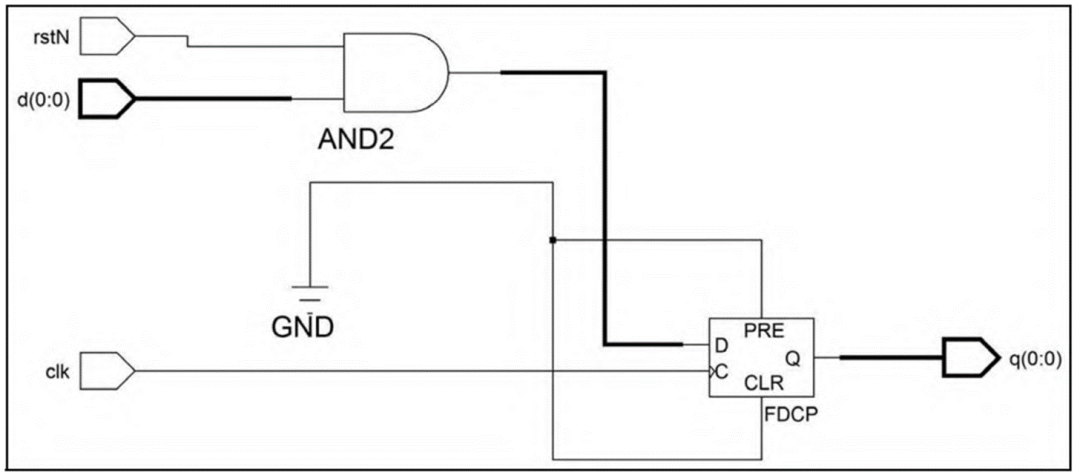

图 8-7: 综合结果。异步复位DFF映射到Xilinx Virtex -7 FPGA中 图8-8:综合结果。映射到Xilinx CoolRunner-11 CPLD的异步复位

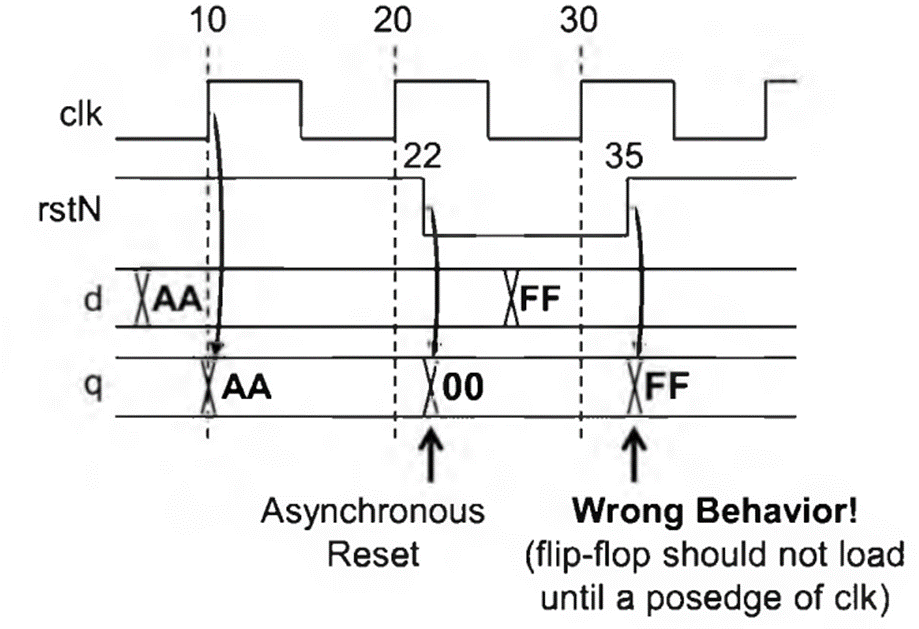

图8-8:综合结果。映射到Xilinx CoolRunner-11 CPLD的异步复位 图8-9:不正确建模的异步复位结果的波形

图8-9:不正确建模的异步复位结果的波形

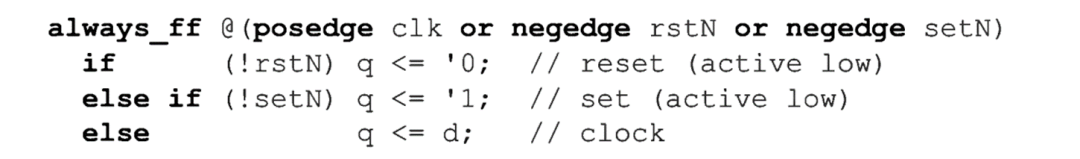

图8-12:一个异步置位-复位触发器的综合结果

图8-12:一个异步置位-复位触发器的综合结果

电子发烧友App

电子发烧友App

评论