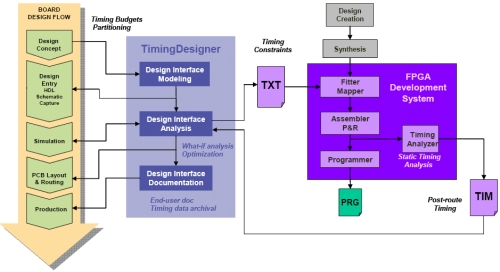

当FPGA设计面临高级接口的设计问题时,该采取什么办法来解决呢?美国EMA公司的TimingDesigner软件可以简化这些设计问题,并提供对几乎

2010-10-28 10:32:49 1100

1100

表。 这4类路径中,我们最为关心是②的同步时序路径,也就是FPGA内部的时序逻辑。 时序模型 典型的时序模型如下图所示,一个完整的时序路径包括源时钟路径、数据路径和目的时钟路径,也可以表示为触发器+组合逻辑+触发器的模型。 该

2020-11-17 16:41:52 2768

2768

在高速系统中FPGA时序约束不止包括内部时钟约束,还应包括完整的IO时序约束和时序例外约束才能实现PCB板级的时序收敛。因此,FPGA时序约束中IO口时序约束也是一个重点。只有约束正确才能在高速情况下保证FPGA和外部器件通信正确。

2022-09-27 09:56:09 1382

1382 FPGA开发过程中,离不开时序约束,那么时序约束是什么?简单点说,FPGA芯片中的逻辑电路,从输入到输出所需要的时间,这个时间必须在设定的时钟周期内完成,更详细一点,即需要满足建立和保持时间。

2023-06-06 17:53:07 860

860

在FPGA设计中,时序约束的设置对于电路性能和可靠性都至关重要。在上一篇的文章中,已经详细介绍了FPGA时序约束的基础知识。

2023-06-06 18:27:13 6213

6213

在FPGA设计中,时序约束对于电路性能和可靠性非常重要。在上一篇的文章中,已经详细介绍了FPGA时序约束的主时钟约束。

2023-06-12 17:29:21 1230

1230 今天跟大家分享的内容很重要,也是调试FPGA经验的总结。随着FPGA对时序和性能的要求越来越高,高频率、大位宽的设计越来越多。在调试这些FPGA样机时,需要从写代码时就要小心谨慎,否则写出来的代码

2023-08-01 09:18:34 1041

1041

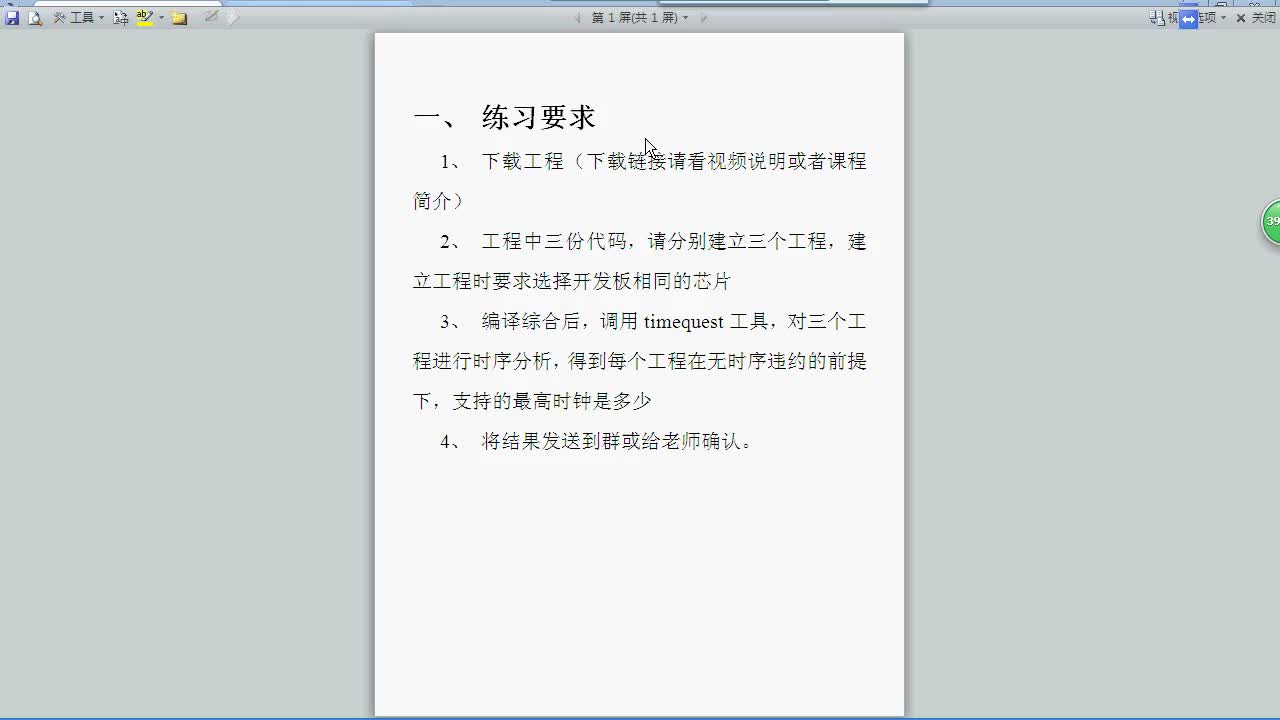

前面讲解了时序约束的理论知识FPGA时序约束理论篇,本章讲解时序约束实际使用。

2023-08-14 18:22:14 842

842

:适合做大块数据的缓冲区。Xlinx 和 LatTI ce FPGA的LUT可以灵活配置成小的RAM、ROM、FIFO等存储结构,这种技术被称为分布式RAM。补充:但是在一般的设计中,不提倡用FPGA

2019-05-04 08:00:00

FPGA CPLFPGA CPLD 数字电路设计经验分享FPGA/CPLD数字电路设计经验分享摘要:在数字电路的设计中,时序设计是一个系统性能的主要标志,在高层次设计方法中,对时序控制的抽象度也相应

2012-08-11 10:17:18

FPGA中几个基本的重要的时序分析参数介绍(fmax\tsu\th\tco\tpd)今天无聊,翻开书偶看到介绍时序部分的东西,觉得其中几个参数缩写所代表的含义应该记住,故写如下文章……FPGA中

2012-04-09 09:41:41

FPGA中的I_O时序优化设计在数字系统的同步接口设计中, 可编程逻辑器件的输入输出往往需要和周围新片对接,此时IPO接口的时序问题显得尤为重要。介绍了几种FPGA中的IPO时序优化设计的方案, 切实有效的解决了IPO接口中的时序同步问题。

2012-08-12 11:57:59

FPGA时序分析系统时序基础理论对于系统设计工程师来说,时序问题在设计中是至关重要的,尤其是随着时钟频率的提高,留给数据传输的有效读写窗口越来越小,要想在很短的时间限制里,让数据信号从驱动端完整

2012-08-11 17:55:55

FPGA时序分析与约束(1)本文中时序分析使用的平台:quartusⅡ13.0芯片厂家:Inter1、什么是时序分析?在FPGA中,数据和时钟传输路径是由相应的EDA软件通过针对特定器件的布局布线

2021-07-26 06:56:44

你好: 现在我使用xilinx FPGA进行设计。遇到问题。我不知道FPGA设计是否符合时序要求。我在设计中添加了“时钟”时序约束。我不知道如何添加其他约束。一句话,我不知道哪条路径应该被禁止。我

2019-03-18 13:37:27

经过两天的恶补,特别是学习了《第五章_FPGA时 序收敛》及其相关的视频后,我基本上明白了时序分析的概念和用法。之后的几天,我会根据一些官方的文件对时序分析进行更系统、深入的学习。先总结一下之前

2011-09-23 10:26:01

FPGA开发过程中,离不开时序约束,那么时序约束是什么?简单点说,FPGA芯片中的逻辑电路,从输入到输出所需要的时间,这个时间必须在设定的时钟周期内完成,更详细一点,即需要满足建立和保持时间

2023-11-15 17:41:10

FPGA时序约束,总体来分可以分为3类,输入时序约束,输出时序约束,和寄存器到寄存器路径的约束。其中输入时序约束主要指的是从FPGA引脚输入的时钟和输入的数据直接的约束。共分为两大类:1、源同步系统

2015-09-05 21:13:07

的文件qxp中,配和qsf文件中的粗略配置信息一起完成增量编译。 4. 核心频率约束+时序例外约束+I/O约束+LogicLock LogicLock是在FPGA器件底层进行的布局约束

2016-06-02 15:54:04

的过程是从一次成功的时序收敛结果开始,把特定的一组逻辑(Design Partition)在FPGA上实现的布局位置和布线结果(Netlist)固定下来,保证这一布局布线结果可以在新的编译中重现,相应

2017-12-27 09:15:17

FPGA时序相关的资料。都看完看懂时序就没问题了。分了三个附件:第一个是通过一些例子教你如何搞定时序分析。第二个附件是网上各种大神们对时序的理解,主要是他们的博客链接以及网站链接。第三个是其他的一些零散的关于时序的资料。

2012-11-12 17:45:28

+ 组合逻辑延时Tlogic + FPGA内部的网络延时Tnet + 寄存器时钟建立时间Tsu –时钟偏斜TclkskewFmax = 1 / Tclk在QuartusII时序分析后很容易看到Fmax

2018-07-03 02:11:23

+ 组合逻辑延时Tlogic + FPGA内部的网络延时Tnet + 寄存器时钟建立时间Tsu –时钟偏斜TclkskewFmax = 1 / Tclk在QuartusII时序分析后很容易看到Fmax

2018-07-09 09:16:13

同步复位,可以降低资源的使用和功耗,有助于时序收敛。由于FPGA的初始状态是确定的(可以在定义说明中指定),为了更快地时序收敛,官方文档认为,能不用复位是最好的,尤其数据路径和移位寄存器的设计中。不过

2020-12-23 17:42:10

对象。(特权同学,版权所有)在图示中,我们从前面reg2reg分析不难推测,在外部芯片内的源寄存器和在FPGA内部的目的寄存器构成的reg2reg也是需要满足一定的时序要求的,即对应的假设它们有同一个

2015-08-12 12:42:14

FPGA时钟时序资料

2014-06-03 20:13:27

FPGA的时序优化高级研修班通知通过设立四大专题,帮助工程师更加深入理解FPGA时序,并掌握时序约束和优化的方法。1.FPGA静态时序分析2.FPGA异步电路处理方法3.FPGA时序约束方法4.FPGA时序优化方法

2013-03-27 15:20:27

FPGA/CPLD的综合、实现过程中指导逻辑的映射和布局布线。下面主要总结一下Xilinx FPGA时序约束设计和分析。

2023-09-21 07:45:57

FPGA设计中电源管理过去,FPGA 设计者主要关心时序和面积使用率问题。但随着FPGA 不断取代ASSP 和ASIC器件计者们现正期望能够开发低功耗设计,在设计流程早期就能对功耗进行正确估算,以及

2012-08-11 16:17:08

FPGA设计中的时序分析及异步设计注意事项建立时间(setup time):是指在触发器的时钟信号上升沿到来以前,数据稳定不变的时间,如果建立时间不够,数据将不能在这个时钟上升沿被打入触发器;保持

2009-12-07 10:14:33

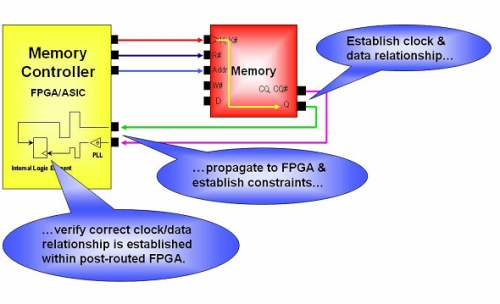

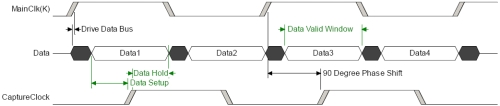

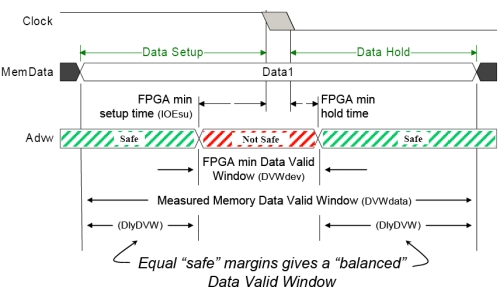

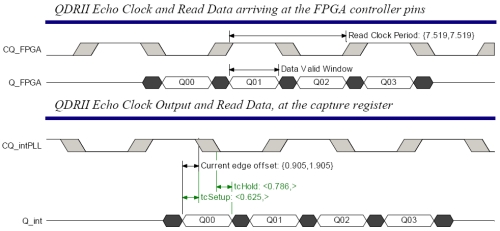

的相位偏移将有效地改变存储控制器接收寄存器的最小有效数据窗口,因此将形成平衡有效数据窗口。时钟偏移调整是FPGA装置中PLL器件的一个组成部分。要确定偏移的值,我们必须考虑到影响信号的布线延迟和任何外部

2017-09-01 10:28:10

随着FPGA器件体积和复杂性的不断增加,设计工程师越来越需要有效的验证方。时序仿真可以是一种能发现最多问题的验证方法,但对许多设计来说,它常常是最困难和费时的方法之一。过去,采用标准台式计算机的时序

2019-07-16 08:10:25

fpga高手经验谈doc文档在数字电路的设计中,时序设计是一个系统性能的主要标志,在高层次设计方法中,对时序控制的抽象度也相应提高,因此在设计中较难把握,但在理解RTL电路时序模型的基础上,采用合理

2012-08-11 11:30:39

在学习fpga的过程中的疑问:1、在功能仿真和板级验真后没问题,还需要进行时序分析吗2、怎么知道自己写的代码有时序问题?

2017-01-08 17:50:35

1。时序分析就是分析前级的数据是否在后一个时钟沿的数据有效窗口里面,就是说在整个窗口内部,数据都应该保持有效,如果不满足时间窗的前端,就是setup违例,如果不满足时间窗的后端,那么就是hold违例

2014-12-29 14:53:00

当你的FPGA设计不能满足时序要求时,原因也许并不明显。解决方案不仅仅依赖于使用FPGA的实现工具来优化设计从而满足时序要求,也需要设计者具有明确目标和诊断/隔离时序问题的能力。设计者现在有一些

2019-08-11 08:30:00

什么是时序分析?时序约束的作用是什么?FPGA组成的三要素分别是哪些?

2021-09-18 06:05:51

所需的电压轨和电流输入到电源管理选型与优化工具中,例如 ADI 公司的 LTpowerCAD 等。图1. 通过 LTpowerCAD 工具选择合适的 DC-DC 转换器来为 FPGA 供电

2018-07-16 16:02:17

1、FPGA中的时序约束--从原理到实例 基本概念 建立时间和保持时间是FPGA时序约束中两个最基本的概念,同样在芯片电路时序分析中也存在。 电路中的建立时间和保持时间其实跟生活中的红绿灯很像

2022-11-15 15:19:27

的。话不多说,上货。 在FPGA中何时用组合逻辑或时序逻辑 在设计FPGA时,大多数采用Verilog HDL或者VHDL语言进行设计(本文重点以verilog来做介绍)。设计的电路都是利用

2023-03-06 16:31:59

如SPI接口中,FPGA通过模拟产生时钟和串行数据与一个外部芯片进行通信,其建立和保持时间是有时序要求的,这个时序要求可以通过外部的手册上获得。那么在FPGA中模拟这个接口要如何保证这个时序要求呀

2023-04-23 11:35:02

当你的FPGA设计不能满足时序要求时,原因也许并不明显。解决方案不仅仅依赖于使用FPGA的实现工具来优化设计从而满足时序要求,也需要设计者具有明确目标和诊断/隔离时序问题的能力。设计者现在有一些

2021-05-18 15:55:00

本文一方面旨在找到正确解决方案并选择最合适的电源管理产品,另一方面则是如何优化实际解决方案以用于FPGA。找到合适的电源解决方案寻找为FPGA供电的最佳解决方案并不简单。许多供应商以适合为FPGA

2019-05-05 08:00:00

。掌握分析和确定关键路径时序的方法,并通过分析找出关键路径的时序问题,再对关键路径进行优化,通过RTL层面的不断优化,不断修炼自己的设计能力,让设计出来的电路更为靠谱有效!本资料属大西瓜FPGA开发团队,在此开源,与大家一起学习FPGA!

2017-02-26 09:42:48

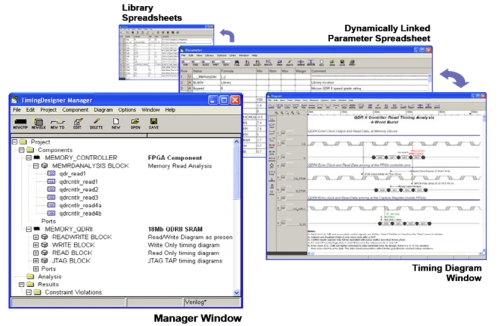

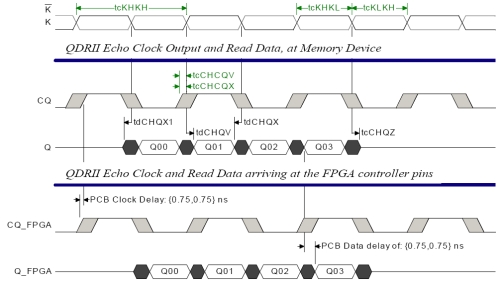

如何有效的管理FPGA设计中的时序问题当FPGA设计面临到高级接口的设计问题时,EMA的TimingDesigner可以简化这些设计问题,并提供对几乎所有接口的预先精确控制。从简单SRAM接口到高速

2009-04-14 17:03:52

这是Xiinx公司的一个工程师写的,介绍了如何使用工具来解决FPGA设计中的时序问题,觉得不错,就转过来了。耗费数月精力做出的设计却无法满足时序要求,这确实非常令人伤心。然而,试图正确地对设计进行

2012-12-14 16:04:56

大家好,我想知道如何实现硬件(FPGA)中的时序报告给出的时序。我的意思是,如何测量FPGA和FPGA中输入信号的建立或保持时间与静态时间报告给出的值进行比较。FPGA怪胎以上来自于谷歌翻译以下

2019-01-15 11:07:15

怎么知道一个时序逻辑电路是上升沿有效还是下降沿有效呢?

2023-05-10 11:27:41

沟道MOSFET来将FPGA与某个电压轨连接和断开。图3. 多个FPGA电源电压的启动和关断顺序。电压轨单调上升除了电压时序之外,启动过程中还可能要求电压单调上升。这意味着电压仅线性上升,如图4中的电压

2018-08-27 09:23:11

电源管理选型与优化工具中,例如ADI公司的 LTpowerCAD等。 图1. 通过LTpowerCAD工具选择合适的DC-DC转换器来为FPGA供电。 LTpowerCAD可用来为各个电压轨提供

2021-06-01 07:00:00

引言 电源时序控制是微控制器、FPGA、DSP、 ADC和其他需要多个电压轨供电的器件所必需的一项功能。这些应用通常需要在数字I/O轨上电前对内核和模拟模块上电,但有些设计可能需要采用其他序列

2019-07-03 08:15:19

1. FPGA时序的基本概念FPGA器件的需求取决于系统和上下游(upstream and downstrem)设备。我们的设计需要和其他的devices进行数据的交互,其他的devices可能是

2019-07-09 09:14:48

如何发现并解决FPGA设计中的时序问题?

2021-04-29 06:49:22

,要经过Thz的时间数据才会有效,这个时间也是可以查到的,即我们前面理论篇所讲的参数那个参数TOH,注意这个TOH和上面的那个Toh是不一样的。然后是FPGA的建立时间,我们从时序报告里查。那么,可以

2015-03-31 10:35:18

FPGA重要设计思想及工程应用之时序及同

在FPGA设计中最好的时钟方案 是: 由专用的全局时钟输入引脚 动单个 主时钟去控制设计项目中的每一个触发 器

2010-02-09 10:29:36 51

51 在分析TDICCD器件驱动时序关系的基础上,设计了可选积分级数的驱动时序发生器.作为卫星上的有效载荷,TDIC?鄄CD成像系统可以根据不同的光照条件及探测分辨率的需求,选择不同

2010-07-28 17:43:54 37

37 一、摘要 从简单SRAM接口到高速同步接口,TimingDesigner软件允许设计者在设计流程的初期就判断出潜在的时序问题,尽最大可能在第一时间解决时序问题。在设计过程的早期检测到时序问题,不仅节省时间,而且可以更容易的实施设计方案。美国EMA公司的设计自动

2011-01-13 16:25:00 103

103 介绍了采用STA (静态时序分析)对FPGA (现场可编程门阵列)设计进行时序验证的基本原理,并介绍了几种与STA相关联的时序约束。针对时序不满足的情况,提出了几种常用的促进 时序收敛的方

2011-05-27 08:58:50 70

70 当你的FPGA设计不能满足时序要求时,原因也许并不明显。解决方案不仅仅依赖于使用FPGA的实现工具来优化设计从而满足时序要求,也需要设计者具有明确目标和诊断/隔离时序问题的能力。

2014-08-15 14:22:10 1169

1169 FPGA时序约束方法很好地资料,两大主流的时序约束都讲了!

2015-12-14 14:21:25 19

19 FPGA重要设计思想及工程应用之时序及同步设计

2016-05-10 11:24:33 16

16 赛灵思FPGA设计时序约束指南,下来看看

2016-05-11 11:30:19 48

48 基于时序路径的FPGA时序分析技术研究_周珊

2017-01-03 17:41:58 2

2 如何有效地管理FPGA设计中的时序问题

2017-01-14 12:49:02 14

14 当你的FPGA设计不能满足时序要求时,原因也许并不明显。解决方案不仅仅依赖于使用FPGA的实现工具来优化设计从而满足时序要求,也需要设计者具有明确目标和诊断/隔离时序问题的能力。设计者现在有一些

2017-02-09 01:59:11 264

264 fpga时序收敛

2017-03-01 13:13:34 23

23 作时序和布局约束是实现设计要求的关键因素。本文是介绍其使用方法的入门读物。 完成 RTL 设计只是 FPGA 设计量产准备工作中的一部分。接下来的挑战是确保设计满足芯片内的时序和性能要求。为此

2017-11-17 05:23:01 2417

2417

一个好的FPGA设计一定是包含两个层面:良好的代码风格和合理的约束。时序约束作为FPGA设计中不可或缺的一部分,已发挥着越来越重要的作用。毋庸置疑,时序约束的最终目的是实现时序收敛。时序收敛作为

2017-11-17 07:54:36 2326

2326

针对八通道采样器AD9252的高速串行数据接口的特点,提出了一种基于FPGA时序约束 的高速解串方法。使用Xilinx公司的FPGA接收高速串行数据,利用FPGA内部的时钟管理模块DCM、位置约束

2017-11-17 12:27:01 6488

6488

现有的工具和技术可帮助您有效地实现时序性能目标。当您的FPGA 设计无法满足时序性能目标时,其原因可能并不明显。解决方案不仅取决于FPGA 实现工具为满足时序要求而优化设计的能力,还取决于设计人员指定前方目标,诊断并隔离下游时序问题的能力。

2017-11-18 04:32:34 2951

2951 时序以及各阶段I/O 管脚状态,说明了FPGA上电配置对电路功能的严重影响,最后针对不同功能需求的FPGA外围电路提出了有效的设计建议。

2017-11-22 07:18:34 6221

6221

作为赛灵思用户论坛的定期访客(见 ),我注意到新用户往往对时序收敛以及如何使用时序约束来达到时序收敛感到困惑。为帮助 FPGA设计新手实现时序收敛,让我们来深入了解时序约束以及如何利用时序约束实现

2017-11-24 19:37:55 4903

4903

FPGA时序收敛让你的产品达到最佳性能!

2018-04-10 11:38:48 18

18 FPGA设计一个很重要的设计是时序设计,而时序设计的实质就是满足每一个触发器的建立(Setup)/保持(Hold)时间的要求。

2018-06-05 01:43:00 4150

4150

本课程以目前流行的Xilinx 7系列FPGA的开发为主线,全面讲解FPGA的原理及电路设计、Verilog HDL语言及VIVADO的应用,并循序渐进地从组合逻辑、时序逻辑的开发开始,深入到FPGA的基础应用、综合应用和进阶应用。

2019-12-05 07:08:00 2539

2539

时序分析结果,并根据设计者的修复使设计完全满足时序约束的要求。本章包括以下几个部分: 1.1 静态时序分析简介 1.2 FPGA 设计流程 1.3 TimeQuest 的使用 1.4 常用时序约束 1.5 时序分析的基本概念

2020-11-11 08:00:00 58

58 本文档的主要内容详细介绍的是华为FPGA硬件的静态时序分析与逻辑设计包括了:静态时序分析一概念与流程,静态时序分析一时序路径,静态时序分析一分析工具

2020-12-21 17:10:54 18

18 在高速系统中FPGA时序约束不止包括内部时钟约束,还应包括完整的IO时序约束利序例外约束才能实现PCB板级的时序收敛。因此,FPGA时序约束中IO口时序约束也是重点。只有约東正确才能在高速情况下保证FPGA和外部器件通信正确

2021-01-13 17:13:00 11

11 本文章探讨一下FPGA的时序约束步骤,本文章内容,来源于配置的明德扬时序约束专题课视频。

2022-03-16 09:17:19 3255

3255

上一篇《FPGA时序约束分享01_约束四大步骤》一文中,介绍了时序约束的四大步骤。

2022-03-18 10:29:28 1323

1323

时序分析时FPGA设计中永恒的话题,也是FPGA开发人员设计进阶的必由之路。慢慢来,先介绍时序分析中的一些基本概念。

2022-03-18 11:07:13 2096

2096 本文章探讨一下FPGA的时序input delay约束,本文章内容,来源于配置的明德扬时序约束专题课视频。

2022-05-11 10:07:56 3462

3462

明德扬有完整的时序约束课程与理论,接下来我们会一章一章以图文结合的形式与大家分享时序约束的知识。要掌握FPGA时序约束,了解D触发器以及FPGA运行原理是必备的前提。今天第一章,我们就从D触发器开始讲起。

2022-07-11 11:33:10 2922

2922

本文章探讨一下FPGA的时序input delay约束,本文章内容,来源于明德扬时序约束专题课视频。

2022-07-25 15:37:07 2379

2379

时序逻辑的代码一般有两种: 同步复位的时序逻辑和异步复位的时序逻辑。在同步复位的时序逻辑中复位不是立即有效,而在时钟上升沿时复位才有效。 其代码结构如下:

2023-03-21 10:47:07 400

400 STA(Static Timing Analysis,即静态时序分析)在实际FPGA设计过程中的重要性是不言而喻的

2023-06-26 09:01:53 362

362

FPGA开发过程中,离不开时序约束,那么时序约束是什么?简单点说,FPGA芯片中的逻辑电路,从输入到输出所需要的时间,这个时间必须在设定的时钟周期内完成,更详细一点,即需要满足建立和保持时间。

2023-06-26 14:42:10 344

344

FPGA开发过程中,vivado和quartus等开发软件都会提供时序报告,以方便开发者判断自己的工程时序是否满足时序要求。

2023-06-26 15:29:05 531

531

FPGA时序不收敛,会出现很多随机性问题,上板测试大概率各种跑飞,而且不好调试定位原因,所以在上板测试前,先优化时序,再上板。

2023-06-26 15:41:31 1112

1112

FPGA高级时序综合教程

2023-08-07 16:07:55 3

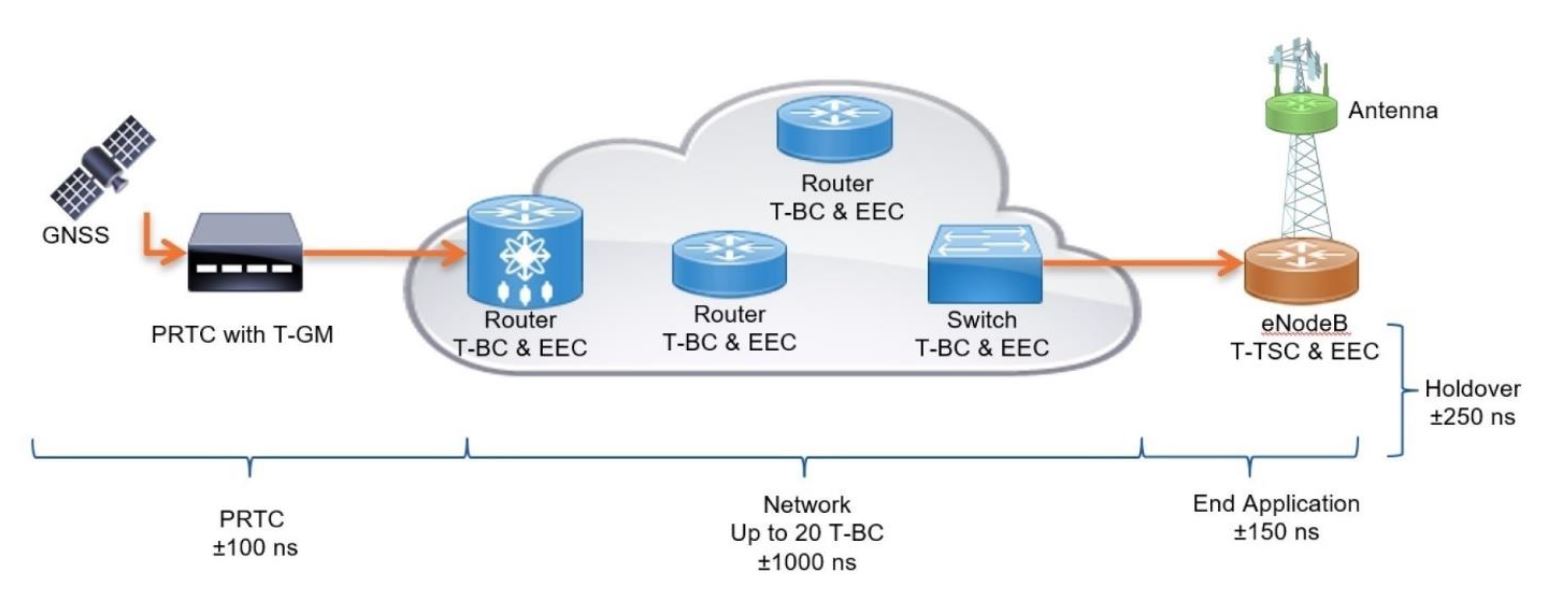

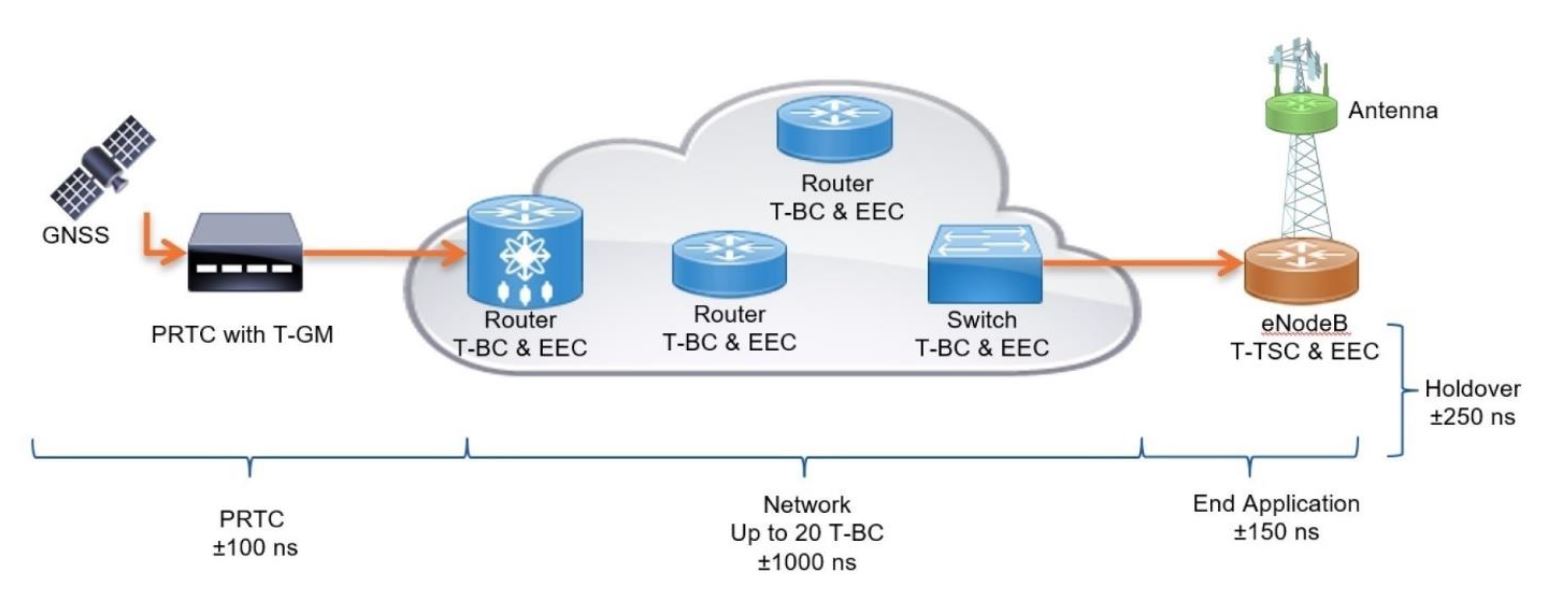

3 5G网络的时序设计和管理同步方式

2023-11-24 14:46:46 222

222

电子发烧友App

电子发烧友App

评论