本文首先介绍了FPGA的特点与FPGA芯片结构,其次分析了FPGA与ASIC及CPLD对比,最后介绍了FPGA基础入门到高手相关知识与FPGA下载配置学习心得。

2018-05-30 08:39:29 37049

37049

我们需要学会区分PCB封装里面的元器件引脚,并在PCB文件中标出来,然后学习创建元件库里面没有的器件封装,通过老师的分步演示从原理图导入PCB的步骤,最后学习电路的连线,完成PCB的封装。

2019-04-18 14:15:40 19195

19195 时钟网络反映了时钟从时钟引脚进入FPGA后在FPGA内部的传播路径。

2019-09-10 15:12:31 7150

7150

01、如何决定FPGA中需要什么样的时钟速率 设计中最快的时钟将确定 FPGA 必须能处理的时钟速率。最快时钟速率由设计中两个触发器之间一个信号的传输时间 P 来决定,如果 P 大于时钟周期 T,则

2020-11-23 13:08:24 4644

4644

当我刚开始我的FPGA设计生涯时,我对明显更小、更不灵活的 FPGA(想想 XC4000XL / Clcyone3/4和 Spartan)和工具的非常简单的时钟规则之一是尽可能只使用单个时钟。当然,这并不总是可能的,但即便如此,时钟的数量仍然有限。

2022-09-30 08:49:26 2145

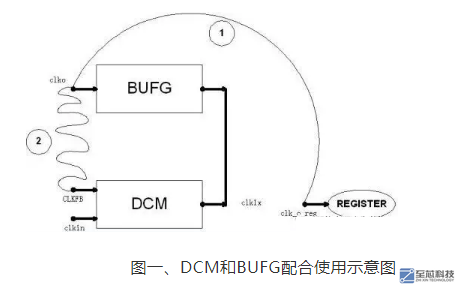

2145 “全局时钟和第二全局时钟资源”是FPGA同步设计的一个重要概念。合理利用该资源可以改善设计的综合和实现效果;如果使用不当,不但会影响设计的工作频率和稳定性等,甚至会导致设计的综合、实现过程出错

2023-07-24 11:07:04 1443

1443

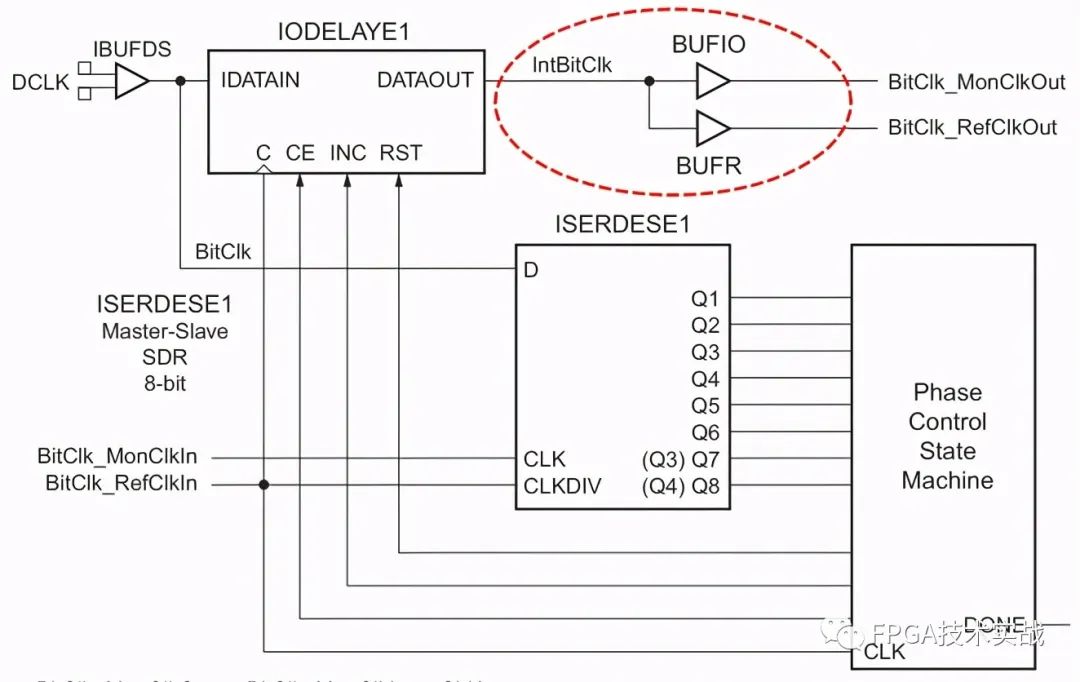

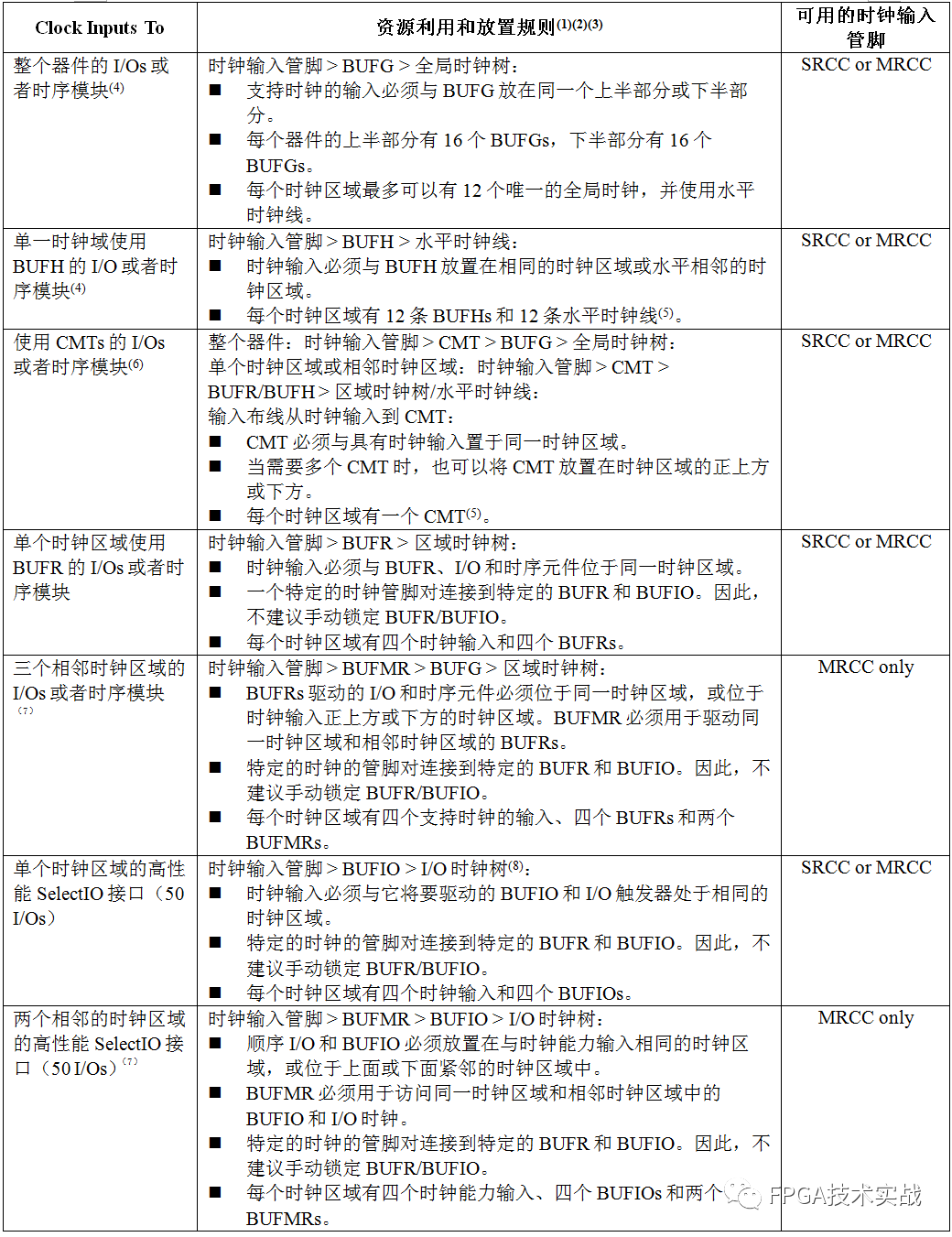

通过上一篇文章“时钟管理技术”,我们了解Xilinx 7系列FPGA主要有全局时钟、区域时钟、时钟管理块(CMT)。 通过以上时钟资源的结合,Xilinx 7系列FPGA可实现高性能和可靠的时钟分配

2023-08-31 10:44:31 4432

4432

本文主要介绍Xilinx FPGA的GTx的参考时钟。下面就从参考时钟的模式、参考时钟的选择等方面进行介绍。

2023-09-15 09:14:26 5117

5117

生成时钟包括自动生成时钟(又称为自动衍生时钟)和用户生成时钟。自动生成时钟通常由PLL或MMCM生成,也可以由具有分频功能的时钟缓冲器生成如7系列FPGA中的BUFR、UltraScale系列

2024-01-11 09:50:09 3808

3808

设计流程紧密集成,在项目的任何阶段均可访问。原理图、PCB Layout 和FPGA 数据库始终保持同步,以便用户控制项目的设计数据流。另外,原理图用户可决定何时将 FPGA 数据(新数据或更新数据

2018-09-20 11:11:16

毕业后,从一个嵌入式硬件狗转做FPGA工程师,从中兜兜转转绕了不少弯路,为了给后人避坑,所以今天开始写有关FPGA从入门到精通的教程吧,这也算是给我国集成电路的发展做出微薄的贡献吧。 本门课程主要

2020-06-23 23:52:00

使用的时钟信号往往不只是供给单个寄存器使用,因为在实际应用中,成百上千甚至更多的寄存器很可能共用一个时钟源,那么从时钟源到不同寄存器间的延时也可能存在较大偏差(我们通常称为时钟网络延时),而我们知道

2019-04-12 01:15:50

Tc2t;时钟到达目的寄存器,即ADV7123芯片的引脚输入端,其路径延时为Tc2r,这个延时包括了时钟从PLL输出到FPGA引脚的延时以及时钟从FPGA的引脚到ADV7123引脚的延时,后者的延时

2015-07-30 22:07:42

FPGA时钟问题 2010-06-11 15:55:39分类: 嵌入式1.FPGA的全局时钟是什么?FPGA的全局时钟应该是从晶振分出来的,最原始的频率。其他需要的各种频率都是在这个基础上利用PLL或者其他分频手段得到的。

2021-07-29 09:25:57

那个商业行为背后的动机,只是想以此为契机从技术的角度,略略讨论下这次收购背后的关键因素——FPGA和ASIC的在AI计算中衔接关系。因为并不是专家,所以如有错误理解请指出。 从FPGA到ASIC

2023-03-28 11:14:04

本来刚开始从原理图画起,到pcb都正常,但是在pcb中,我重新标注了几次,原理图也重新标注了,现在问题是,两边的元件对不上了,updata不起作用,反标也不行,该怎么做才能让原理图和pcb元件能对应上呢

2011-03-04 21:40:20

从ASIC到FPGA的转换系统时钟设计方案

2011-03-02 09:37:37

从MCU到FPGA

2021-02-02 07:36:46

包含.bit文件,而不包括VHDL源代码。有没有办法获得最简单的源代码,这将允许我从FPGA获取数据流到PC上的COM端口。我只需要来自FPGA-> PC的3.2Kbps数据。

2019-09-11 12:18:49

嗨, 我正在开发一种设计,我们的主板有1个virtex5 fpga和9个从属卡,每个都有1个V5 fpga。我想同步所有9个从卡的操作。我还希望主卡和从卡之间的数据传输速率为300-400Mbps

2019-01-30 06:52:36

在设计中想用上AD9254作为ADC,在设计过程中发现datasheet内部提供了多种时钟设计方案,由于设计的限制,想要省去所有方案中均推荐使用的AD951x芯片,请问是否有曾经使用过该款AD的同仁,使用直接从FPGA差分时钟引脚引出的时钟信号,是否能够满足设计的要求?

2018-11-02 09:14:32

我现在做一个数据采集板子,用的zyqn7000 soc FPGA,ADC用的ADC08DL502 ,采样率最高到500M,想请问下这么高的采样率的时钟是否可以直接从FPGA输出给ADC,还是要用

2024-12-26 06:37:42

桥接器和一些简单的UART VHDL代码通过HyperTerm从FPGA到PC获取数据?我在ML605上看到,Xilinx表示需要实现UART IP,例如XPS UART Lite或UART16550

2019-09-09 06:23:26

必须适当地与所有数据位的到达保持同步。如果接收器使用发射时钟,可能会要求延迟从发送端到接收端的时钟信号。 有时设计可能需要一个更高的时钟频率来运行FPGA上的逻辑。但是,只有低频率输出的时钟源可以用

2020-04-25 07:00:00

1、Audio codec时钟源从BCLK1获取 Platform: RK3399 OS: Android 7.1 Kernel: v4.4.83 需求: 默认codec的clock

2022-11-15 17:36:45

的问题是,我可以在FPGA内部使用这个时钟作为FPGA和电路板的主时钟吗?我有一个应用程序,我想在板上尽可能少的部件,我不关心主时钟频率是什么,只要它是1-50MHz时钟。要使用CCLK我必须有一个PCB

2019-05-07 13:40:54

数字信号处理[3]已经成为FPGA的一个重要课题,高速的采样频率带来的是大容量的存储数据。在存储芯片领域,DDR3以较低的功耗,较快的存储速度,较高的存储容量和较低的价格迅速占领市场;同时在绘制PCB板图

2018-08-30 09:59:01

一部追踪器,这又是怎么回事呢?由于目前安卓手机大都自带GPS定位功能,很多移动广告公司为了做到更精准的广告投放,在软件里就恶意插入获取用户位置信息的代码。记者在暗访一家名为“赢告无限”的广告公司时,一位

2012-12-01 17:36:51

大家好,设备:xc7vx485tffg1761-2我需要从FPGA提供外部时钟。所以我使用了OBUFDS,输入时钟来自clock_wizard。我想知道OBUFDS是否是正确的选择,还是有任何提供输出差分时钟的方法。谢谢,Musthafa V.

2020-04-15 08:30:14

嗨,有谁知道如何从fpga(斯巴达3)中读出用户代码?干杯约翰以上来自于谷歌翻译以下为原文Hi, Anybody knows how to readout the usercode from within the fpga (spartan3)? cheers John

2019-07-26 10:53:31

嗨,我正在尝试从FPGA向另一个设备输出一个时钟信号(10MHz)来驱动一个50欧姆的端接负载。我试着用DDR来输出这个时钟。我从主振荡器时钟输入(50MHz)到virtex板生成此信号。我使用DCM以5来获得10Mhz。然后我把它运行到DDR。到目前为止,我没有运气。有人可以给我指点吗?谢谢。

2020-06-15 08:40:22

先生/女士, 我们如何从virtex 5(XC5VLX110T)获取时钟信号?我们已经参考了用户手册并尝试从d手册中提到的几个引脚获取信号。针脚:AH17,AG18。通过AH17引脚的输出是17

2019-03-04 10:10:13

我知道在接入点模式下我们可以设置用户和密码,但我看到另一种方式(如我附上的图表)ESP8266 可以从路由器获取用户和密码,这怎么可能?

2023-05-16 08:49:35

大家好

我正在使用 FX2 设备,以前也使用过 FX3 设备。 使用 FX3 设备 SDK,当我下载它时,我在安装文件夹中获得了许多示例源代码,但是它没有 FX2 的示例源代码,我如何获取用于开发 fx2 的 sdk 和示例源代码?

2025-05-07 07:25:05

“Drago,William @NARDAEAST”写道:>全部,>>任何人都可以告诉我如何在VEE 6.xx中获取用户名(System.Environment.UserName

2019-08-29 11:03:45

我想知道如何通过 wifi 从 C329 相机获取图像到用户的屏幕,是直接 wifi 链接,还是通过互联网?

IMAGE 命令要求是:“图像文件应使用文件管理器上传到设备”,因此不是动态的。

是否有

2023-05-10 09:44:29

我们正在使用St 分发源代码,我们在buildroot工具中编译源代码。但是我们无法获取用户登录页面。我怎样才能得到用户登录页面。

2022-12-26 10:41:39

周期吗?3.FPGA做加减法之类的运算时间要耗费多少时钟周期?比如我定义输入变量A、B、C、D都是8位,输出变量E是16位,使E的前八位存入A+B,后八位存入C+D,那么从输入到输出需要多少个时钟周期?谢谢!

2015-05-11 19:17:21

考虑的是在SDRAM端口的时钟延时,也就是说还没有考虑SDRAM时钟从PLL输出,经过FPGA内部走线,和外部PCB的延时,我们想一下,是不是有一个这样的关系 就是,PLL的时钟偏移 + 时钟从PLL

2015-03-31 10:35:18

的值,由于我们的时钟是总PLL发出的,时钟从FPGA管脚输出后再送给SDRAM,因此这个值一定是负值,而且也是时钟在PCB上的走线延时,这个值我们估算为-0.1ns好了,因为真的没法算我觉得。 然后

2015-03-31 10:20:00

具有DCO输出,可将DAC输入时钟转发至FPGA。我在想,这与ADC情况非常相似。但现在我意识到,对DCO信号的引用并没有给我带来任何好处。首先,DCO信号经历从DAC到FPGA的传播延迟,然后数据

2020-03-12 11:12:21

详细接入体验可参考Account Kit提供的SampleCode示例工程。

典型场景:

1、元服务需要完善用户头像信息,参见获取头像。

2、元服务提供的服务依赖用户手机号,需要获取用户手机号,参见获取

2025-04-02 11:10:42

、Client Secret、Authorization Code从华为服务器获取Access Token,再使用Access Token请求获取用户信息。

从用户信息中获取到手机号、UnionID

2025-04-08 16:14:04

pcb Layout 设计从基础到实践多媒体教程

2006-05-28 01:11:23 0

0 DLL在FPGA时钟设计中的应用:在ISE集成开发环境中,用硬件描述语言对FPGA 的内部资源DLL等直接例化,实现其消除时钟的相位偏差、倍频和分频的功能。时钟电路是FPGA开发板设计中的

2009-11-01 15:10:30 33

33 最初,FPGA 只是用于胶合逻辑,从胶合逻辑到算法逻辑再到数字信号处理、高速串行收发器和嵌入式处理器,FPGA 真正地从配角变成了主角。

2009-11-30 16:25:14 17

17 本文阐述了用于FPGA的可优化时钟分配网络功耗与面积的时钟布线结构模型。并在时钟分配网络中引入数字延迟锁相环减少时钟偏差,探讨了FPGA时钟网络中锁相环的实现方案。

2010-08-06 16:08:45 12

12 Printf:读取用户输入

前面的程序很好,但要是如果能从用户那里读入值5和7而不是使用固定的值的话,那就更好了。可以改为下面的程序: #include

2009-07-29 10:42:21 2234

2234 PCB板完整电磁信息的获取及应用

调试PCB的传统工具包括:时域的示波器

2009-12-26 14:44:40 751

751 大型设计中FPGA的多时钟设计策略

利用FPGA实现大型设计时,可能需要FPGA具有以多个时钟运行的多重数据通路,这种多时钟FPGA设计必须特别小心,需要注意最大时钟速率

2009-12-27 13:28:04 827

827

在FPGA设计中,为了成功地操作,可靠的时钟是非常关键的。设计不良的时钟在极限的温度、电压下将导致错误的行为。在设计PLD/FPGA时通常采用如下四种类型时钟:全局时钟、门控时钟

2011-09-21 18:38:58 4131

4131

在Quartus Ⅱ开发环境下,用Verilog HDL硬件描述语言设计了一个可以在FPGA芯片上实现的数字时钟. 通过将设计代码下载到FPGA的开发平台Altera DE2开发板上进行了功能验证. 由于数字时钟的通用

2011-11-29 16:51:43 184

184 利用FPGA实现大型设计时,可能需要FPGA具有以多个时钟运行的多重数据通路,这种多时钟FPGA设计必须特别小心,需要注意最大时钟速率、抖动、最大时钟数、异步时钟设计和时钟/数

2012-05-21 11:26:10 1591

1591

DLL在_FPGA时钟设计中的应用,主要说明DLL的原理,在Xilinx FPGA中是怎么实现的。

2015-10-28 14:25:42 1

1 基于FPGA的数字时钟设计,可实现闹钟的功能,可校时。

2016-06-23 17:15:59 71

71 实现了基于FPGA与USB的CMOS图像获取与采集系统的设计。介绍了成像系统的结构、CMOS图像获取时序的VHDL程序实现、包含FPGA控制及USB固件与VC接口界面程序等在内的数据传输通路设计以及Direct Draw数字图像的显示等。实验结果表明,成像系统工作正常,数据传输满足USB接口规范与设计要求。

2016-09-22 16:53:46 23

23 如何正确使用FPGA的时钟资源

2017-01-18 20:39:13 22

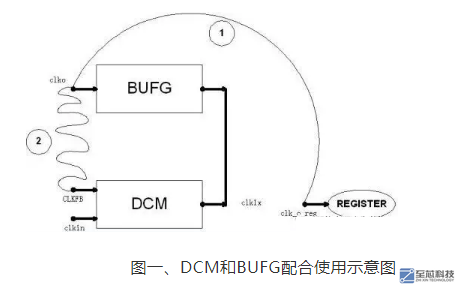

22 有些FPGA学习者,看Xilinx的Datasheet会注意到Xilinx的FPGA没有PLL,其实DCM就是时钟管理单元。 1、DCM概述 DCM内部是DLL(Delay Lock Loop结构

2018-05-25 15:43:53 8952

8952

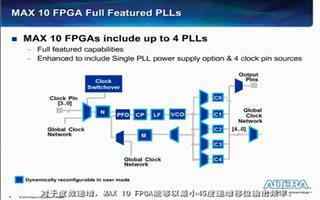

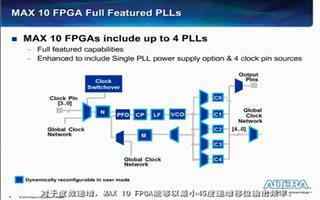

MAX 10 FPGA PLL和时钟培训,此次培训涉及到器件系列的时钟特性和选项。有20个全局时钟网络,全局CLK输入引脚数量也可以加倍,用作通用IO引脚。并且采用动态用户控制进行各种选择和电源控制,构建鲁棒的时钟网络源。它所有4个PLL都是全功能的。

2018-06-20 08:00:00 3327

3327

本文档的主要内容详细介绍的是spartan-6 FPGA的时钟资源的用户指南资料免费下载。

2019-02-15 16:39:07 28

28 时钟是FPGA设计中最重要的信号,FPGA系统内大部分器件的动作都是在时钟的上升沿或者下降沿进行。

2019-09-20 15:10:18 6055

6055

偏斜 时钟偏斜是一种现象,其中时钟信号以不同的间隔到达不同的目的地。时钟信号通常用于 PCB 设计中的同步通信。例如,串行外设接口( SPI )使用时钟信号在设备之间发送和接收数据。 在理想的主机到多个从机组件的配置中,时钟信号的传播时间没有延迟

2020-09-16 22:59:02 2876

2876 时钟网络反映了时钟从时钟引脚进入FPGA后在FPGA内部的传播路径。 报告时钟网络命令可以从以下位置运行: A,VivadoIDE中的Flow Navigator; B,Tcl命令

2020-11-29 09:41:00 3695

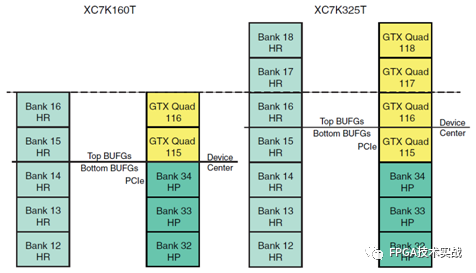

3695 区域(Region):每个FPGA器件被分为多个区域,不同的型号的器件区域数量不同。

FPGA时钟资源主要有三大类:时钟管理模、时钟IO、时钟布线资源。

时钟管理模块:不同厂家及型号的FPGA中

2020-12-09 14:49:03 21

21 本文档的主要内容详细介绍的是FPGA硬件基础之FPGA时钟资源的工程文件免费下载。

2020-12-10 15:00:29 16

16 前些时候,共享充电宝涨价问题引起了消费者热议,现在,新的问题又来了。根据有关媒体的消息,共享充电宝存在着一个安全隐患问题,那就是窃取用户的个人隐私。

2020-12-15 15:33:09 5166

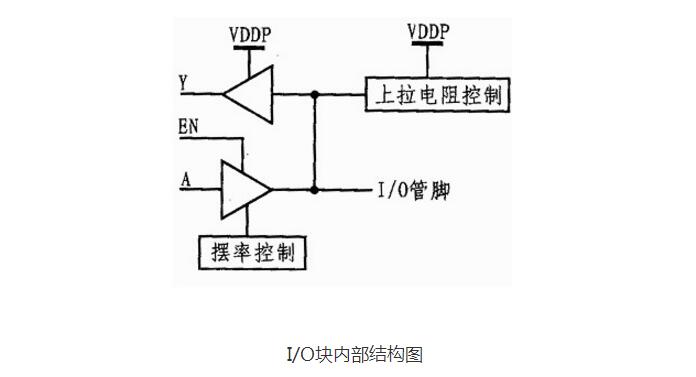

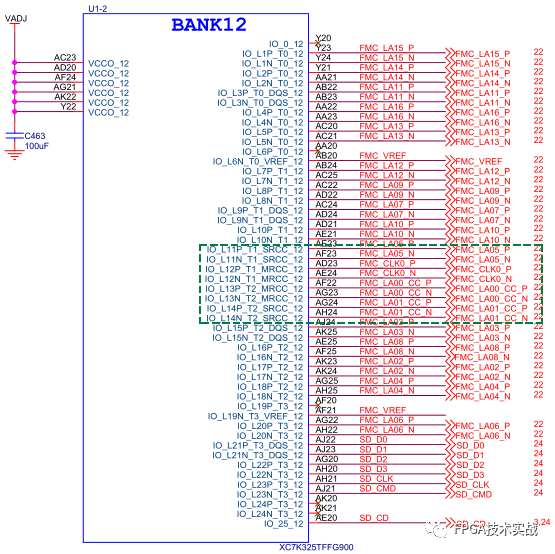

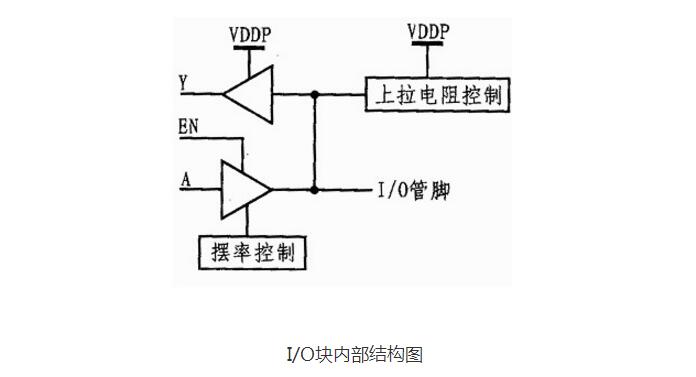

5166 引言:7系列FPGA具有多个时钟路由资源,以支持各种时钟方案和要求,包括高扇出、短传播延迟和极低的偏移。为了最好地利用时钟路由资源,必须了解如何从PCB到FPGA获取用户时钟,确定哪些时钟路由资源

2021-03-22 10:16:18 6115

6115

引言:从本文开始,我们陆续介绍Xilinx 7系列FPGA的时钟资源架构,熟练掌握时钟资源对于FPGA硬件设计工程师及软件设计工程师都非常重要。本章概述7系列FPGA时钟,比较了7系列FPGA时钟

2021-03-22 10:25:27 6070

6070 从电池中获取更多能量

2021-04-24 15:45:54 6

6 1. STM32获取系统时钟第一步在main函数开头添加如下代码:RCC_ClocksTypeDef RCC_Clocks;RCC_GetClocksFreq(&RCC_Clocks

2021-12-24 19:35:25 11

11 (08)FPGA时钟概念1.1 目录1)目录2)FPGA简介3)Verilog HDL简介4)FPGA时钟概念5)结语1.2 FPGA简介FPGA(Field Programmable Gate

2021-12-29 19:41:17 2

2 (12)FPGA时钟设计原则1.1 目录1)目录2)FPGA简介3)Verilog HDL简介4)FPGA时钟设计原则5)结语1.2 FPGA简介FPGA(Field Programmable

2021-12-29 19:41:27 17

17 (29)FPGA原语设计(差分时钟转单端时钟)1.1 目录1)目录2)FPGA简介3)Verilog HDL简介4)FPGA原语设计(差分时钟转单端时钟)5)结语1.2 FPGA简介FPGA

2021-12-29 19:41:38 5

5 (30)FPGA原语设计(单端时钟转差分时钟)1.1 目录1)目录2)FPGA简介3)Verilog HDL简介4)FPGA原语设计(单端时钟转差分时钟)5)结语1.2 FPGA简介FPGA

2021-12-29 19:41:48 10

10 经过了前面的开胃菜,项目正式开始。一步步讲解这个模型怎么玩起来的。从C 到 matlab 到 FPGA ,三个平台联合起来完成这个 由 RTL 实现 CNN 的项目。

2022-03-15 17:13:24 3087

3087 xilinx 的 FPGA 时钟结构,7 系列 FPGA 的时钟结构和前面几个系列的时钟结构有了很大的区别,7系列的时钟结构如下图所示。

2022-07-03 17:13:48 4699

4699 电子发烧友网站提供《Logos系列FPGA时钟资源(Clock)用户指南.pdf》资料免费下载

2022-09-26 10:15:21 11

11 电子发烧友网站提供《从云端获取数据到您的Arduino.zip》资料免费下载

2022-11-08 15:12:44 6

6 ASIC 和FPGA芯片的内核之间最大的不同莫过于时钟结构。ASIC设计需要采用诸如时钟树综合、时钟延迟匹配等方式对整个时钟结构进行处理,但是 FPGA设计则完全不必。

2022-11-23 16:50:49 1249

1249

电子发烧友网站提供《从Web获取湿度/温度.zip》资料免费下载

2022-12-14 09:21:01 0

0 设计开发过程高质量、顺畅地进行呢?“PCB系统设计——从原理图到投产”系列将通过实例演示,在5期直播网课中与大家探讨PCB系统设计理念与方法,从概念阶段到物理实现

2022-12-19 11:29:14 1123

1123

之前在玩FPGA时,对于一个系统工程,当逻辑电路设计完成之后,一般会先拿给Vivado/Quartus先去跑一般综合,然后去获取所有的跨时钟路径,在ASIC里,基本也是拿EDA工具去分析获取。今儿个搞个小demo,看在SpinalHDL当设计做完后,如何一键提取整个工程里所有的跨时钟路径。

2023-09-15 14:06:56 1464

1464 Altera的FPGA中,只有从专用时钟管脚(Dedicated clock)进去的信号,才能接片内锁相环(PLL)吗? 在Altera的FPGA中,专用时钟管脚是经过特殊处理的单独管脚,其用途

2023-10-13 17:40:00 1292

1292 fpga跨时钟域通信时,慢时钟如何读取快时钟发送过来的数据? 在FPGA设计中,通常需要跨时钟域进行数据通信。跨时钟域通信就是在不同的时钟域之间传输数据。 当从一个时钟域传输数据到另一个时钟域

2023-10-18 15:23:51 1901

1901 fpga与dsp通讯怎样同步时钟频率?dsp和fpga通信如何测试? 在FPGA与DSP通讯时,同步时钟频率非常重要,因为不同的设备有不同的时钟频率,如果两者的时钟频率不同步,会导致通讯数据的错误或

2023-10-18 15:28:13 2793

2793 FPGA为什么有时候还需要一个时钟配置芯片提供时钟呢? FPGA(Field Programmable Gate Array)是一种可编程逻辑器件,可以根据不同需要编程,实现不同的功能。在FPGA中

2023-10-25 15:14:20 2400

2400 CADENCE从原理图到PCB步骤(精)

2022-12-30 09:19:46 35

35 从设计到生产,PCB小批量生产解密

2023-12-20 11:15:47 6627

6627 据悉,黑客可借助此漏洞获取加密密钥,进而盗取用户个人信息。DMP作为内存系统中的角色,负责推测当前运行代码所需访问的内存地址。黑客则借此可预测下一步需获取的数据位,以此干扰数据的预取过程,进而获悉用户敏感数据。此类攻击行为被称为“Go Fetch”操作。

2024-03-22 10:30:53 1529

1529 FPGA 中包含一些全局时钟资源。以AMD公司近年的主流FPGA为例,这些时钟资源由CMT(时钟管理器)产生,包括DCM、PLL和MMCM等。

2024-04-25 12:58:30 3304

3304

在FPGA(现场可编程门阵列)设计中,消除时钟抖动是一个关键任务,因为时钟抖动会直接影响系统的时序性能、稳定性和可靠性。以下将详细阐述FPGA中消除时钟抖动的多种方法,这些方法涵盖了从硬件设计到软件优化的各个方面。

2024-08-19 17:58:54 3753

3753 爬虫数据获取实战指南:从入门到高效采集 在数字化浪潮中,数据已成为驱动商业增长的核心引擎。无论是市场趋势洞察、竞品动态追踪,还是用户行为分析,爬虫技术都能助你快速捕获目标信息。然而,如何既

2025-03-24 14:08:23 1331

1331

电子发烧友App

电子发烧友App

评论