USB 3.0的传输编码方式与USB 2.0有所不同,从USB 3.0规范中我们了解到,USB 3.0采用的是8b/10b编码方式

2011-11-22 16:22:57 10296

10296

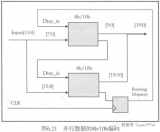

为了在USB 3.0中实现数据的8 b/10 b编解码,把8b/10b编解码分解成5 b/6 b编解码和3 b/4 b编解码,然后在FPGA上实现了具体的硬件电路。

2011-11-30 11:38:18 4000

4000

以下是笔者一些关于FPGA功耗估计和如何进行低功耗设计的知识。##关于FPGA低功耗设计,可从两方面着手:1)算法优化;2)FPGA资源使用效率优化。

2014-12-17 09:27:28 9945

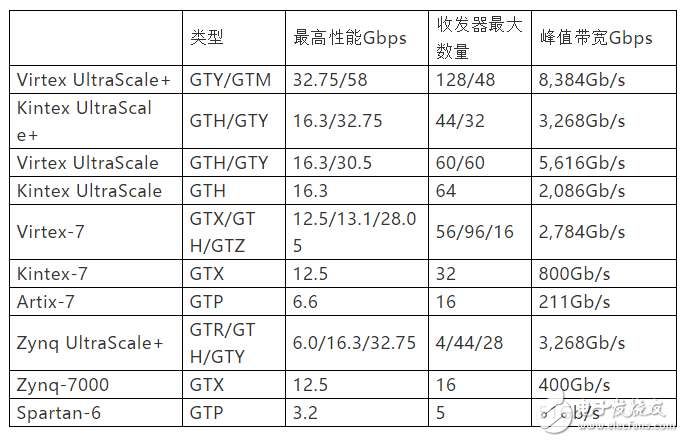

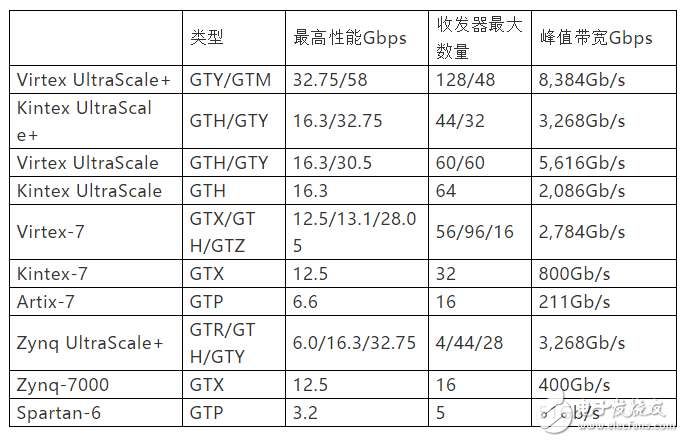

9945 随着系统带宽不断增加至多吉比特范围,并行接口已经被高速串行链接,或SERDES (串化器/ 解串器)所取代。起初, SERDES 是独立的ASSP 或ASIC 器件。在过去几年中已经看到有内置SERDES 的FPGA 器件系列,但多见于高端FPGA芯片中,而且价格昂贵。

2015-02-02 17:32:52 2705

2705

这里将介绍SERDES的基本概念,并介绍SERDES相关的专有名词:眼图(Eye-diagram)、眼图模板、抖动(Jitter)、容忍度(tolerance)、功耗(Power Consumption)、预加重(Pre-emphasis)、均衡(Equalization)、8B/10B编码等。

2018-01-30 08:55:54 24845

24845

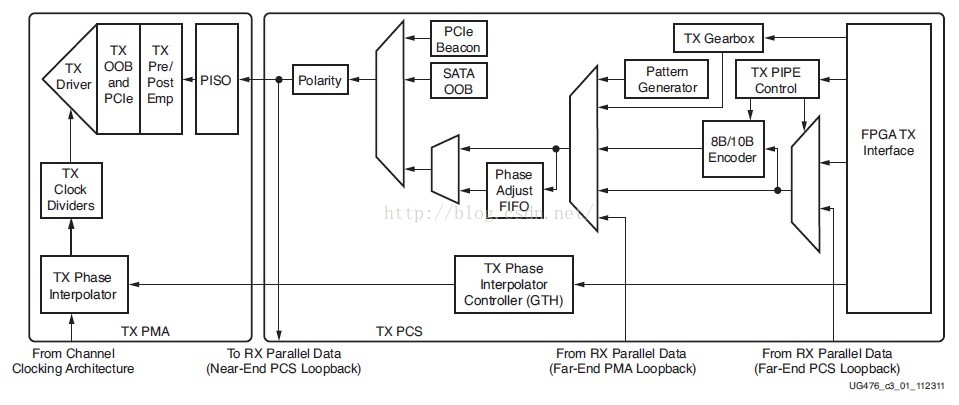

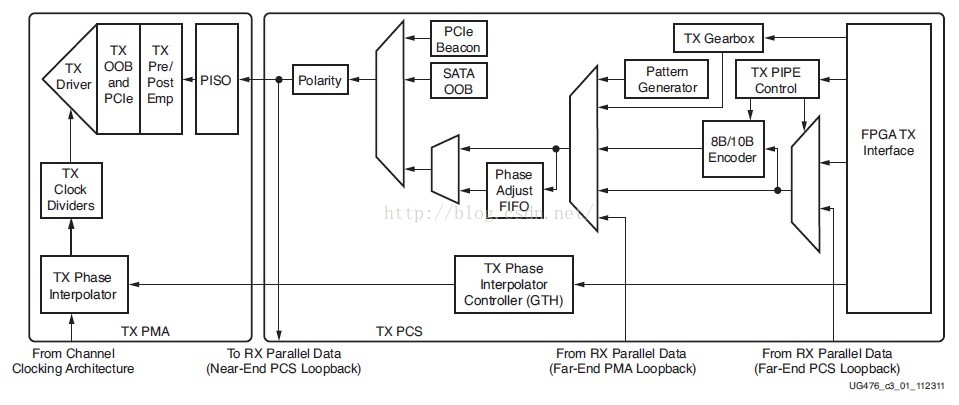

,其中PMA子层包含高速串并转换(Serdes)、预/后加重、接收均衡、时钟发生器及时钟恢复等电路。PCS子层包含8B/10B编解码、缓冲区、通道绑定和时钟修正等电路。对于GTX的发送端来说,结构如图1

2020-11-20 11:27:39 7777

7777

接口下,MAC芯片在将数据发给PHY芯片之前进行了8B/10B变换(8B/10B变换本是在PHY芯片中完成的,前面已经说过了)。 大多数芯片的TBI接口和GMII接口兼容。在用作TBI接口

2023-03-29 15:19:28 8137

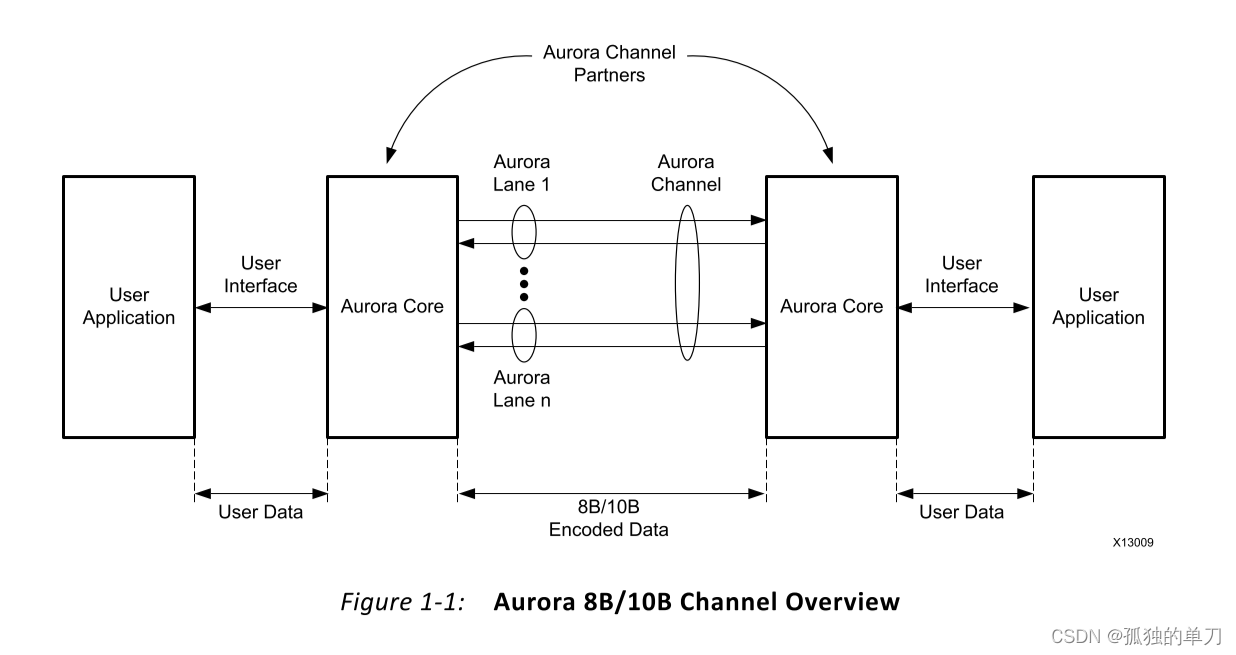

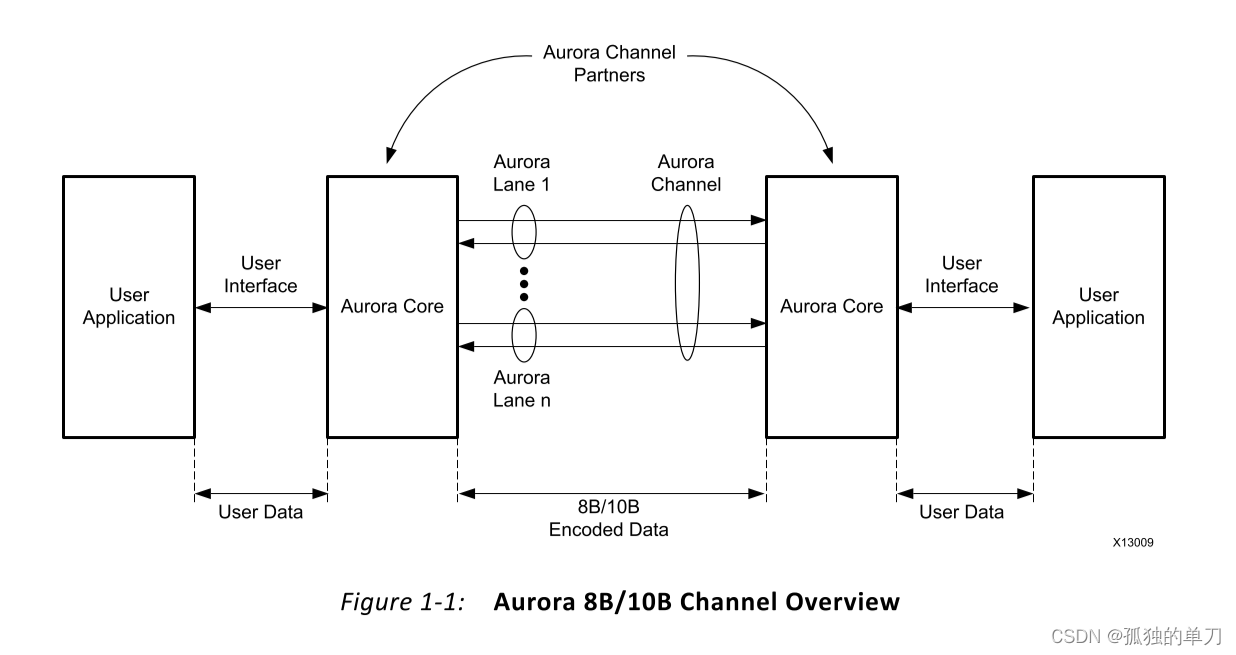

8137 XSTC_8B10B IP(XSTC:XiST Transmission Channel)是智多晶开发的一个灵活的,轻量级的高速串行通信的IP。IP在具备SerDes(单通道或多通道)高速串行收发器之间构建出接口简单,低成本,轻量化的高速率数据通信通道。

2025-04-03 16:30:01 1250

1250

8b/10b编码是一种用于减少数据线上的低效能时钟信号传输的技术,通过在数据流中插入特殊的控制字符,来同步数据和时钟。在Verilog中实现8b/10b编码器可以通过以下步骤完成:

定义8b/10b

2024-03-26 07:55:35

8b/10b编码用的控制字是K28.5,但是解码时用非K28.5的控制字能把数据解码出来吗?

2019-01-02 14:47:15

串行接口常用于芯片至芯片和电路板至电路板之间的数据传输。随着系统带宽不断增加至多吉比特范围,并行接口已经被高速串行链接,或SERDES (串化器/ 解串器)所取代。起初, SERDES 是独立

2019-10-23 07:16:35

数据传输的关键。在FPGA中实现SATA物理层时,需要正确配置GTX(高速串行收发器)模块,包括时钟设置、数据位宽、8B/10B编码等。同时,还需要设计物理层的状态机,以实现数据的串并转换、OOB信号

2024-05-27 16:20:22

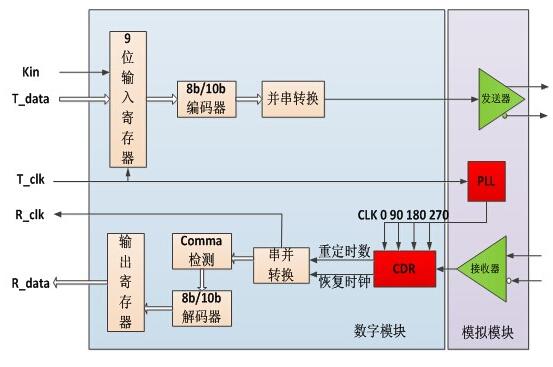

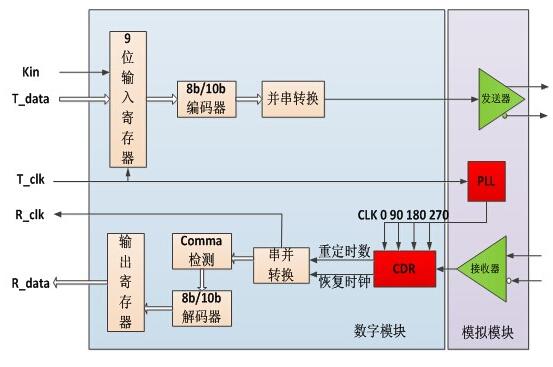

通信,该SERDES接口方案具有成本低、灵活性高、研发周期短等特点。 1 硬件接口: 硬件的接口如上图所示,主要包括发送与接收模块。 发送模块包括8b/10b编码器,并串转换器,锁相环(PLL

2019-05-29 17:52:03

小弟最近在调用Aurora 8b/10b IP模块时,在用modelsim功能仿真时,一切正常。 但是直接使用了例化后的example,并将Tx和Rx形成了回路下到FPGA板子上

2015-03-09 10:58:03

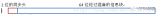

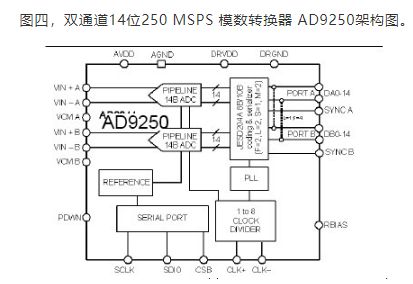

什么是8b/10b编码,为什么JESD204B接口需使用这种编码?怎么消除影响JESD204B链路传输的因素?JESD204B中的确定延迟到底是什么? 它是否就是转换器的总延迟?JESD204B如何使用结束位?结束位存在的意义是什么?如何计算转换器的通道速率?什么是应用层,它能做什么?

2021-04-13 06:39:06

请问各位大侠:JESD204B专用于ADC/DAC和FPGA或ASIC的接口吗,该接口同Rapid/PCIe的物理层Serdes接口有何区别,谢谢!

2025-02-08 09:10:29

问:什么是8b/10b编码,为什么JESD204B接口需使用这种编码?

答:无法确保差分通道上的直流平衡信号不受随机非编码串行数据干扰,因为很有可能会传输大量相反的1或0数据。通过串行链路传输

2024-01-03 06:35:04

【STM32L15xx6/8/B-】本文档是关于ARM® Cortex®-M3内核的超低功耗单片机STM32L151x6/8/B-A,STM32L152x6/8/B-A的数据手册。特征:超低功率平台

2022-11-28 08:06:54

大家好,我正在使用带有8B / 10B的Spartan-6 GTP传输32位数据,并使用光纤外部FPGA,当我将代码下载到芯片时,它是正确的,但在IPull输出光纤后立即插入电源(我称之为热插拔

2020-03-18 10:02:58

我们5805的I2C地址配置的是7b:2D,8b:5A,怎么出来是7b:2F,8b:5E?这个是什么原因?

DVDD: 1.8V

2024-10-18 07:41:01

嗨,我试图在Zynq 7015中使用GTX来制作一个简单的传输仅使用8B10B编码的serdes。我有Vivado 2014.4,我在PicoZed SOM上测试。我有一个200Mhz LVDS信号

2020-07-31 09:10:30

。此外,可通过8B/10B解码错误状态实时确定SERDES链路质量。伪随机位序列(PRBS)提供了一个测量高速链路中信号质量和抖动容差的有用资源。大部分FPGA 中的SERDES收发器都内置了PRBS

2018-10-16 06:02:44

数据的8b/10b编解码、高速串并转换,以及CPRI协议的成帧、解帧、同步、传输数据复/分解等操作。FPGA的控制作用主要是针对光接口模块和PHY模块。对于光接口模块,由于XFP提供一个两线的串行接口

2019-06-04 05:00:18

Gb/s传输给FPGA。在该数据流传输中,由于FPGA对数据进行8b/10b编解码,因此有效码率是10 Gb/s,能够满足本文的设计要求,可以实现10G以太网的数据流传输。时钟模块:时钟模块内采用

2019-05-31 05:00:06

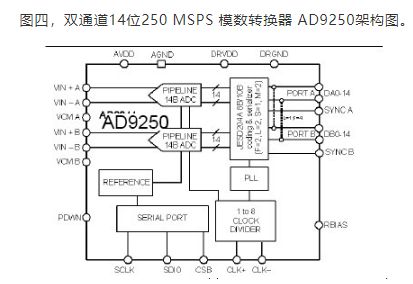

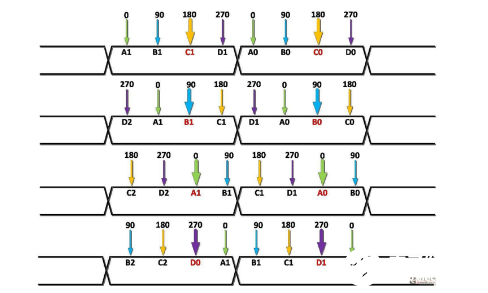

的协议会定义特殊的码型(常见的码型如8B/10B编码中的K28.5)用于字对齐处理。另一些带源同步时钟的LVDS接口,通常会利用低频的源同步时钟来携带字对齐信息,用于接收端的正确恢复。FPGA对上述两种

2019-07-29 07:03:50

高速LVDS数据传输方案和协议基于FPGA的高速LVDS数据传输本人在北京工作6年,从事FPGA外围接口设计,非常熟悉高速LVDS数据传输,8B/10B编码等,设计调试了多个FPGA与FPGA以及

2014-03-01 18:47:47

你好,我正在尝试使用Aurora 8B / 10B建立仅传输(流媒体)。现在使用Vivado 2014.4进行模拟阶段。我知道GTXE2_COMMON原语需要在设计中使用以包含一个QUAD PLL

2020-08-14 08:49:13

Serdes向导中使用了不正确的设置吗?我在Comma Alignment上附上了Wizard页面的屏幕截图。作为附件。注意:我们在Serdes之外做8b / 10b,所以我们在没有解码的情况下查看原始数据。查克王尔德NEOTECH

2020-08-21 11:05:45

的模数转换器(ADC)和数模转换器(DAC)支持最新的JESD204B串行接口标准,出现了FPGA与这些模拟产品的最佳接口方式问题。FPGA一直支持千兆串行/解串(SERDES)收发器。然而在过去,大多数ADC

2021-04-06 09:46:23

本方案是以CME最新的低功耗系列FPGA的HR03为平台,实现8/10b的SerDes接口,包括SERDES收发单元,通过完全数字化的方法实现SERDES的CDR(Clock Data

2019-10-21 07:09:44

大家好,我使用的是Vivado 2016.4和Virtex 7 XC7VX485T FPGA。我需要知道是否有一个选项可以禁用Aurora IP Core 8B / 10B中的时钟补偿功能。我可以看到IP核心文件,但它们都是只读的。谢谢,马诺

2020-08-18 09:43:40

以及所针对的最终应用。并行数据通常将编码为标准编码方案(例如 8B/10B 编码),因而适用于串行化。原始应用数据可能包含病态模式、长期运行的 1 和 0,这会使串行解串器难以捕捉位跳变。对数据进行

2018-09-13 09:54:18

亲爱的先生,我正在使用Vivado 2015.4。我想在收发器向导中使用通道绑定,但CB在手册中是灰色的。另外,我找不到在收发器向导中启用8b / 10b编码器的方法。如果你能给我一些建议,我将不胜感激。问候,泰迪王

2020-08-04 08:32:57

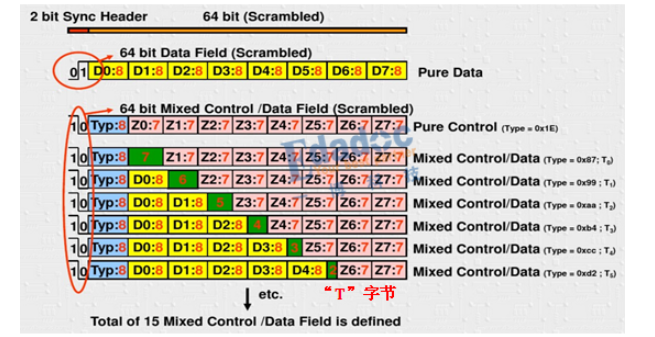

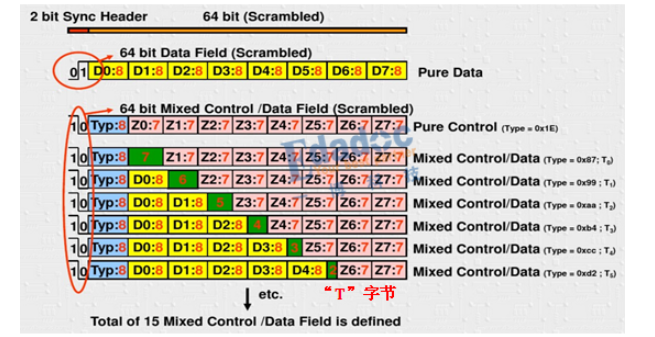

作者:黄刚上文说完了8B/10B之后,我们再来说说貌似更复杂的64B/66B编码。很多人可能在想,8B/10B编码主要作用的优化直流平衡,从8bit中插2个bit进去,这样的话最终效果能够使长0或者

2019-07-19 07:35:57

大家好,Vivado版本:15.2FPGA:Artix 7 xc7a50tAurora 8b / 10b IP v11.0(Rev 1) - 使用VHDL创建车道:1我最近一直面临着Aurora

2020-08-06 09:34:12

Hi~,我想请问一下204B接口的各个层次,例如transport layer,link layer...里面的8B/10B,scrambler...的内建测试模式和测试模板(test parten)方面的资料,应该参考什么呢?

2025-01-20 09:05:37

关于ARM® Cortex®-M3超低功耗单片机STM32L15xx6/8/B的数据手册, 介绍了它的主要外设资源和电特性参数。特征:超低功率平台1.65V至3.6 V电源-40°C至85°C

2022-11-28 07:01:54

后,经过8B/10B编码,并/串变换等处理步骤,以串行差分信号的形式输出到光电转换子模块。为了保证PL4接口达到十路1Gbps的速率,PM3388的参考时钟引脚接160MHz时钟晶振,输入输出接口

2019-04-29 07:00:07

(旁路)。 T M D S信号传输使用对本协议唯一的四个对齐的字符(不同于8B/10B方式)。串行器与SERDES的CDR传递10位的原始数据,FPGA进行字节对齐。 DVI/HDMI链路连接能以多个

2019-06-06 05:00:34

一、高速接口8B/10B的作用? 在数字通信中编码和加扰的作用是不同的。编码通常有信源编码和信道编码,8b/10b是信道编码,信道编码的作用是通过增加冗余(此外冗余为2b)以提高数据传输的可靠性。加

2022-01-18 06:16:43

作者:黄刚前面文章说过,在高速链路中导致接收端眼图闭合的原因,很大部分并不是由于高频的损耗太大了,而是由于高低频的损耗差异过大,导致码间干扰严重,因此不能张开眼睛。针对这种情况,前面有讲过可以通过CTLE和FFE(包括DFE)均衡进行解决,原理无非就是衰减低频幅度或者抬高高频幅度,从而达到在接收端高低频均衡的效果。同时我们在前文还埋了个伏笔:

2019-07-19 07:45:29

采用Xilinx 公司Virtex- II Pro 系列FPGA 内嵌得SERDES 模块———RocketIO 作为高速串行协议的物理层, 利用其8B/10B的编解码和串化、解串功能, 实现了两板间基于数据帧的简单高速串行传输

2010-09-22 08:44:28 28

28 摘要:为提高8B/10B编解码的工作速度和简化逻辑方法,提出一种基于FPGA的8B/10B编解码系统设计方案。与现有的8B/10B编解码方案相比,该方案是一种利用FPGA实现8B/lOB编解码的模块方

2011-05-26 11:08:20 4329

4329

Xilinx FPGA工程例子源码:Xilinx 提供的高速多状态编码8b_10b编码器

2016-06-07 15:07:45 26

26 了解如何将串行收发器应用到您的 7 系列 FPGA 设计中。了解并利用串行收发器模块的特性:如 8B/10B 和 64B/66B 编码、通道绑定、时钟校正和逗点检测。其它专题包括

2017-02-09 02:20:12 328

328 了解如何在您的 UltraScale™ FPGA 设计中部署串行收发器。了解并利用串行收发器模块的特性,如 8B/10B 和 64B/66B 编码、通道绑定、时钟校正和逗点检测。其它专题

2017-02-09 08:04:41 467

467 一种基于低成本FPGA的高速8B_10B编解码器设计_陈章进

2017-03-19 11:46:13 1

1 (Pseudo Random Binary Sequence,PRBS)检测方法对该编码器进行验证。FPGA综合结果表明,该设计占用的LUT为32,占用较少的逻辑资源。采用PIU3S-7测试结果表明,该8B/10B编码电路误码率为O,表明了该8B/10B编码器传输信息的可靠性。

2017-11-06 17:04:21 7

7 为降低成本,提高设计灵活性,提出一种基于FPGA的1553B总线接口方案;采用自顶向下的设计方法,在分析1553B总线接口工作原理和响应流程的基础上,完成了接口方案各FPGA功能模块设计;对关键模块

2017-11-17 13:47:25 23359

23359 针对较为常用的Aurora 8B/10B和PCI Express 2.0,Serial RapidIO 2.0三种协议进行了测试及对比分析。首先搭建了基于Virtex-6 FPGA的高速串行协议测试

2017-11-18 01:00:06 13369

13369

随着更多的模数转换器(ADC)和数模转换器(DAC)支持最新的JESD204B串行接口标准,出现了FPGA与这些模拟产品的最佳接口方式问题。FPGA供应商多年来一直支持千兆串行/解串(SERDES

2017-11-18 01:48:02 1816

1816 HES5B/8B系列以太网交换机是一系列入门级5口或8口工业非网管以太网交换机,支持IEEE802.3/802.3u/802.3x,lO/lOOM,全/半双工,MDI/MDI-X自适应RJ45端口

2017-11-20 17:15:34 11

11 Microsemi公司的SmartFusion2 SoC FPGA是低功耗FPGA器件,集成了第四代基于闪存FPGA架构,166MHz ARM Cortex-M3处理器和高性能通信接口,是业界最低功耗

2018-05-14 14:20:00 9622

9622

GTx接收和发送方向均由PCS和PMA两部分组成,PCS提供丰富的物理编码层特性,如8b/10b编码等;PMA部分为模拟电路,提供高性能的串行接口特性,如预加重与均衡。

2018-06-29 08:47:00 11290

11290

为了提高串行数据传输的可靠性,现在很多更高速率的数字接口采用的是对数据进行编码后再做并串转换的方式…

2018-03-14 16:23:59 18523

18523 看看LatticeECP3 FPGA的功耗是多么的低,无论是在实验室中测量,还是利用莱迪思的功耗计算器软件计算。 LatticeECP3是业界最低功耗的配备SERDES的FPGA。

2018-06-15 13:36:00 5850

5850

本文档的主要内容详细介绍的是8B10B译码和编码的FPGA源代码资料免费下载。

2018-09-03 08:00:00 62

62 关键词:FPGA , 低功耗 , RTL 在项目设计初期,基于硬件电源模块的设计考虑,对FPGA设计中的功耗估计是必不可少的。笔者经历过一个项目,整个系统的功耗达到了100w,而单片FPGA的功耗

2018-09-07 14:58:01 790

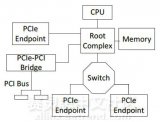

790 需要注意的是PCIe Spec并没有规定弹性缓存的具体位置,设计者可以将弹性缓存放在8b/10b解码器之前,也可以把弹性缓存放在8b/10b解码器之后。不过,Mindshare的建议是将弹性缓存放置于8b/10b解码器之前的。

2018-09-08 09:59:41 7245

7245

本方案是以CME最新的低功耗系列FPGA的HR03为平台,实现8/10b的SerDes接口,包括SERDES收发单元,通过完全数字化的方法实现SERDES的CDR(Clock Data

2019-05-24 15:33:25 5411

5411

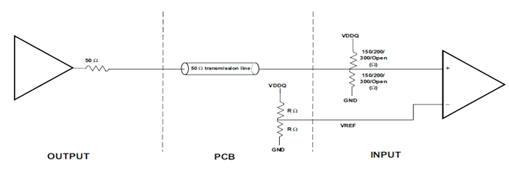

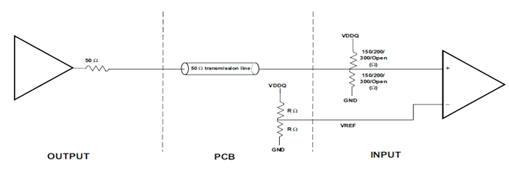

8b/10b编码器用于将从上层协议芯片发送过来的字节信号映射成直流平衡的 10 位8b/10b 编码,并串转换用于将 10 位编码结果串行化,并串转换所需的高速、低抖动时钟由锁相环提供,发送器用于将 CMOS 电平的高速串行码流转换成抗噪声能力较强的差分信号,经背板连接或光纤信道发送到接收机。

2019-05-27 14:31:09 6120

6120

串行互连接口的速率在过去几年里得到了显著提高,每线的速率从2.5Gbit/s提高到10Gbit/s,而每个接口可以容纳1到32线。8B10B作为互连接口的一种编码技术,设计简单、性能出众,因此成为

2020-04-12 11:06:52 6750

6750

总线而成为高速接口设计的主流。 如今,随着SerDes接口的广泛应用,许多高端的FPGA都内嵌有SerDes接口硬核。在FPGA中内嵌的SERDES的硬核,可以大大地扩张FPGA的数据吞吐量,节约功耗,提高性能,使FPGA在高速系统设计中扮演着日益重要的角色。 国产

2020-07-28 12:05:16 1726

1726 USB3.0中的新技术 •全双工传输; •8B/10B编码和加入PRBS扰码; •扩频时钟(SSC)技术; •去加重(De-emphasis)技术; •均衡技术(Equalization); •电源管理技术;

2020-09-23 08:00:00 0

0 功耗是各大设计不可绕过的话题,在各大设计中,我们应当追求低功耗。为增进大家对低功耗的认识,本文将对FPGA低功耗设计予以介绍。如果你对FPGA低功耗相关内容具有兴趣,不妨继续往下阅读哦。 FPGA

2020-10-28 15:02:13 3673

3673 很多人可能在想,8B/10B编码主要作用的优化直流平衡,从8bit中插2个bit进去,这样的话最终效果能够使长0或者长1的位数不超过5位,达到很好的效果。那64B/66B编码方式呢?在从64个bit

2021-04-01 12:01:38 9977

9977

我在2015年底到2016年初的时候,使用7 Series FPGA Transceivers完成了TS流数据的传输,当时使用的传输速度为3.125G,SerDes选取的是8b/10b编码方式

2020-12-30 17:24:00 31

31 下面详细介绍了6个功能模块及其应用特点:并行接口、串行接口、时钟分布电路、8B/10B编解码电路、PRBS测试以及相关寄存器访问控制接口MDIO。

2021-06-26 16:10:42 7686

7686

论序 8b/10b编码/解码是高速串行通信,如PCle SATA(串行ATA),以及Fiber Channel中常用的编解码方式。在发送端,编码电路将串行输入的8比特一组的数据转变成10比特一组

2021-09-26 09:56:22 10820

10820

Aurora 协议是一个用于在点对点串行链路间移动数据的可扩展轻量级链路层协议(由Xilinx开发提供)。这为物理层提供透明接口,让专有协议或业界标准协议上层能方便地使用高速收发器

2022-02-16 16:21:24 11012

11012

8b/10b最常见的是应用于光纤通讯和LVDS信号的。由于光模块光模块只能发送亮或者不亮,也就是0或者1这两种状态这种单极性码,那么这会存在一个问题,如果传输中出现较长的连0或者连1(例如

2022-11-12 15:47:27 17676

17676 IP_数据表(A-11):双通道 8b D/A 转换器

2023-03-16 19:28:52 0

0 R0E3308B0EPB00 用户手册 (Emulation Probe for M32C/8B 组)

2023-04-18 19:03:42 0

0 R0E3308B0EPB00 Supplementary Document (Emulation Probe for M32C/8B 组)

2023-04-18 19:04:32 0

0 E8a Emulator Additional Document for 用户手册 (Notes on Connecting the M32C/8B)

2023-04-19 19:15:48 0

0 M32C/8B 组数据表

2023-04-20 18:56:32 0

0 M32C/8B群硬件手册

2023-04-20 18:57:22 0

0 8B/10B 编码数据对时钟恢复电路很友好,因为它具有游程长度限制。它还适用于交流耦合,因为它是直流平衡的。8B/10B 编码涉及将 8 位八位字节转换为 10 位代码组。在每个代码组中,1 和 0 的数量之差绝不会超过两个。通过监测连续代码组中 1 和 0 的数量,计算出运行差异。

2023-04-29 16:34:00 1088

1088

采用8b/10b编码方式,可使得发送的“0”、“1”数量保持基本一致,连续的“1”或“0”不超过5位,即每5个连续的“1”或“0”后必须插入一位“0”或“1”,从而保证信号DC平衡,也就是说,在链路超时时不致发生DC失调。

2023-05-16 12:29:15 5486

5486

利用8b/10b编码,采用嵌入式时钟,这样便无需路由额外的时钟线路,以及相关的高数据速率下传输的数据与额外的时钟信号对齐的复杂性。

2023-06-17 09:53:39 1160

1160

IP_数据表(A-11):双通道 8b D/A 转换器

2023-07-06 20:15:10 0

0 摘要:莱迪思(Lattice )半导体公司在这应用领域已经推出两款低成本带有SERDES的 FPGA器件系列基础上,日前又推出采用富士通公司先进的低功耗工艺,目前业界首款最低功耗与价格并拥有SERDES 功能的FPGA器件――中档的、采用65nm工艺技术的 LatticeECP3系列。

2023-10-27 16:54:24 1208

1208 的ASSP 或ASIC 器件。在过去几年中已经看到有内置SERDES 的FPGA 器件系列,但多见于高端FPGA芯片中,而且价格昂贵。 本方案是以CME的低功耗系列FPGA的HR03为平台,实现8

2023-07-27 16:10:01 4205

4205

本文开源一个FPGA高速串行通信项目:Aurora 8b10b光通信。7 Series FPGAs Transceivers Wizard IP是Xilinx官方7系列FPGA的高速串行收发器,本工程主要是围绕该IP核采用Vivado提供的例程创建。

2023-10-01 09:48:00 9986

9986

光缆8D与8B的主要区别体现在其结构、光纤类型以及应用场景上。以下是对两者的详细比较: 一、结构差异 GYTY53-8D光缆: 是一种充满油脂的松散层绞合室外光缆。 内护套由聚乙烯制成,外护套为钢

2024-10-30 10:13:58 1737

1737 算能BM1684X上完成Qwen3-VL4B/8B模型的适配,推理速度13.7/7.2tokens/s,使其成为边缘部署多模态大模型的最佳选择。近日,阿里千问正式开源Qwen3-VL系列的4B和8B

2025-10-16 18:00:07 2145

2145

SN65LVDS93B:低功耗、高分辨率的LVDS SerDes发送器的理想选择 在电子设备的显示系统中,数据的高效传输和显示质量的保障至关重要。SN65LVDS93B作为一款LVDS SerDes

2025-12-18 11:35:12 252

252

电子发烧友App

电子发烧友App

评论