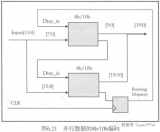

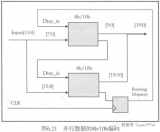

为了在USB 3.0中实现数据的8 b/10 b编解码,把8b/10b编解码分解成5 b/6 b编解码和3 b/4 b编解码,然后在FPGA上实现了具体的硬件电路。

2011-11-30 11:38:18 2803

2803

语音编解码器技术的发展一定程度上处于静止状态,但音频编解码器技术一直在向前演进。音频编解码器朝更多的环绕声通道发展就是一个趋势。

2012-02-03 16:17:11 4774

4774 16B 20B编解码 Xilinx提供1

2012-08-10 18:01:22

概述: 随着手机、MP3、MP4等便携多功能设备市场日渐繁荣,音频解码IC的发展也不断扩大。目前以数字编解码最为常见,这一过程可以通过软件进行,也可以通过硬件进行,或者二者相结合。因为音频在很多系统

2021-05-17 07:58:52

53小波的EZW压缩编解码FPGA实现,有了解的麻烦指点下,谢谢!

2014-06-22 11:25:36

10G以太网系统中的并行CRC编解码器的设计

2012-08-10 17:59:00

8b/10b编码用的控制字是K28.5,但是解码时用非K28.5的控制字能把数据解码出来吗?

2019-01-02 14:47:15

求助用FPGA进行视频编解码,可行吗?尤其在高清领域,FPGA强大的计算能力似乎很有优势,但算法极其复杂,各位高手指点指点。

2009-02-06 09:40:04

编解码器是用于对数字媒体文件(如歌曲或视频)进行压缩或解压缩的软件。Windows Media Player 和其他程序使用编解码器来播放并创建数字媒体文件。

2020-04-06 09:00:42

AKD4951EG-B,AK4951EG 24位编解码器评估板,内置PLL和MIC / HP / SPK放大器。 AKD4951EG-B具有与AKM的A / D评估板的接口。因此,很容易评估

2019-04-18 09:25:55

小弟最近在调用Aurora 8b/10b IP模块时,在用modelsim功能仿真时,一切正常。 但是直接使用了例化后的example,并将Tx和Rx形成了回路下到FPGA板子上

2015-03-09 10:58:03

你好, 我正在使用Aurora 8B / 10B v5.3 IP内核,Virtex 5 FPGA用于使用SFP电缆的GB收发器。我使用核心生成器创建了IP核,获得了示例设计(所有文件)。我模拟了示例

2020-04-07 14:52:25

的,以IP核的形式,在FPGA器件上运行,基于FPGA的解决方案使用FPGA为核心器件,实现H.264编解码的IP核,此解决方案为纯硬件的解决方案,启动时间可以忽略,编解码延迟为固定的延迟,在一定

2018-05-07 17:14:42

什么是8b/10b编码,为什么JESD204B接口需使用这种编码?怎么消除影响JESD204B链路传输的因素?JESD204B中的确定延迟到底是什么? 它是否就是转换器的总延迟?JESD204B如何使用结束位?结束位存在的意义是什么?如何计算转换器的通道速率?什么是应用层,它能做什么?

2021-04-13 06:39:06

数据处理以便串行解码8b/10b数据,并在示波器屏幕上显示未编码数据流。采用这种方法可以探测未加扰数据,从而确定链路上正在进行何种活动。FPGA供应商提供内部探测软件工具,通过一个USB加密狗将其与计算机相连

2024-01-03 06:35:04

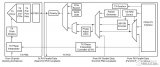

)频率合成器和发送器,接收模块包括 8b/10b解码器,Comma 检测器,串并转换器,时钟数据恢复器(CDR)和接收器。 8b/10b编码器用于将从上层协议芯片发送过来的字节信号映射成直流平衡

2019-05-29 17:52:03

大家好,我正在使用带有8B / 10B的Spartan-6 GTP传输32位数据,并使用光纤外部FPGA,当我将代码下载到芯片时,它是正确的,但在IPull输出光纤后立即插入电源(我称之为热插拔

2020-03-18 10:02:58

通道上最大记录长度为 32 M样点- 在所有四条通道上实时取样速率为 20 GS/s- 高达 3.125 Gb/s的串行码流触发功能,支持 8b/10b 协议触发 - 串行数据分析和一致性测试,提供 Windows XP操作系统的内置联网- 速率可达 6.25 Gb/s 及更高 OpenChoice?软件

2022-03-09 14:51:57

不知道大家对这个有没有兴趣,可以来讨论一下我暂时对这个还不了解,先看看哈[此贴子已经被admin于2008-7-18 13:08:55编辑过]

2008-07-18 09:27:44

)====================================================================版权归作者所有,未经允许,请勿转载。====================================================================一、opus编解码简介Opus是一个完全开放,免版税,高度通用的音频编解码器。在互联网上Opus是交互式语音和音乐传输,也

2021-12-24 06:56:37

)。本文介绍了一种读写器的编解码部分由FPGA来完成的设计方案,由FPGA负责前向链路的PIE编码和后向链路的FM0/miller解码,且解码模块可对标签突发传来的数据立即检测并实施解码,实现了较快的解码速率。FPGA选用的是Altera公司的EP1C3T100C6芯片。

2019-07-26 06:47:39

PCI Express increases data transport efficiency and data quality. It uses an 8b/10b encoding methodology to embed the clock signal ...

2019-09-23 11:01:40

二者都是使用的8b/10b编解码(内部位宽不同,GTP选择的是10,GTX选择的是20)。选择相同的协议,其它选择默认设置,使用光纤进行相互之间的传输。接收端接收数据始终不对(观察为51个64位

2014-09-22 16:29:54

小弟最近在做2013年国赛题目红外通信装置,其实核心就是对音频信号进行PCM编解码,其中我们用到了MC14LC5480这款PCM编解码芯片,其中有几个疑问1.看全英文的文档介绍说有四种工作模式,但我

2016-03-15 11:30:37

初识红外编解码

2021-08-16 06:35:47

Xilinx FPGA上的JESD204B发送器和接收器框图。发送器/接收器通道实现加扰和链路层;8B/10B编码器/解码器和物理层在GTP/GTX/GTHGbit 收发器中实现。图4. 使用Xilinx

2018-10-16 06:02:44

我正在尝试使用Xaui协议的4.25Gbps和使用Zynq zc706板的PCIE。我遵循以下步骤1)生成7系列收发器向导(4.25Gbps,XAUI协议,8b / 10b编码器和解码器以及PCIe

2020-05-22 15:27:40

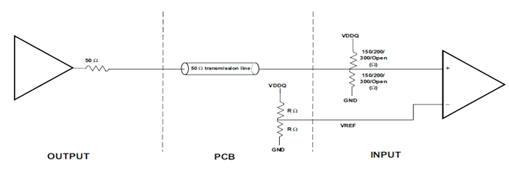

路,以3.125 Gb/s传输给FPGA。在该数据流传输中,由于FPGA对数据进行8b/10b编解码,因此有效码率是10 Gb/s,能够满足本文的设计要求,可以实现10G以太网的数据流传输。时钟模块

2019-06-04 05:00:18

Gb/s传输给FPGA。在该数据流传输中,由于FPGA对数据进行8b/10b编解码,因此有效码率是10 Gb/s,能够满足本文的设计要求,可以实现10G以太网的数据流传输。时钟模块:时钟模块内采用

2019-05-31 05:00:06

本帖最后由 zengkf0102 于 2016-4-18 10:21 编辑

最近看到一个朋友做这个,我就上网查了下资料也学习着编写这个代码,由于本人初学FPGA,就是学习然后

2016-04-15 21:54:08

基于FPGA的HDB3编解码系统,谁有这方面的资料,谢了!

2013-04-07 15:14:45

Modelsim进行时序仿真,并用综合工具Synplify对设计进行综合、优化,最后在FPGA上实现编解码技术,提高了测井系统通信的实时性、可靠性。【关键词】:曼彻斯特编解码;;B总线;;FPGA;;DSP

2010-05-13 09:07:52

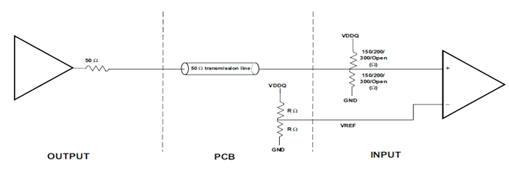

的协议会定义特殊的码型(常见的码型如8B/10B编码中的K28.5)用于字对齐处理。另一些带源同步时钟的LVDS接口,通常会利用低频的源同步时钟来携带字对齐信息,用于接收端的正确恢复。FPGA对上述两种

2019-07-29 07:03:50

高速LVDS数据传输方案和协议基于FPGA的高速LVDS数据传输本人在北京工作6年,从事FPGA外围接口设计,非常熟悉高速LVDS数据传输,8B/10B编码等,设计调试了多个FPGA与FPGA以及

2014-03-01 18:47:47

缓冲区。为了正确有效地完成这个任务,接口控制芯片的硬件部分实现以下一些功能:缓冲到缓冲的流量控制、链路级别的差错检测和恢复、字同步、有序集检测、帧提取、8B/10B编解码和串并/并串转换等功能。接口

2019-05-22 05:01:15

求助!大佬们,问一下用FPGA实现卷积码编解码的难度。

2023-10-16 23:26:26

你好,我正在尝试使用Aurora 8B / 10B建立仅传输(流媒体)。现在使用Vivado 2014.4进行模拟阶段。我知道GTXE2_COMMON原语需要在设计中使用以包含一个QUAD PLL

2020-08-14 08:49:13

ADPCM算法及其编解码器原理是什么?如何去设计ADPCM语音编解码电路?

2021-05-06 06:37:15

本方案是以CME最新的低功耗系列FPGA的HR03为平台,实现8/10b的SerDes接口,包括SERDES收发单元,通过完全数字化的方法实现SERDES的CDR(Clock Data

2019-10-21 07:09:44

REF clk 125MHz 外部数据宽度为16位 内部数据宽度为20位 编码/解码8b / 10b TX,RX PLL通道PLL 均衡模式 - LPM-Auto 环回 - “010” - 近端PMA谢谢。

2020-07-30 09:13:10

大家好,我使用的是Vivado 2016.4和Virtex 7 XC7VX485T FPGA。我需要知道是否有一个选项可以禁用Aurora IP Core 8B / 10B中的时钟补偿功能。我可以看到IP核心文件,但它们都是只读的。谢谢,马诺

2020-08-18 09:43:40

亲爱的先生,我正在使用Vivado 2015.4。我想在收发器向导中使用通道绑定,但CB在手册中是灰色的。另外,我找不到在收发器向导中启用8b / 10b编码器的方法。如果你能给我一些建议,我将不胜感激。问候,泰迪王

2020-08-04 08:32:57

有哪位能用FPGA实现G.729语音编解码的协议?初步我们打算外包,如题,如您有把握能做的话,请联系我邮箱qox2009@163.com

2013-06-03 13:01:30

作者:黄刚上文说完了8B/10B之后,我们再来说说貌似更复杂的64B/66B编码。很多人可能在想,8B/10B编码主要作用的优化直流平衡,从8bit中插2个bit进去,这样的话最终效果能够使长0或者

2019-07-19 07:35:57

大家好,Vivado版本:15.2FPGA:Artix 7 xc7a50tAurora 8b / 10b IP v11.0(Rev 1) - 使用VHDL创建车道:1我最近一直面临着Aurora

2020-08-06 09:34:12

我想在我的项目中包含8b / 10b编码器和解码器。当我尝试在Vivado 2013.4中模拟时,我收到以下错误:错误:[VRFC 10-149]'decode_8b10b_rtl'未编译在库

2019-03-04 07:59:53

音视频编解码标准简介

2021-01-21 06:53:21

本人完全未接触过音频编解码,最近因为需要了解了一下音频编解码的芯片,其中均集成了ADC和DAC,想请教一下,音频编解码与ADC和DAC是什么关系?(我理解是:ADC是编码的基础,DAC是解码的基础,解码其实就是将数字量经DAC后生成了模拟量在经运放等恢复音频,不知对否?)

2014-08-07 15:22:30

作者:黄刚前面文章说过,在高速链路中导致接收端眼图闭合的原因,很大部分并不是由于高频的损耗太大了,而是由于高低频的损耗差异过大,导致码间干扰严重,因此不能张开眼睛。针对这种情况,前面有讲过可以通过CTLE和FFE(包括DFE)均衡进行解决,原理无非就是衰减低频幅度或者抬高高频幅度,从而达到在接收端高低频均衡的效果。同时我们在前文还埋了个伏笔:

2019-07-19 07:45:29

一、高速接口8B/10B的作用? 在数字通信中编码和加扰的作用是不同的。编码通常有信源编码和信道编码,8b/10b是信道编码,信道编码的作用是通过增加冗余(此外冗余为2b)以提高数据传输的可靠性。加

2022-01-18 06:16:43

在对G.726 语音编解码标准分析的基础上给出了基于FPGA 的DSP 设计流程,利用MATLAB/Simulink、DSP Builder 和SOPC Builder 工具设计了G.726 语音编解码器,通过仿真实验验证了所设计的编解码器模

2009-11-30 14:59:24 12

12 在对G.726语音编解码标准分析的基础上给出了基于FPGA的DSP设计流程,利用MATLAB/Simulink、DSP Builder和SOPC Builder工具设计了G.726语音编解码器,通过仿真实验验证了所设计的编解码器模型

2010-07-16 15:06:52 18

18 分析了HDB3编解码原理,提出了一种适合于在现场可编程门阵列FPGA上实现的HDB3编译码器的硬件实现方案,在FPGA上完成了布局布线和时序仿真,最后给出了仿真和实验结果。结果表明该方

2010-07-28 17:36:41 32

32 采用Xilinx 公司Virtex- II Pro 系列FPGA 内嵌得SERDES 模块———RocketIO 作为高速串行协议的物理层, 利用其8B/10B的编解码和串化、解串功能, 实现了两板间基于数据帧的简单高速串行传输

2010-09-22 08:44:28 28

28 采用多路复用流水线的思想,设计基于FPGA仿真测试的RS编解码的改进IBM算法,使用Verilog硬件编程语言实现,进一步提高RS编解码器的运行速度及纠错能力,扩大应用范围。系统设计

2010-12-22 17:02:40 25

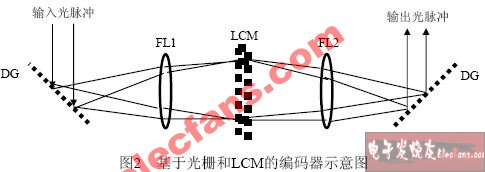

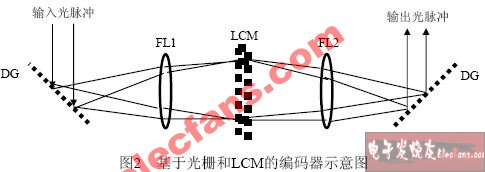

25 频域相位编解码OCDMA系统

基于频域相位编解码OCDMA通信系统如图1所示[3]。频域相位编解码OCDMA通信系统,无论是在实验还是理论方面,相对

2009-02-28 11:32:43 1009

1009

什么是音频编解码器?

编解码器(编码器/解码器)转换成模拟信号的数字码流,另一个相同的编解码器转换为数字流回到成模拟信

2009-05-03 23:48:59 3870

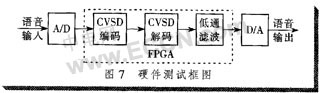

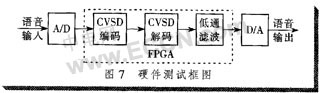

3870 基于FPGA的32Kbit/s CVSD语音编解码器的实现

64 Kbit/s的A律或μ律的对数压扩PCM编码在大容量的光纤通信系统和数字微波系统中已得到广泛应用,但由于占用较大的传输带宽

2010-01-12 09:52:15 729

729

在研究密勒调制副载波序列特点的基础上,提出一种基于FPGA并运用VerilogHDL硬件描述语言实现的密勒调制 副载波 编解码设计方法,并利用Altera公司CycloneI系列EP1C12Q芯片与Verilog HDL硬件描

2011-08-15 11:26:30 33

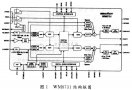

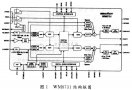

33 介绍了音频编解码芯片WM8731基于FPGA的 接口电路 的设计,包括芯片配置模块与音频数据接口模块等,使得控制器只通过寄存器就可以方便地对其进行操作。整个设计以VHDL和Verilog HDL语言

2011-09-15 11:42:55 11230

11230

设计出基于FPGA的曼彻斯特编解码器是影响整个总线系统通信质量的关键。本设计采用硬件描述语言(Verilog)设计电路,ISE完成综合和布局布线的工作,并用modelSim进行仿真验证。在深入

2011-12-28 10:36:21 95

95 E文JPEG编解码介绍,很好的资料,快来学习吧

2016-02-18 14:14:31 0

0 13曼彻斯特码编解码的FPGA设计与实现-9。

2016-04-26 15:12:57 11

11 RS编解码的FPGA实现-说明RS编解码的FPGA实现-说明。

2016-05-04 15:59:44 21

21 四路编解码电路原理图都是值得参考的设计。

2016-05-11 17:33:19 27

27 基于FPGA的JPEG实时图像编解码系统

2016-08-29 16:05:01 15

15 一种高速卷积编解码器的FPGA实现

2017-02-07 15:05:00 19

19 屏幕视频演示,演示了基于FPGA的视频编解码器在各种Xilinx FPGA评估包上的运行情况,包括: 运行在Artix-7 FPGA上的HDp60 HEVC解码器 运行在Kintex-7 FPGA上的4K

2017-02-09 04:46:30 300

300 一种基于低成本FPGA的高速8B_10B编解码器设计_陈章进

2017-03-19 11:46:13 0

0 通信接口——编解码

2017-09-04 09:39:45 9

9 (Pseudo Random Binary Sequence,PRBS)检测方法对该编码器进行验证。FPGA综合结果表明,该设计占用的LUT为32,占用较少的逻辑资源。采用PIU3S-7测试结果表明,该8B/10B编码电路误码率为O,表明了该8B/10B编码器传输信息的可靠性。

2017-11-06 17:04:21 7

7 针对较为常用的Aurora 8B/10B和PCI Express 2.0,Serial RapidIO 2.0三种协议进行了测试及对比分析。首先搭建了基于Virtex-6 FPGA的高速串行协议测试

2017-11-18 01:00:06 11255

11255

具体特点为:1.支持各种分辨率;2.支持各种帧率;3.编解码延迟低于60ms;4.占用FPGA资源小;5.定制性强.

银亿电子开发的H.264视频编解码解决方案广泛应用于低带宽下、超低延时的星载/机载/弹载/车载视频数据链方面,受到广泛用户一致认可。

2018-05-24 11:45:58 15

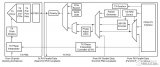

15 ,其中PMA子层包含高速串并转换(Serdes)、预/后加重、接收均衡、时钟发生器及时钟恢复等电路。PCS子层包含8B/10B编解码、缓冲区、通道绑定和时钟修正等电路。对于GTX的发送端来说,结构如图1所示。

2018-06-20 13:48:00 2709

2709

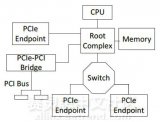

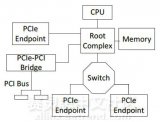

需要注意的是PCIe Spec并没有规定弹性缓存的具体位置,设计者可以将弹性缓存放在8b/10b解码器之前,也可以把弹性缓存放在8b/10b解码器之后。不过,Mindshare的建议是将弹性缓存放置于8b/10b解码器之前的。

2018-09-08 09:59:41 6208

6208

介绍了一种读写器的编解码部分由FPGA来完成的设计方案,由FPGA负责前向链路的PIE编码和后向链路的FM0/miller 解码,且解码模块可对标签突发传来的数据立即检测并实施解码,实现了较快的解码速率。FPGA选用的是Altera公司的 EP1C3T100C6芯片。

2020-07-28 18:54:00 1

1 下面详细介绍了6个功能模块及其应用特点:并行接口、串行接口、时钟分布电路、8B/10B编解码电路、PRBS测试以及相关寄存器访问控制接口MDIO。

2021-06-26 16:10:42 4899

4899

论序 8b/10b编码/解码是高速串行通信,如PCle SATA(串行ATA),以及Fiber Channel中常用的编解码方式。在发送端,编码电路将串行输入的8比特一组的数据转变成10比特一组

2021-09-26 09:56:22 7402

7402

8b/10b最常见的是应用于光纤通讯和LVDS信号的。由于光模块光模块只能发送亮或者不亮,也就是0或者1这两种状态这种单极性码,那么这会存在一个问题,如果传输中出现较长的连0或者连1(例如

2022-11-12 15:47:27 7711

7711 大家好,今天我分享的是走向实用的AI图像编解码。本次将着重从 “走向”两个字出发,阐述AI编解码研发的关键内容和进展。

2023-06-15 09:19:10 465

465

电子发烧友网站提供《密勒调制副载波编解码器的FPGA实现.pdf》资料免费下载

2023-10-26 11:10:21 0

0 编解码一体机是一种集视频编解码、音频编码以及数据传输功能于一体的多媒体设备。这种设备通常基于云计算技术和先进的编解码算法,能够高效地处理视频流,提供低延迟、高稳定性的音视频传输服务。此外,编解码

2024-01-31 14:19:36 168

168

编解码一体机相对于传统的编解码设备具有多个优势。以下是编解码一体机的几个主要优势: 高效实时的视频处理能力:编解码一体机采用先进的编解码算法和云计算技术,能够实现高效、实时的视频处理,满足各种应用场

2024-01-31 14:56:04 291

291

电子发烧友App

电子发烧友App

评论