概述

本文开源一个FPGA高速串行通信项目:Aurora 8b10b光通信。7 Series FPGAs Transceivers Wizard IP是Xilinx官方7系列FPGA的高速串行收发器,本工程主要是围绕该IP核采用Vivado提供的例程创建。

下面主要介绍一下7 Series FPGAs Transceivers Wizard IP核的参数配置以及如何建立该项目Vivado工程。

软硬件平台

软件平台 :Vitis 2019.2;

硬件平台 :XC7Z035FFG676-2;

IP核参数配置

GT Selection

GT Selection相关参数配置保持默认即可;

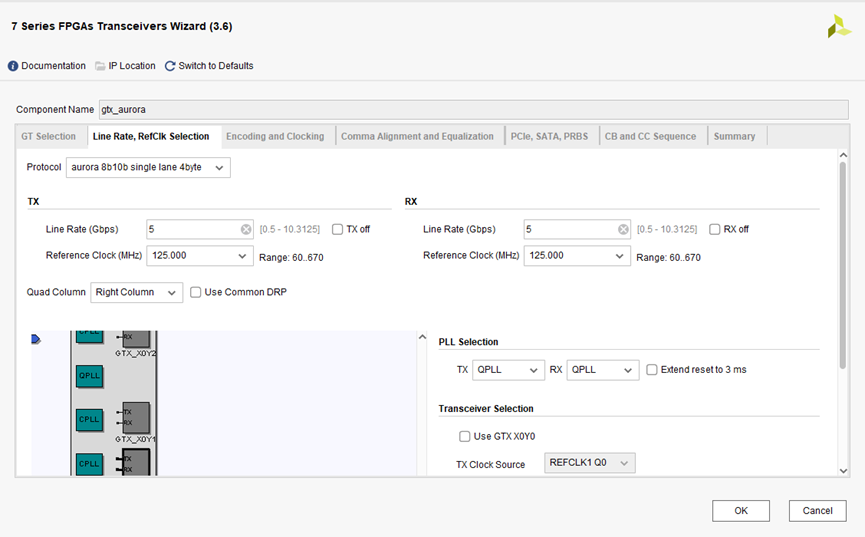

Line Rate, RefClk Selection

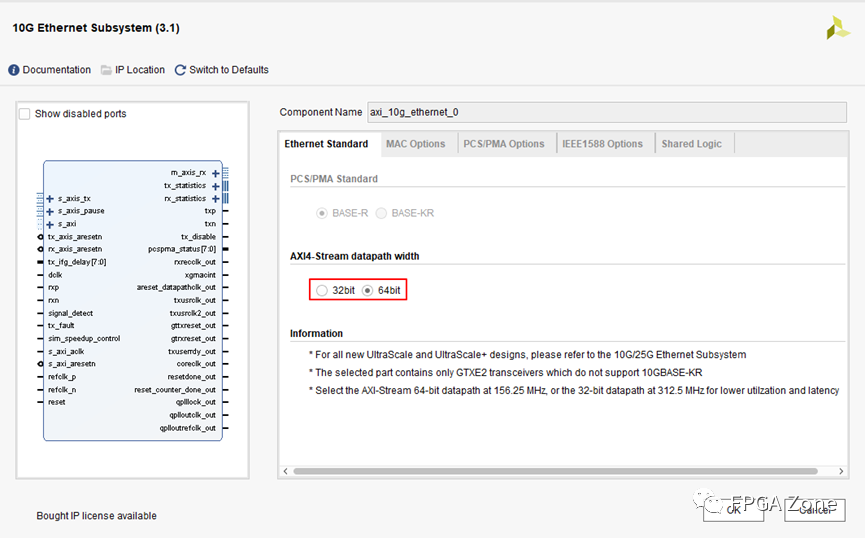

Protocol :此选项下有多种协议可供选择,这里选择 Aurora 8b10b single lane 4bytes,对外接口也就是32位;

TX & RX :收发器是独立的,可以选择不同的编码和速度,对于GTX收发器最大是10.3125Gbps,这里选择5Gbps。参考时钟必须和FPGA板卡上的时钟一致,为125MHz。

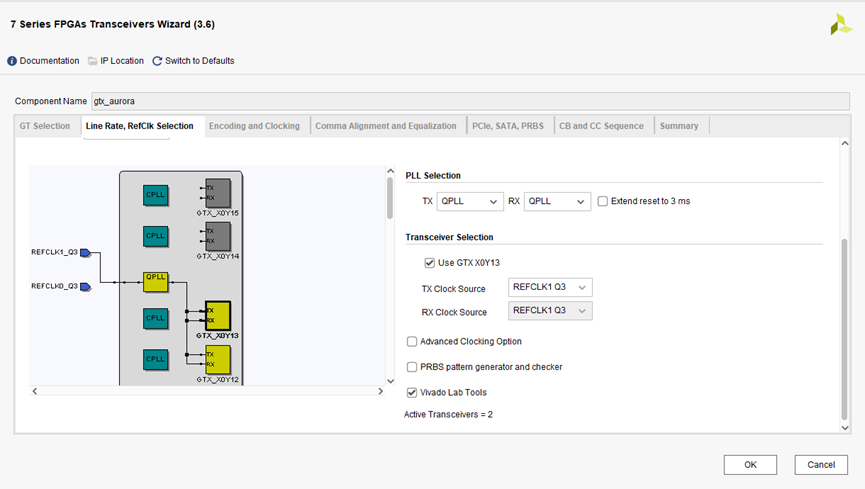

Transceiver Selection :该项目采用的FPGA型号为MK7325,有两个SFP接口,分别连接到GTX_X0Y12和GTX_X0Y13;

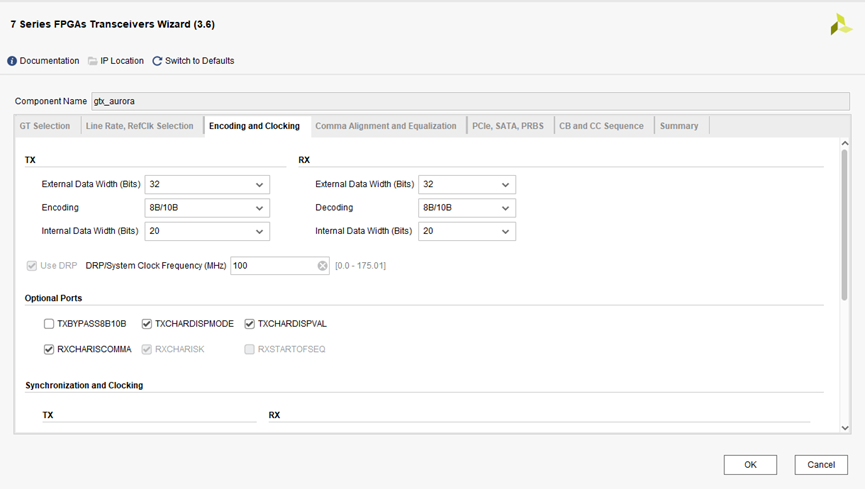

Encoding and Clocking

TX & RX :内部数据宽度设置为20(16bit数据利用8b10b编码为20bits),两个内部数据拼接为1个32bit外部数据,编码方式采用8b10b编码,这种编码方式最主要的目的是保持 直流平衡,根据特定的编码表实现数据传输过程中0和1的数量基本一致,减少连续0或1的情况。DRP/System Clock是动态重配置/系统工作时钟,通过DPR可以根据所配置线速率和协议实时调整收发器参数。DRP时钟频率设置为100MHz,可以通过外部PLL产生,利用DRP时钟初始化一些GTX控制器信号或者参数;

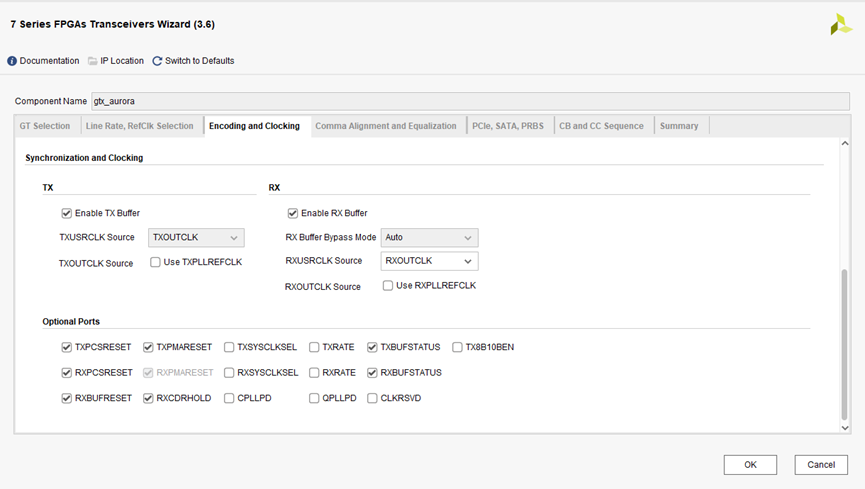

Synchronization and Clocking :TXUSERCLK,和 RXUSERCLK 时钟的选择一般TXUSERCLK可以直接选择TXOUTCLK作为用户时钟,而RXUSERCLK可以选择TXOUTCLK也可以选择RXUSERCLK,还可以选择RXPLLREFCLK作为用户时钟。这里就涉及到一个同步的概念,如果时钟不一致必须设置TX和RX的 BUFFER,默认都是设置的。另外输入TX的发送时钟和RX的恢复时钟差异交大,可能会导致RX BUFFER的溢出或者读空,而导致数据出错。比较好的解决办法就是设置RXUSERCLK为RXOUTCLK,就是利用恢复时钟作为用户时钟,这样就很好的解决了同步的问题了。

Comma Alignment and Equalization

Comma Value :设置K码为K28.5,K码用于修正数据对齐,其它选项保持默认配置即可;

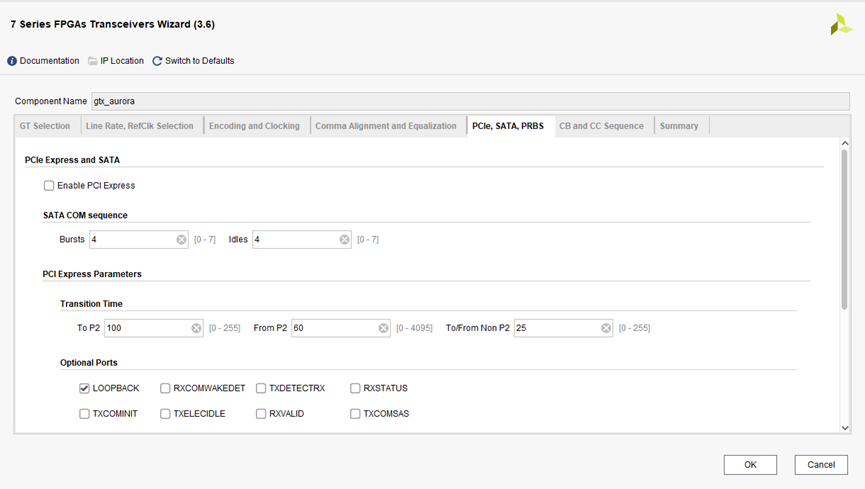

PCIe SATA PRBS

保持默认配置即可;

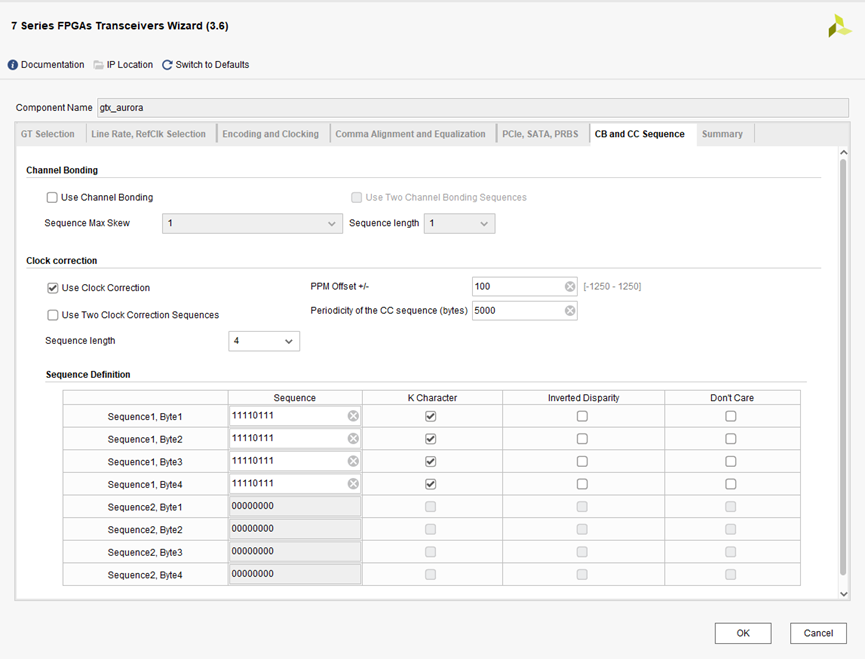

CB and CC Sequence

Clock correction :选择支持时钟校准,设置每5000个字节发送一组CC Seq,因为从数据流中恢复出来的时钟和本地产生的FIFO读侧的时钟的频率不可能完全一致,所以才要进行CC处理。这个周期是根据发送侧和接收侧的时钟差算出来,然后再根据实际调试结果进行一定的修正。

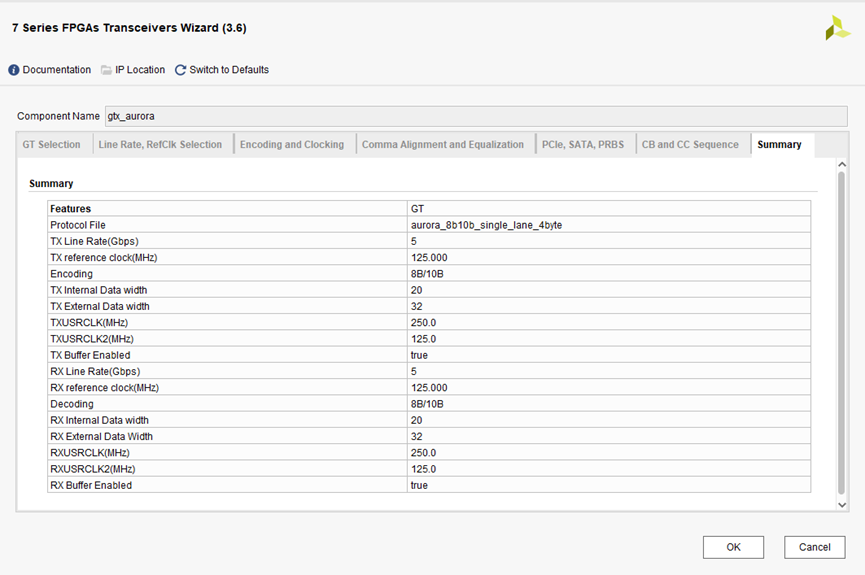

Summary

根据上图可以看出,TXUSRCLK和RXUSRCLK频率为250M,TXUSRCLK2和 RXUSRCLK2为125M,也就是我们写代码要使用的时钟。

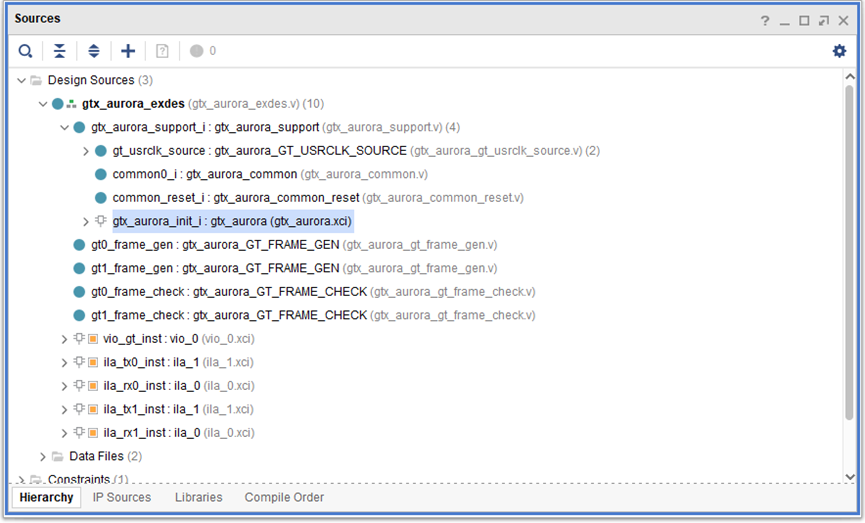

Vivado工程创建

右击IP核,选择 open IP example design;

其中,gt aurora GT FRAME GEN模块功能是产生要发送的测试数据,gt aurora GT FRAME CHECK模块检查回环收到的数据是否正确;

由于开发板的SFP屏蔽笼的tx_disable引脚都默认接了上拉电阻。要使收发回环测试可以正常进行,必须要将tx_disable引脚拉低。因此,在example design的顶层模块,添加2个sfp_tx_disable引脚,且均置为0即可;

将drp_clk直接连入sysclk,官方例程这个时钟是引脚进来的加了bufg,该工程用PLL产生;

接下来我们将在硬件上实现回环传输测试数据的功能,首先我们需要从外部给出一个自由时钟,hb_gtwiz_reset_all_in复信号是高电平有效,用户直接拉低即可。由于开发板的SFP屏蔽笼的tx_disable引脚都默认接了上拉电阻。要使收发回环测试可以正常进行,必须要将tx_disable引脚拉低;

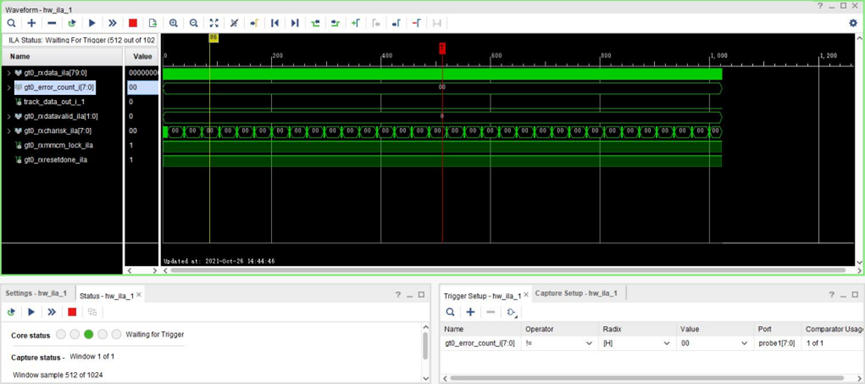

最后在示例工程里添加必要的ILA,去抓取对应的信号。

功能测试

本工程实现功能为光纤信号8b10b回环传输,FPGA板上测试结果如下图所示,可以看到gt0_error_count_i信号保持为0,也就是说8b10b光通信传输正常。

-

FPGA

+关注

关注

1664文章

22502浏览量

639189 -

Xilinx

+关注

关注

73文章

2206浏览量

131884 -

串行通信

+关注

关注

4文章

609浏览量

37224 -

光通信

+关注

关注

20文章

1033浏览量

35453 -

Vivado

+关注

关注

19文章

860浏览量

71396

发布评论请先 登录

把握光通信行业演变脉动 CIOE2012光通信展即将起航!

Aurora 8b/10b IP核问题

FPGA在光通信中的应用

Aurora IP 8b10b如何生成bitfile?

用于26Km光缆的Aurora IP v11.0通道上行/上行故障的解决办法?

如何使用Aurora 8B / 10B建立仅传输?

怎么禁用Aurora IP Core 8B / 10B中的时钟补偿功能?

如何在KC705-kintex 7中实现极光8b10b?

可见光通信原理及硬件方案 精选资料分享

可见光通信 调制解调技术 家庭机器人 可见光通信应用 原理及硬件方案 精选资料分享

基于Virtex-6 的Aurora 8B/10B,PCIe2.0,SRIO 2.0三种串行通信协议分析

泰克携最新光通信测试技术解决方案亮相ECOC 2018展

基于FPGA的UDP万兆光通信测试

基于FPGA的Aurora 8b10b光通信测试方案

基于FPGA的Aurora 8b10b光通信测试方案

评论