性能浮点处理一直与高性能CPU相关联。在过去几年中,GPU也成为功能强大的浮点处理平台,超越了图形,称为GP-GPU(通用图形处理单元)。

2015-07-31 09:45:20 2122

2122

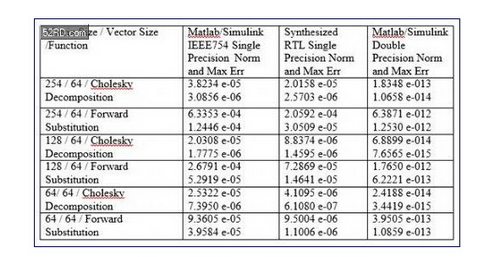

高性能浮点处理一直与高性能CPU相关联。在过去几年中,GPU也成为功能强大的浮点处理平台,超越了图形,称为GP-GPU(通用图形处理单元)。新创新是在苛刻的应用中实现基于FPGA的浮点处理。本文

2018-01-16 08:53:11 6710

6710

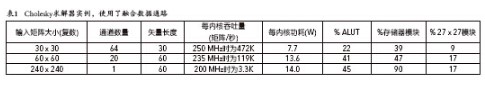

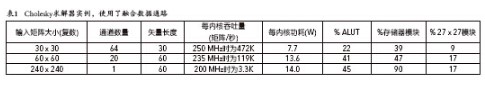

卷积是一种线性运算,其本质是滑动平均思想,广泛应用于图像滤波。而随着人工智能及深度学习的发展,卷积也在神经网络中发挥重要的作用,如卷积神经网络。本参考设计主要介绍如何基于INTEL 硬浮点的DSP

2018-07-23 09:09:45 8401

8401

大部分运算可以通过扩位和近似的方式转换为定点运算。但有些算法在设计在设计的过程中就涉及大量的浮点运算,在转换为定点运算时比较麻烦,会带来庞大的工作量。

2022-09-08 15:41:56 3509

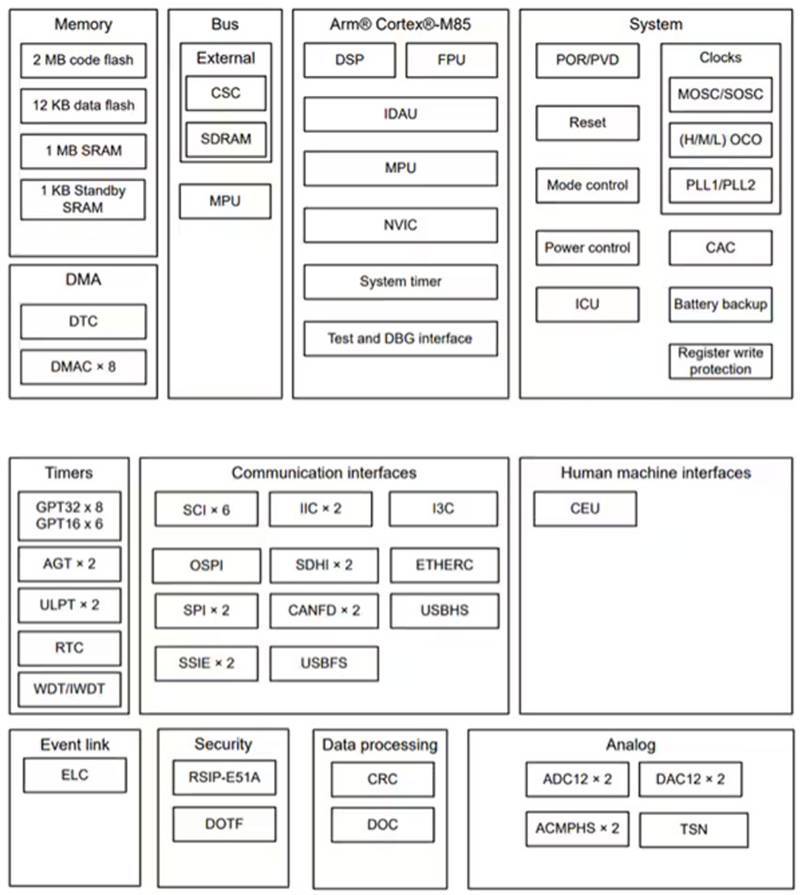

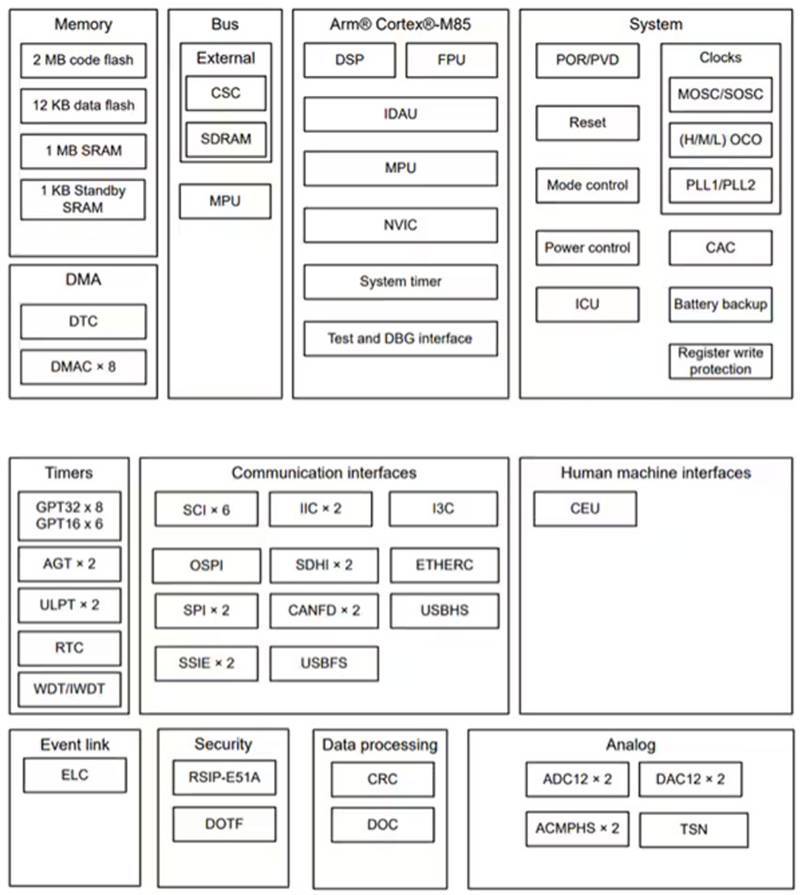

3509 众所皆知,MCU运算力有限(相对于IoT网关、手机、计算机),而AI/ML向来耗用运算力,如此TinyML的技术主张岂不矛盾?事实上,MCU的运算力也非如刻板印象中那样一直不堪,MCU运算力也在提升,如此可用来执行简单(相对于云端机房、边缘运算)的AI/ML推论工作。

2022-09-20 11:10:55 2862

2862 作者:Kenton Williston 人工智能 (AI)、机器学习 (ML) 和其他计算密集型工作负载在物联网 (IoT) 网络边缘的兴起,给微控制器 (MCU) 带来了额外的处理负载。处理这些

2024-04-23 15:04:36 2307

2307

全新Balletto™系列无线MCU基于Alif Semiconductor先进的MCU架构,该架构具有DSP加速和专用NPU,可快速且低功耗地执行AI/ML工作负载 中国,北京 -2024 年

2024-04-18 17:51:54 1161

1161

装置」与「感测装置」成为不可或缺的一环。在AI模块中,处理芯片与储存系统之间的信道优化,将直接影响系统在实时判断与深度学习的效能,因此内存模块必须更重视客制化与稳定性等需求。目前就AI产业面观察,尤其

2017-12-05 08:09:38

%数据中心的工作量。平方GPU对培训工作量有效,但在人工智能的所有不同阶段都不需要GPU。在2021年的一项研究中,56%的研究受访者将成本列为他们面临的最重大挑战实施AI/ML解决方案。

2023-08-04 07:25:00

FPGA 如何进行浮点运算

2015-09-26 09:31:37

最近出现的 FPGA设计工具和 IP有效减少了计算占用的资源,大大简化了浮点数据通路的实现。而且,与数字信号处理器不同, FPGA能够支持浮点和定点混合工作的 DSP数据通路,实现的性能超过

2019-08-13 06:42:48

。利用FPGA,可以将多个设计功能集成到一个器件中。这种功能性的集成也可以提高性能、减小面积和功耗。信号处理实现的另一个潜在的优点是,FPGA中包含一些预先验证过的信号处理算法单元。这些IP核或者块可以

2021-12-15 06:30:00

在定点DSP系统中可否实现浮点运算?当然可以,因为DSP都可以用C,只要是可以使用c语言的场合都可以实现浮点运算。

2009-04-07 09:06:17

的,和整数长度一致。

2.浮点运算指令实现:蜂鸟E203可以通过在EXU内添加一个与ALU平行的模块:浮点处理单元(float point unit),专用于处理浮点指令。该单元可以更高效地执行浮点数计算

2025-10-22 07:04:49

一些特殊处理。

浮点数开平方运算可以表达为以下公式:

这里的符号位是逻辑零,这意味着平方根块总是期望正浮点数。平方根运算只在尾数部分进行,这可以通过任意一种平方根算法来实现。指数部分除以2,也就是右移

2025-10-24 08:42:22

语言编写的浮点矩阵相乘处理单元[1],其关键技术是乘累加单元的设计,这样设计的硬件,其性能依赖于设计者的编程水平。此外,FPGA厂商也推出了一定规模的浮点矩阵运算IP核[2],虽然此IP核应用了本厂家的器件,并经过专业调试和硬件实测,性能稳定且优于手写代码,但仍可对其进行改进,以进一步提高运算速度。

2019-08-22 06:41:38

的 ML 工作负载。MLCommons 是一个开放的工程联盟,通过基准、指标、数据集和最佳实践来支持和改进机器学习行业。在此分析中,我们为两个广泛使用的 ML 用例(图像分类和语言处理)运行了基准模型

2022-08-31 15:03:46

4 个时钟后连续输出运算结果。各个单元协调一致的并行工作, 提高了系统时钟频率, 达到了高速处理。采用块浮点机制, 动态扩大数据范围, 在速度和精度之间得到折衷。模块化设计, 易于实现更多

2017-11-21 15:55:13

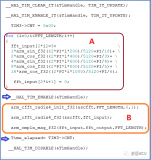

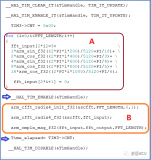

在添加浮点运算单元时,可以引用开源的浮点运算器以简化所需工作任务压力。在此我们采用了FPnew这个开源工程,再次介绍一些如何将其导成vivado工程。

首先在github上下载fpnew工程文件

2025-10-24 11:08:41

void SystemInit(void){/* FPU settings 浮点运算单元设置,此处一般不执行

2021-08-23 06:20:51

NUC980有浮点运算单元吗?另外采用外部的SPI NOR FLASH是不是不能加密呀!

2022-10-24 14:17:27

TMS320F28335浮点单元,进行浮点运算时会自动选择Q15,Q22等格式,自动进行精度和范围的匹配吗?

2013-04-06 18:33:52

我想知道 X-CUBE-AI 和 NanoEdge AI Studio 在 ML 和 AI 开发环境中的区别。我可以在任何一个开发环境中做同样的事情吗?使用的设备有什么限制吗?

2022-12-05 06:03:15

RISC-V浮点运算单元(floating-point unit,简称FPU)是一种专门用于执行浮点运算的硬件加速器,其作用是提高浮点运算速度,在科学计算、图像处理和机器学习等应用领域有着广泛

2025-10-21 14:46:51

今天测试一下EdgeBoard的浮点运算能力(在Linux下),测试的程序比较容易,运行基2 FFT算法,折合成 百万次浮点运算/每秒 的运算速度来衡量。 运行程序,结果如下: 下面是各类处理

2021-04-29 12:12:20

现代信号处理技术通常都需要进行大量高速浮点运算。由于浮点数系统操作比较复杂,需要专用硬件来完成相关的操作(在浮点运算中的浮点加法运算几乎占到全部运算操作的一半以上),所以,浮点加法器是现代信号

2019-07-05 06:21:42

单元。

Unpack和Pack模块块将浮点类型转换为符号、指数和尾数。图中S、E、M分别代表符号、指数、尾数。这是基于IEEE-754浮点运算标准。浮点算法实现块在S、E和m上执行计算。通过这种转换

2025-10-22 06:48:48

乘法简单得多,在FPGA中占用的资源也比乘法器少得多,因而能够在1块50万门左右的FPGA中实现32个运算单元或者更多的运算单元。为了使窗口值T取128时计算的结果不会溢出,运算器选取了26位位宽

2009-09-19 09:25:42

和IFFT运算。在FPGA设计中,利用结构复用减少逻辑单元块,不仅可以节约系统资源,而且能够减少结构间 的硬连线及传输线时延,有利于提高系统的工作频率。 2.2.2 脉冲压缩模块的时序设计 由于FFT

2018-11-09 15:53:22

现代信号处理技术通常都需要进行大量高速浮点运算。由于浮点数系统操作比较复杂,需要专用硬件来完成相关的操作(在浮点运算中的浮点加法运算几乎占到全部运算操作的一半以上),所以,浮点加法器是现代信号

2019-08-15 08:00:45

高性能浮点处理一直与高性能CPU相关联。在过去几年中,GPU也成为功能强大的浮点处理平台,超越了图形,称为GP-GPU(通用图形处理单元)。新创新是在苛刻的应用中实现基于FPGA的浮点处理。

2019-10-21 08:15:23

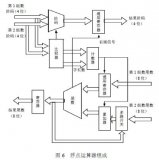

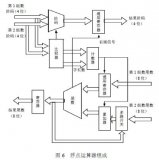

FFT算法的实现为了提高FFT工作频率和节省FPGA资源,采用3级流水线结构实现64点的FFT运算。流水线处理器的结构如图2所示。每级均由延时单元、转接器(SW)、蝶形运算和旋转因子乘法4个模块组成

2019-06-17 09:01:35

在AI时代,FPGA(现场可编程门阵列)具有极其重要的地位,主要体现在以下几个方面:

1.硬件加速与高效能

• 并行处理能力:FPGA内部由大量可编程逻辑单元组成,能够实现高度并行的数据处理。这种

2025-02-19 13:55:47

STM32开发板ISP下载的原理是什么?STM32F4的浮点运算单元是由哪些部分组成的?怎样去计算STM32F4的浮点运算单元呢?

2021-10-22 09:13:17

扩充浮点运算集的时候,是否需要自己在FPGA板子上设置一个定点数转为浮点数的部分?

2023-08-11 09:13:34

本帖最后由 一只耳朵怪 于 2018-5-25 17:11 编辑

怎么样使用TMS570LC4357片上浮点运算单元(FPU)?怎么充分利用浮点运算单元呢?

2018-05-25 02:22:48

。 Achronix为了解决这一大困境,创新地设计了机器学习处理器(MLP)单元,不仅支持浮点的乘加运算,还可以支持对多种定浮点数格式进行拆分。

2020-11-26 06:42:00

介绍一种在FPGA上实现的单精度浮点加法运算器,运算器算法的实现考虑了FPGA器件本身的特点,算法处理流程的拆分和模块的拆分,便于流水设计的实现。

2021-04-29 06:27:09

有助于使成本和功耗降至最低,而且还能尽可能地加速硬件部署。FPGA 非常适用于执行定点运算,并能在逻辑或基于软件或硬件处理器的实施方案中创建高度并行的数据路径解决方案。Virtex®-5 FPGA 产品

2018-08-03 11:15:23

可配置性,具有多种选项以提高性能和安全性。矢量单元支持每个周期用于 DSP 应用的两个 32 位 MAC 运算,扩展的算术支持包括用于 ML 工作负载的 8 位定点。Cortex-M55 处理器汇集

2022-08-12 16:11:32

你好,我现在用得是LCDK6748,因为LCDK6748既可以执行定点运算也可以执行浮点运算,我已经知道如果我想只进行定点运算,可以在-mv编译选项选择6400+,如果我只想进行浮点运算可以在-mv

2018-08-02 08:54:38

请问esp32 wroom 32u 默认开启硬件浮点运算单元了吗?感谢

2024-06-21 11:08:25

我们的蓝牙芯片有浮点运算单元吗

2022-10-09 07:52:55

浮点运算方法:

2008-01-16 09:22:37 29

29

介绍了用VHDL 语言在硬件芯片上实现浮点加/ 减法、浮点乘法运算的方法,并以Altera

公司的FLEX10K系列产品为硬件平台,以Maxplus II 为软件工具,实现了6 点实序列浮点加/ 减法

2009-07-28 14:06:13 85

85 浮点运算与浮点运算器

浮点加减法的运算步骤 设两个浮点数 X=Mx※2Ex Y=My※2Ey 实现X±Y要用如下5步完成: ①对阶操作:小阶

2010-04-15 13:42:32 7293

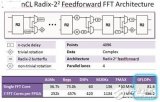

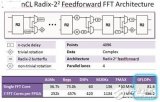

7293 提出一种基2FFT的FPGA方法,完成了基于FPGA高精度浮点运算器的FFT的设计。利用VHDL语言描述了蝶形运算过程及地址产生单元,其仿真波形基本能正确的表示输出结果。

2011-12-23 14:24:08 46

46 i7处理器的 PC机的浮点运算性能提高1.7倍,功耗仅仅增加10%左右。Rutten写道: “根据测试软件,一个典型的i7 PC平台的浮点数运算性能大约是每秒75GFLOPS。通过给PC机增加一个基于FPGA的SOM,利

2017-02-09 06:15:08 1645

1645 Float Point Unit,浮点运算单元是专用于浮点运算的协处理器,在计算领域,例如三角函数以及时域频域变换通常会用到浮点运算。

2017-09-16 11:28:47 6

6 上提供了一组协处理器指令专门实现浮点运算。但这需要硬件支持,具体某一处理器上是否有FPA协处理器支持,可以查看ARM相关手册。 浮点运算仿真(FPE):使用软件仿真了FPA协处理器的执行。 浮点运算库(FPLib):使用ARM的浮点运算库函数实现程序中的浮点运算操作。这就意味着C编译器要把每一个

2017-10-17 16:48:39 1

1 浮点算法不遵循整数算法规则,但利用 FPGA 或者基于 FPGA 的嵌入式处理器不难设计出精确的浮点系统。工程人员一看到浮点运算就会头疼,因为浮点运算用软件实现速度慢,用硬件实现则占用资源多。理解

2017-11-22 16:51:08 2072

2072 器作为计算机的加工处理部件,是CPU(中央处理器)的重要组成部分。作为典型的PC机一般都至少具有一个定点运算器。在586 之前的机型中,由于当时硬件条件和工艺的限制,浮点运算器一般以协处理器的形式出现

2018-07-14 09:50:00 3906

3906

一. 前言 有工程师反应说Keil 下无法使用STM32F4xx 硬件浮点单元, 导致当运算浮点时运算时间过长,还有一些人反应不知如何使用芯片芯片内部的复杂数学运算,比如三角函数运算。针对这个部分

2017-11-29 15:57:01 1750

1750

一. 前言 有工程师反应说Keil 下无法使用STM32F4xx 硬件浮点单元, 导致当运算浮点时运算时间过长,还有一些人反应不知如何使用芯片芯片内部的复杂数学运算,比如三角函数运算。针对这个部分

2017-11-29 17:48:46 1170

1170

高性能浮点处理一直与高性能CPU相关联。在过去几年中,GPU也成为功能强大的浮点处理平台,超越了图形,称为GP-GPU(通用图形处理单 元)。新创新是在苛刻的应用中实现基于FPGA的浮点处理。本文

2017-12-04 16:29:05 1016

1016

异常会造成程序错误,实现完全没有异常的浮点计算软件也很艰难,因此,实现有效的异常处理方法很重要.但现有的异常处理并不针对浮点运算,并且研究重点都集中在整数溢出错误上,而浮点类型运算降低了整数溢出存在

2018-01-19 15:50:14 1

1 工智能(AI)/机器学习、5G移动通信、汽车先进驾驶员辅助系统(ADAS)、数据中心和网络应用; Speedcore custom blocks定制单元块可以大幅度地提升性能、功耗和面积效率,并支持以前在FPGA独立芯片上无法实现的功能。

2018-01-22 16:42:01 1116

1116 各种处理平台的GFLOP指标在不断提高,现在,TFLOP/s这一术语已经使用的非常广泛了。但是,在某些平台上,峰值GFLOP/s,即,TFLOP/s表示的器件性能信息有限。它只表示了每秒能够完成的理论浮点加法或者乘法总数。分析表明,FPGA单精度浮点处理能够超过1 TFLOP/s。

2018-02-19 03:53:00 5141

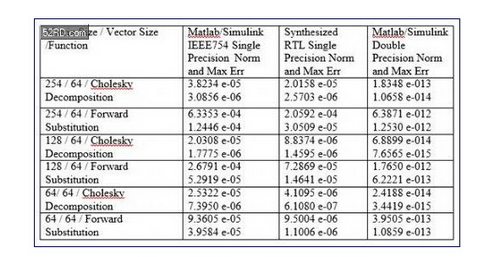

5141 2014年4月23号,北京Altera公司 (Nasdaq: ALTR) 今天宣布在FPGA浮点DSP性能方面实现了变革。Altera是第一家在FPGA中集成硬核IEEE 754兼容浮点运算功能

2018-02-11 13:34:00 7749

7749 在载人航天飞船的终端仪器仪表设计中,处理算法中的浮点非线性运算常采用库函数实现,但软件实现非线性函数执行速度慢,限制了浮点算法的应用。为此,针对航天领域处理器不支持非线性函数运算的情况以及浮点

2018-02-26 14:58:34 0

0 浮点加法是数字信号处理中的一种非常频繁且非常重要的操作,在现代数字信号处理应用中,浮点加法运算几乎占到全部浮点操作的一半以上。浮点乘法器是高性能DSP(数字信号处理器)的重要部件,是实时处理的核心

2018-04-10 10:47:21 8

8 结构复杂,采用DSP实现会增加系统负担,降低系统速度。在某些对速度要求较高的情况,必须采用专门的浮点运算处理器。 EDA/FPGA技术不断发展,其高速、应用灵活、低成本的优点使其广泛应用数字信号处理领域。在FPCA技术应用的初期,

2018-04-10 14:25:53 17

17 以往FPGA在进行浮点运算时,为符合IEEE 754标准,每次运算都需要去归一化和归一化步骤,导致了极大的性能瓶颈。因为这些归一化和去归一化步骤一般通过FPGA中的大规模桶形移位寄存器实现,需要大量

2020-01-14 16:19:55 4101

4101

高性能浮点处理一直与高性能 CPU 相关联。在过去几年中,GPU 也成为功能强大的浮点处理平台,超越了图形,称为 GPGPU(通用图形处理单元)。新创新是在苛刻的应用中实现基于 FPGA 的浮点处理

2020-12-22 13:33:00 14

14 有人利用STM32芯片做些DSP处理,在启用FPU单元进行调试、验证过程中可能会遇到些小问题、小困惑,这里通过STM32F4芯片一个具体的应用示例简单分享下,希望顺便能给同仁提供些帮助或提醒。 我

2021-01-02 18:09:00 9859

9859

单元;一片为因子的生成单元;一片为$DRAM控制单元;一片为系统的控制单元.该系统将流水处理和并行处理相结合,从而极大的减少了处理时间.同时根据算法各运算对数据的精度要求不同,将浮点运算和定点运算结合在一块,减少了硬件开销.该系统工作在100MHz时,

2021-02-05 15:22:46 14

14 该问题由某客户提出,发生在 STM32F407IGT6 器件上。据其工程师讲述:由于在其产品中,需要使用STM32进行大量的浮点数以及浮点DSP运算,所以针对STM32的浮点数运算能力及 DSP

2021-04-28 15:17:02 10

10 的,一种解决办法就是采用定标。 数的定标就是将要运算的浮点数扩大很多倍,然后取整,再用这个数进行运算,运算得到的结果再缩小相应的倍数就可以了。在设计中,一定不要忘记小数点。在FPGA 中是体现不出来小数点的,小数点的位置只有程序员知道。

2021-08-12 09:53:39 5486

5486 编者按:在计算领域,例如三角函数以及时域频域变换通常会用到浮点运算。当CPU执行一个需要浮点数运算的程序时,有三种方式可以执行:软件仿真器(浮点运算函数库)、附加浮点运算器和集成浮点运算单元。在控制

2021-12-04 13:36:05 19

19 使用插值算法实现图像缩放是数字图像处理算法中经常遇到的问题。我们经常会将某种尺寸的图像转换为其他尺寸的图像,如放大或者缩小图像。由于在缩放的过程中会遇到浮点数,如何在FPGA中正确的处理浮点数运算是在FPGA中实现图像缩放的关键。

2022-03-18 11:03:41 5929

5929 (人工智能)和ML(机器学习)的日益普及开辟了一个充满可能性的新世界,PC厂商和生态系统巨头都在寻求将这些先进的新功能添加到其产品功能集中。 在本篇博文中,莱迪思将讨论PC中AI/ML功能的增长趋势,为什么FPGA非常适合实现这些新

2022-09-08 17:19:25 1688

1688 FPGA在常规运算时不能进行浮点运算,只能进行定点整型运算,在处理数据的小数乘加运算和除法运算时FPGA一般是无能为力的,其中一种常用的处理方法就是数据进行浮点到定点的转换。

2022-10-13 16:23:50 6173

6173 我们使用的处理器一般情况下,要么直接支持硬件的 浮点运算 ,比如某些带有FPU的器件,要么就只支持定点运算,此时对 浮点 数的处理需要通过编译器来完成。在支持硬件浮点处理的器件上,对 浮点运算

2022-12-09 12:25:09 3815

3815 在 FPGA 上实施 AI/ML 的选项

2022-12-28 09:51:08 1424

1424 图像处理的算法中,大部分需要采用 浮点数 运算,而浮点数运算再FPGA中是非常不划算的,因此需要转换成定点数计算,此时会设计到浮点运算转定点运算时精度下降的问题。 3.软件和硬件的合理划分 这里的软件是指DSP,CPU,硬件是指FPGA;一般 结构规则

2023-02-15 16:35:08 2004

2004 图像处理的算法中,大部分需要采用浮点数运算,而浮点数运算再FPGA中是非常不划算的,因此需要转换成定点数计算,此时会设计到浮点运算转定点运算时精度下降的问题。

2023-02-17 09:16:15 3351

3351 MLP全称Machine Learning Processing单元,是由一组至多32个乘法器的阵列,以及一个加法树、累加器、还有四舍五入rounding/饱和saturation/归一化normalize功能块。

2023-02-27 10:45:30 600

600 。Achronix为了解决这一大困境,创新地设计了机器学习处理器(MLP)单元,不仅支持浮点的乘加运算,还可以支持对多种定浮点数格式进行拆分。 MLP全称Machine Learning Processing单元

2023-03-11 13:05:07 1285

1285 处理的算法中,大部分需要采用浮点数运算,而浮点数运算再FPGA中是非常不划算的,因此需要转换成定点数计算,此时会设计到浮点运算转定点运算时精度下降的问题。 3.软件和硬件的合理划分这里的软件是指DSP,CPU,硬件是指FPGA;一般 结构规则

2023-03-21 19:40:02 1195

1195 点击上方 蓝字 关注我们 高性能浮点处理一直与高性能 CPU 相关联。在过去几年中,GPU也成为功能强大的浮点处理平台,超越了图形,称为GP-GPU(通用图形处理单元)。新创新是在苛刻的应用中实现

2023-06-10 10:15:01 1350

1350

虹科方案1AI&ML变革日常生活AI(人工智能)和ML(机器学习)的发展正逐渐渗透到我们的日常生活中,为我们带来了翻天覆地的变化。从智能手机中的语音助手到智能家居设备,AI的应用让我们的生活

2023-08-05 08:11:03 1181

1181

点击上方 蓝字 关注我们 现代信号处理技术通常都需要进行大量高速浮点运算。由于浮点数系统操作比较复杂,需要专用硬件来完成相关的操作(在浮点运算中的浮点加法运算几乎占到全部运算操作的一半以上),所以

2023-09-22 10:40:03 2116

2116

运算的运算步骤远比定点运算繁琐,运算速度慢且所需硬件资源大大增加,因此基于浮点运算的LMS算法的硬件实现一直以来是学者们研究的难点和热点。 本文正是基于这种高效结构的多输入FPA,在FPGA上成功实现了基于浮点运算的LMS算法。测试

2023-12-21 16:40:01 1590

1590 支持硬件浮点运算单元(FPU),可以提供快速和高效的浮点运算性能。本文将详细介绍 STM32F407 的浮点运算速度。 浮点运算是很多应用中常用的一种运算类型,特别是对于需要进行较复杂计算的任务,如图像处理、信号处理和物理模拟等。传统的处理器对于浮点运算的支持有限,需要通过软件库实现

2024-01-04 10:58:34 5181

5181 由于定点的四则运算比较简单,如加减法只要注意符号扩展,小数点对齐等问题即可。在本文中,运用在前一节中描述的自定义浮点格式FPGA中数的表示方法(下),完成浮点四则运算的实现过程 1.自定义浮点格式加

2024-11-16 11:19:23 2139

2139

由于定点的四则运算比较简单,如加减法只要注意符号扩展,小数点对齐等问题即可。在本文中,运用在前一节中描述的自定义浮点格式FPGA中数的表示方法(下),完成浮点四则运算的实现过程 1.自定义浮点格式加

2024-11-16 12:51:57 1323

1323

提供了强有力的支持。 一、FPGA 在深度学习中的应用 深度学习是 AI 的重要分支,涉及海量的数据运算。FPGA 能够针对深度学习算法中的卷积、池化等核心运算进行硬件加速优化。例如,在图像识别任务中,将卷积神经网络部署到 FPGA 上,通过并行处理

2025-01-06 17:37:10 2318

2318

电子发烧友App

电子发烧友App

评论