我们使用的处理器一般情况下,要么直接支持硬件的浮点运算,比如某些带有FPU的器件,要么就只支持定点运算,此时对浮点数的处理需要通过编译器来完成。在支持硬件浮点处理的器件上,对浮点运算的编程最快捷的方法就是直接使用浮点类型,比如单精度的float来完成。但是在很多情况下,限于成本、物料等因素,可供我们使用的只有一个定点处理器时,直接使用float类型进行浮点类型的运算会使得编译器产生大量的代码来完成一段看起来十分简单的浮点数学运算,造成的后果是程序的执行时间显著加长,且其占用的资源量也会成倍地增加,这就涉及到了如何在定点处理器上对浮点运算进行高效处理的问题。

既然是定点处理器,那么其对定点数,或者说字面意义上的“整数”进行处理的效率就会比它处理浮点类型的运算要高的多。所以在定点处理器上,我们使用定点的整数来代表一个浮点数,并规定整数位数和小数位数,从而方便地对定点数和浮点数进行转换。以一个32位的定点数为例,假设转换因子为Q,即32位中小数的位数为Q,整数位数则为31-Q(有符号数的情况),则定点数与浮点数的换算关系为:

定点数=浮点数×2^Q

例如,浮点数-2.0转换到Q为30的定点数时,结果为:

定点数=-2×2^30=-2147483648

32位有符号数的表示范围是:-2147483648到2147483647。如果我们把有符号定点数的最大值2147483647转换为Q为30对应的浮点数,则结果为:

浮点数2147483647/2^30=1.999999999

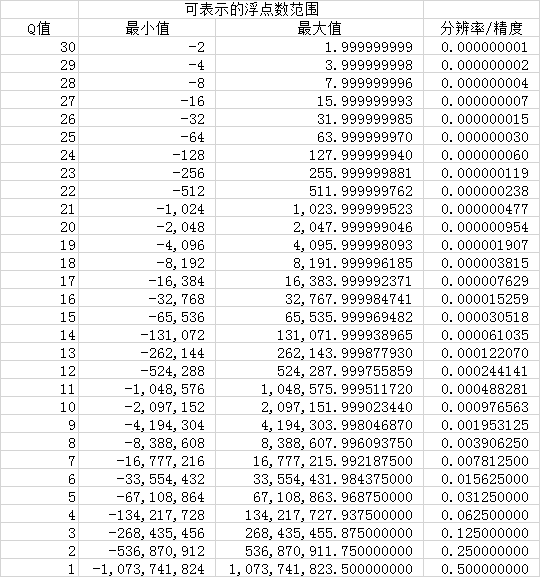

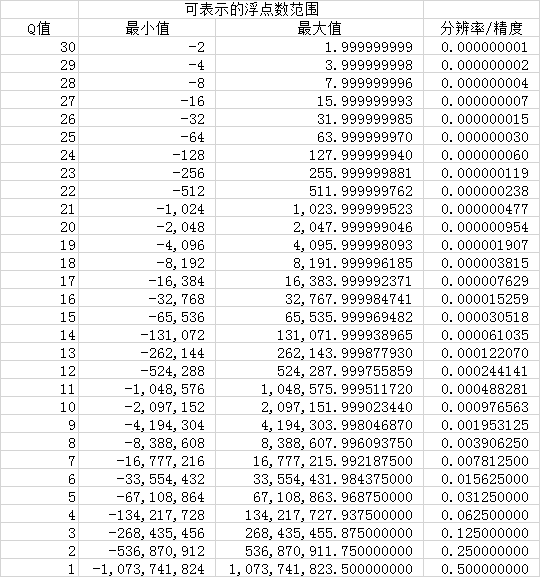

从上面的两个计算例子中也可以看出,在Q30格式的情况下,最大的浮点数只能表示到1.999999999,如果我们想把浮点数2.0转换为Q30的定点数,则产生了溢出,即造成了1e-9的截断误差。在此我们列出Q0到Q30对应的范围和分辨率如下表所:

如果你嫌自己计算麻烦的话,可以借助Matlab的命令来求取它们的转换,例如,在Matlab的命令窗口中输入:

q = quantizer('fixed', 'ceil', 'saturate', [32 30]);

FixedNum=bin2dec(num2bin(q,1.999999999));

回车之后就可以看到1.999999999转成Q30之后的定点数了。

弄清楚了单个浮点数和定点数之间的转换关系,接下来就需要了解一下两个定点数所代表的浮点数进行运算时,是如何转换的了。根据乘法的结合律、分配率,浮点数转换之后的定点数是可以直接运算的,例如:

1. 不同Q格式的转换

设有定点数Fixed1=Float1*2^Q1,如果把它用为Q2这个不同精度/表示范围的定点数来表示,则有Fixed2=Float1*2^Q2。所以不同的Q格式直接的转换为:

Fixed2=Fixed1*2^Q2/2^Q1=Fixed1*2^(Q2-Q1)

因为Fixed1、Fixed2都是定点数,所以在C编程的情况下,我们可以使用高效的左移、右移操作来完成这个乘以2^(Q2-Q1)的操作。

2. 两个相同Q格式的定点数:

Fixed1=Float1*2^Q

Fixed2=Float2*2^Q

则加法操作为:

Float1+Float2=Fixed1/2^Q+Fixed/2^Q=(Fixed1+Fixed2)/2^Q

对于上述的加法操作,如果定点数的和Fixed1+Fixed2超过了32位整数的极值,则会发生溢出现象,造成结果的不正确,此时我们只能先损失一倍的精度,把Float1、Float2的Q值变为Q-1.

乘法操作为:

Float1*Float2=Fixed1/2^Q*Fixed/2^Q= Fixed1*Fixed2/2^(2Q)

同样的道理,如果Fixed1*Fixed2之后的定点数超过了32位整数的极值,则我们也需要提前对它们进行一下折算,变换一下它们的Q值。这就涉及到对结果的一个预估问题,也是定点编程不如浮点编程简单、高效的不足之一。

3. 两个不同Q格式的定点数:

Fixed1=Float1*2^Q1

Fixed2=Float2*2^Q2

运算的规则是结合了前面的两种情况,只不过多了额外的转换工作:要么把其中的一个Q1格式的定点数先转换为另一个Q2格式,要么把它们都转换为一个中间值Q3格式的定点数,然后再进行运算。

这些运算虽然并不复杂,但是如果在数学运算比较多的情况下,一个个的进行手工转换还是比较麻烦的,还好在近些年的处理器特别是DSP芯片中,在其BootROM中都内置了强大的数学表来帮助我们完成这些转换工作,我们只要按照一定的格式进行书写,那么编译器就会自动调用相关的库函数来完成了。以TI的C28x系列DSP为例,我们可以使用现成的IQMath库来完成这些繁琐的工作。它的使用方法示例为

1)在工程属性中引用IQmath.lib库文件

2)在使用IQMath库函数的主程序中引用相关的头文件:

#include

#define PI 3.14159

_iq input, sin_out;

void main(void )

{

/* 0.25 x PI radians represented in Q29 format*/

input=_IQ29(0.25*PI);

sin_out =_IQ29sin(input);

}

其中,我们可以在头文件中指定一个全局的Q格式,在不需要特别指定Q值的时候,使用默认的值。

例如,在头文件中#define Q 28,则我们在程序中调用IQMath库函数时,

sin_out =_IQsin(input);//使用全局定义的Q28格式

sin_out =_IQ29sin(input); //特别指定使用Q29格式

默认情况下,编译器使用的Q格式是24,如果追求更高的精度,则可以使用更大的Q值,但是相应地表示的浮点数的范围也要小,此时可以考虑使用标么值,使得大部分变量的值都处在-1到1的区间内。

此外,在C语言编程时,调用方式是_IQsin(input),在C++编程时,则直接使用IQsin(input)就可以了。

3)在CMD链接文件中指明IQMath数学表的位置:

例如,对于281x器件:

MEMORY

{

PAGE 0:

PRAMH0 (RW) : origin = 0x3f8000, length = 0x001000

PAGE 1:

IQTABLES (R) : origin = 0x3FF000, length = 0x000b50

DRAMH0 (RW) : origin = 0x3f9000, length = 0x001000

}

SECTIONS

{

IQmathTables : load = IQTABLES, type = NOLOAD, PAGE = 1

IQmathTablesRam : load = DRAMH0, PAGE = 1

IQmath : load = PRAMH0, PAGE = 0

}

对于2833x器件:

MEMORY

{

PAGE 0:

PRAML0 (RW) : origin = 0x008000, length = 0x001000

PAGE 1:

IQTABLES (R) : origin = 0x3FE000, length = 0x000b50

IQTABLES2 (R) : origin = 0x3FEB50, length = 0x00008c

DRAML1 (RW) : origin = 0x009000, length = 0x001000

}

SECTIONS

{

IQmathTables : load = IQTABLES, type = NOLOAD, PAGE = 1

IQmathTables2 > IQTABLES2, type = NOLOAD, PAGE = 1

{

IQmath.lib (IQmathTablesRam)

}

IQmathTablesRam : load = DRAML1, PAGE = 1

IQmath : load = PRAML0, PAGE = 0

}

对于280x器件:

MEMORY

{

PAGE 0:

PRAML0 (RW) : origin = 0x008000, length = 0x001000

PAGE 1:

IQTABLES (R) : origin = 0x3FE000, length = 0x000b50

IQTABLES2 (R) : origin = 0x3FEB50, length = 0x00008c

IQTABLES3 (R) : origin = 0x3FEBDC, length = 0x0000AA

DRAML1 (RW) : origin = 0x009000, length = 0x001000

}

SECTIONS

{

IQmathTables : load = IQTABLES, type = NOLOAD, PAGE = 1

IQmathTables2 > IQTABLES2, type = NOLOAD, PAGE = 1

{

IQmath.lib (IQmathTablesRam)

}

IQmathTables3 > IQTABLES3, type = NOLOAD, PAGE = 1

{

IQmath.lib (IQmathTablesRam)

}

IQmath : load = PRAML0, PAGE = 0

}

为了方便数学运算的高效处理,IQMath库中还包含了常用的数学运算函数,包括:

1. 格式转换

IQN浮点转定点,IQNtoF定点转浮点,atoIQN字符串转定点,IQNtoa定点转字符串,IQNint返回定点数的整数部分,IQNfrac返回定点数的小数部分,IQtoIQN和IQNtoIQ为指定Q格式与全局Q格式的互转,IQtoQN和QNtoIQ为32位与16位互转,IQmpy2, 4, 8..64即左移,IQdiv2, 4, 8..64即右移

2. 算数运算

IQNmpy和IQNrmpy:乘法,IQNrsmpy为带饱和的乘法。IQNmpyI32和IQNmpyI32int为定点数与32位整数的乘法,IQNmpyI32frac可返回结果的小数位数。QNmpyIQX:不同Q格式的定点数相乘。

IQNdiv:除法运算。

3. 三角运算

包括IQNasin,IQNsin,IQNsinPU,IQNacos,IQNcos,IQNcosPU,IQNatan2,IQNatan2PU,IQNatan。

其中,PU的含义在该函数中π已经折算为1。例如:

sin(0.25*π)=sinPU(0.25)。

4. 代数运算

包括IQNexp,IQNlog,IQNsqrt,IQNisqrt,IQNmag,IQNabs,IQsat

至芯科技12年不忘初心、再度起航12月17日北京中心FPGA工程师就业班开课、线上线下多维教学、欢迎咨询!

欢迎加入至芯科技FPGA微信学习交流群,这里有一群优秀的FPGA工程师、学生、老师、这里FPGA技术交流学习氛围浓厚、相互分享、相互帮助、叫上小伙伴一起加入吧!

详解浮点运算的定点编程

详解浮点运算的定点编程

评论