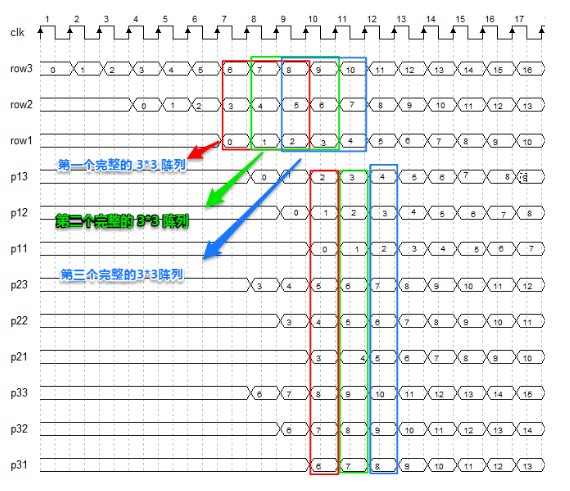

1 //矩阵元素移位赋值

2 always @(posedge clk or negedge rst_n)begin

3 if(rst_n==1'b0)begin

4 {p_11,p_12,p_13} <= {5'b0,5'b0,5'b0} ;

5 {p_21,p_22,p_23} <= {15'b0,15'b0,15'b0};

6 {p_31,p_32,p_33} <= {15'b0,15'b0,15'b0};

7 end

8 else begin

9 if(per_href_ff0==1&&flag_do==1)begin

10 {p_11,p_12,p_13}<={p_12,p_13,row_1};

11 {p_21,p_22,p_23}<={p_22,p_23,row_2};

12 {p_31,p_32,p_33}<={p_32,p_33,row_3};

13 end

14 else begin

15 {p_11,p_12,p_13}<={5'b0,5'b0,5'b0};

16 {p_21,p_22,p_23}<={5'b0,5'b0,5'b0}

17 {p_31,p_32,p_33}<={5'b0,5'b0,5'b0}

18 end

19 end

20 end

21

22

23 always @(posedge clk or negedge rst_n)begin

24 if(rst_n==1'b0)begin

25 mean_value_add1<=0;

26 mean_value_add2<=0;

27 mean_value_add3<=0;

28 end

29 else if(per_href_ff1)begin

30 mean_value_add1<=p_11+p_12+p_13;

31 mean_value_add2<=p_21+ 0 +p_23;

32 mean_value_add3<=p_31+p_32+p_33;

33 end

34 end

35

36 wire [8:0]mean_value;//8位数之和

37 wire [5:0]fin_y_data; //平均数,除以8,相当于左移三位。

38

39 assign mean_value=mean_value_add1+mean_value_add2+mean_value_add3;

40 assign fin_y_data=mean_value[8:3];

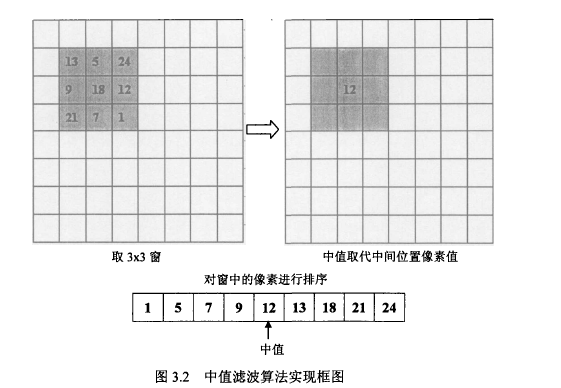

中值滤波

欢迎加入至芯科技FPGA微信学习交流群,这里有一群优秀的FPGA工程师、学生、老师、这里FPGA技术交流学习氛围浓厚、相互分享、相互帮助、叫上小伙伴一起加入吧!

点个在看你最好看

原文标题:FPGA学习-基于FPGA的图像处理

文章出处:【微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA

+关注

关注

1655文章

22283浏览量

630126

原文标题:FPGA学习-基于FPGA的图像处理

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

热点推荐

FPGA在机器学习中的具体应用

随着机器学习和人工智能技术的迅猛发展,传统的中央处理单元(CPU)和图形处理单元(GPU)已经无法满足高效处理大规模数据和复杂模型的需求。FPGA

【FPGA新品】正点原子L22开发板来了!采用紫光的Logos系列FPGA,适合工业控制、图像处理、高速通信等领域!

【FPGA新品】正点原子L22开发板来了!采用紫光的Logos系列FPGA,适合工业控制、图像处理、高速通信等领域!

ATK-L22开发板采用紫光的Logos系列

发表于 04-21 17:28

进群免费领FPGA学习资料!数字信号处理、傅里叶变换与FPGA开发等

进群免费领FPGA学习资料啦!小编整理了数字信号处理、傅里叶变换与FPGA开发等FPGA必看资料,需要的小伙伴可以加小助手(微信:elecf

发表于 04-07 16:41

【国产FPGA入学必备】国产FPGA权威设计指南+配套FPGA图像视频教程

缩短工程项目的开发周期,同时,本书可以帮助高校师生快速学习国产FPGA,为参加FPGA和集成电路竞赛提供有力的帮助。

二、紫光同创FPGA图像

发表于 02-20 15:08

【国产FPGA必备教程】——紫光同创FPGA图像视频教程,适用于小眼睛FPGA盘古全系列开发板

本帖最后由 jf_25420317 于 2025-2-19 18:15 编辑

小眼睛科技针对赛事推出配套视频教程,涵盖紫光同创工具的使用方法、基于紫光同创FPGA图像处理技巧、高速通信

发表于 02-19 15:44

基于FPGA的图像边缘检测设计

今天给大侠带来基于 FPGA 的图像边缘检测设计,话不多说,上货。 设计流程如下:mif文件的制作→ 调用 ip 核生成rom以及仿真注意问题→ 灰度处理→ 均值滤波:重点是3*3 像素阵列的生成

FPGA图像处理基础----实现缓存卷积窗口

像素行与像素窗口 一幅图像是由一个个像素点构成的,对于一幅480*272大小的图片来说,其宽度是480,高度是272。在使用FPGA进行图像处理时,最关键的就是使用

基于FPGA的GigE Vision相机图像采集方案设计

1 概述 GigE Vision是一个比较复杂的协议,要在FPGA中完全实现具有较大的难度。如果FPGA作为接收端希望实现GigE Vision相机的配置和图像采集功能,则只需要实现其中小部分功能

FPGA在AI方面有哪些应用

提供了强有力的支持。 一、FPGA 在深度学习中的应用 深度学习是 AI 的重要分支,涉及海量的数据运算。FPGA 能够针对深度学习算法中的

大多数FPGA的程序存储器(FLASH)为什么都放在外面呢?FPGA的主要应用

FPGA的主要应用: FPGA由于其较高的价格和成本,决定了FPGA不能像单片机那样被广泛的使用,FPGA的针对于高端处理市场(类如:手机

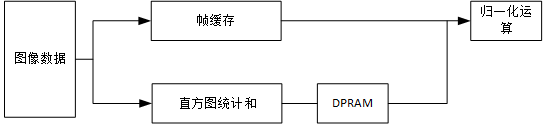

基于FPGA实现图像直方图设计

简单,单采用FPGA来实现直方图的统计就稍显麻烦。若使用Xilinx和Altera的FPGA芯片,可以使用HLS来进行图像的加速处理。但这暂时不是我的重点。 用C语言实现直方图统计:u

FPGA学习-基于FPGA的图像处理

FPGA学习-基于FPGA的图像处理

评论