这篇文章在开发者分享|AMD Vitis HLS 系列 1 - AMD Vivado IP 流程(Vitis 传统 IDE) 的基础上撰写,但使用的是 AMD Vitis Unified IDE,而不是之前传统版本的 Vitis HLS。

2025-06-20 10:06:15 2068

2068

Vivado IP 流程(Vitis Unified),在这篇 AMD Vitis HLS 系列 3 中,我们将介绍如何使用 Unified IDE 创建 HLS 组件。这里采用“自下而上”的流程,从 HLS

2025-07-02 10:55:32 1263

1263

在本篇文章我们将学习如何在 AMD Vitis Unified 2024.2 中连接到 QEMU。 这是本系列的第 2 篇博文。要了解如何设置和使用 QEMU + 协同仿真,请参阅开发者分享|在 AMD Versal 自适应 SoC 上使用简单的 QEMU + 协同仿真示例。

2025-08-06 17:24:19 1643

1643

您将在这篇博客中了解系统设备树 (SDT) 以及如何在 AMD Vitis Unified IDE 中使用 SDT 维护来自 XSA 的硬件元数据。本文还讲述了如何对 SDT 进行操作,以便在 Vitis Unified IDE 中实现更灵活的使用场景。

2025-11-18 11:13:53 2961

2961

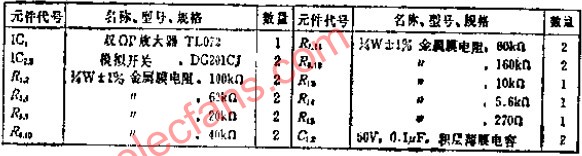

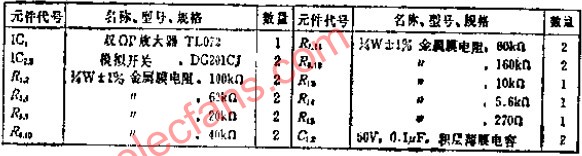

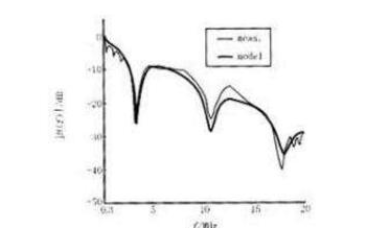

可由数字设定截止频率的可编程低通滤波器

电路的功能

2010-05-13 15:19:50 3279

3279

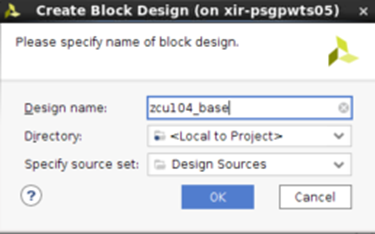

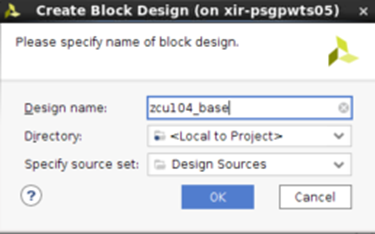

装加速平台 ;第 4 部分: 在 Vitis 中测试定制加速平台 )。 在本文中,我们将讲解如何在 Vivado Design Suite 中完成平台准备工作,以便将其用作为 Vitis 中的加速平台

2020-09-26 11:29:43 4310

4310

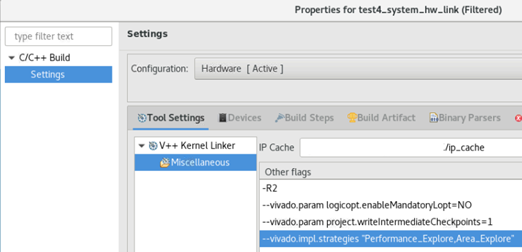

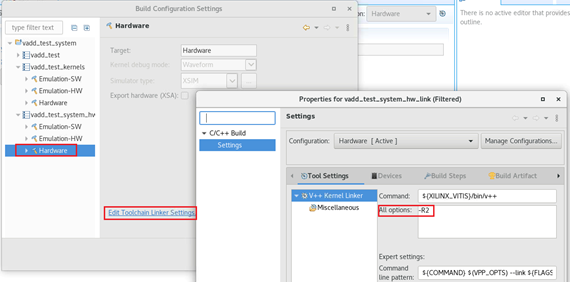

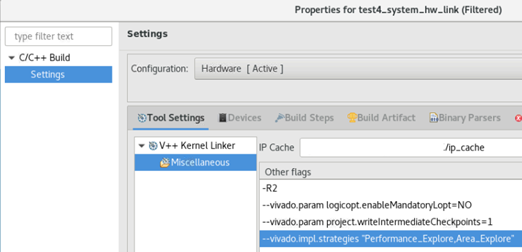

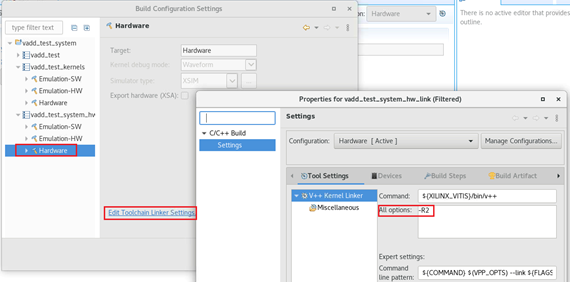

在Vitis完成这个过程的底层,实际调用的是Vivado。Vitis会指定默认的Vivado策略来执行综合和实现的步骤。当默认的Vivado策略无法达到预期的时序要求时,我们需要在Vivado中分

2022-08-02 08:03:38 1821

1821

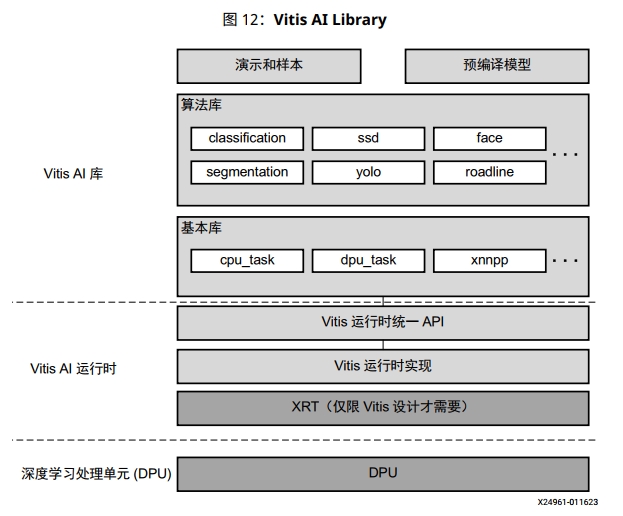

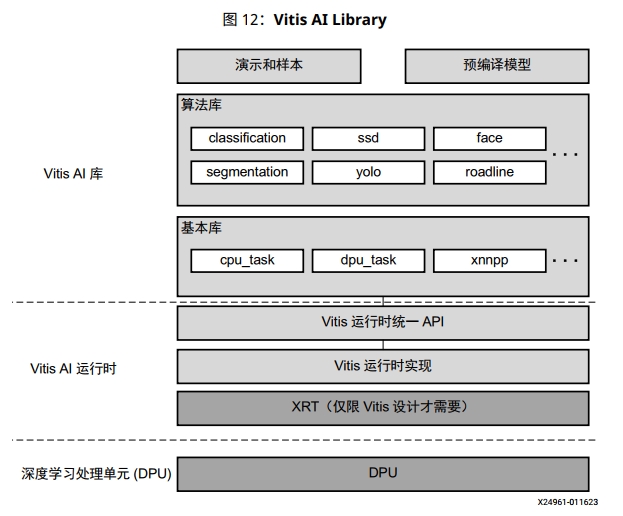

Vitis AI Library是一组高层次库和 API,专为利用 DPU 高效执行 AI 推断而构建。它是基于 Vitis AI运行时利用 Vitis运行时统一 API 来构建的,能够为 XRT 提供完整支持。

2023-10-17 08:23:20 1831

1831

Vitis AI Model Zone软件平台具备哪些功能?Vitis AI Model Zone软件平台的应用范围包括哪些?

2021-07-09 06:44:28

Vitis 已经更新到2023.2了,新版本相较于旧版本更新了嵌入式平台,新版平台增加了Versal™ AI 引擎 DSP 设计的增强功能,全新的独立 Vitis 嵌入式软件,最新 Vitis 统一

2024-03-24 16:15:14

上一章聊了一下vitis2023.2怎样使用classic Vitis IDE,这章我们来说一说基于classic Vitis

IDE的工程怎么样更新到新版本的Vitis Unified IDE

2024-03-24 17:14:43

Vitis准备工程及注意事项

2021-01-25 06:26:20

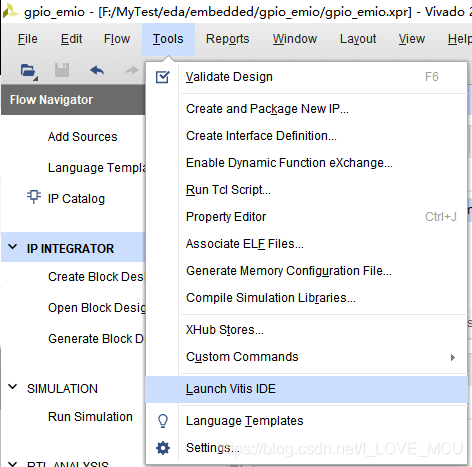

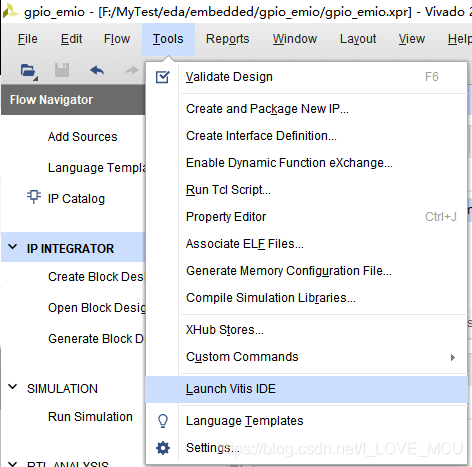

找到vitisvivado->tools->launch vitis ide如果打开失败,说明没有安装vitis,先进行安装安装vitisvivado->help->Add

2020-12-23 17:10:37

在学习ZYNQ嵌入式开发的过程中,正点原子的教程是采用SDK,而我下载的vivado2020.1已经变成了vitis,所以写一这篇博客,方便后续查阅。

2021-02-04 07:09:50

RTC介绍中断介绍Vitis程序编写

2021-02-25 07:39:08

vitis和vivado有什么区别和联系呢

2023-10-16 07:55:35

,Vivado 2019.1之前(包括),HLS工具叫Vivado HLS,之后为了统一将HLS集成到Vitis里了,集成之后增加了一些功能,同时将这部分开源出来了。Vitis HLS是Vitis AI

2022-09-07 15:21:54

求助各位高手:如何在OrCAD 16.3中, 设定Wire的宽度和颜色?而不是Line的颜色和宽度.

2012-07-20 20:32:08

指针地址调用entry函数,但asm文件指向重启函数。需求:请简要说明如何在移植的main.c中初始化kernel和系统

2020-11-19 12:03:44

linux kernel通过修改链接脚本lds文件实现,请问如何在esp32的linker.lf文件中实现?

linux kernel实现过程:

链接脚本:

. = ALIGN(4

2024-06-26 06:19:15

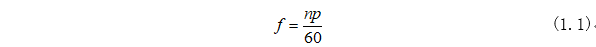

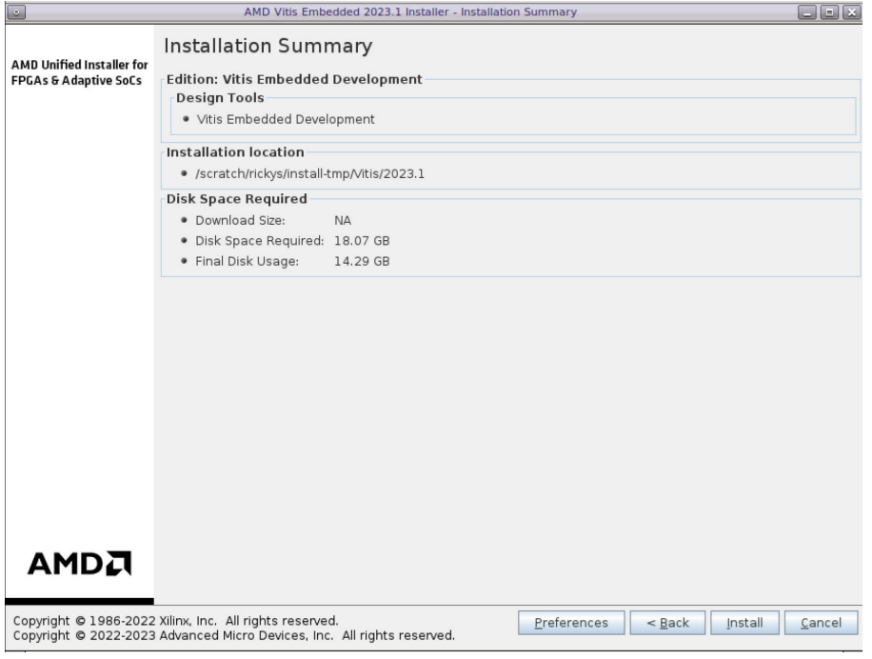

:在CentOS 7 和CentOS 8中的操作方式有些差异,需要在配置前注意系统版本,此处以CentOS-7.9为例进行说明。

1. 系统软件安装

Vitis需要一些软件或者依赖库,优先解决该

2023-08-27 21:22:34

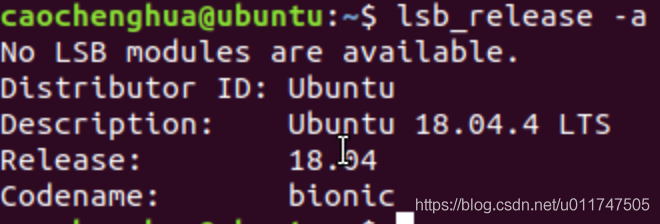

一、基础环境

硬件:KV260视觉入门套件

摄像头:海康720P USB摄像头(因为部署Vitis AI之后懒得poweroff插MIPI camera了,直接USB上)

软件:Ubuntu

2023-09-10 13:15:24

量化

七、Vitis AI 通过迁移学习训练自定义模型

八、Vitis AI 将自定义模型编译并部署到KV260中

铺垫

Vitis AI 是什么?

Vitis AI 是赛灵思公司推出的一款综合 AI

2023-10-14 15:34:26

本文将介绍如何使用Vitis-AI加速YOLOX模型实现视频中的目标检测,并对相关源码进行解读。由于演示的示例程序源码是Vitis-AI开源项目提供的,本文演示之前会介绍所需要的准备工作。演示之后

2023-10-06 23:32:47

都已编译到预构建的 Vitis AI 开发板镜像中。您可直接运行示例。如有新程序,请在主机侧对其进行编译并将可执行程序复制到目标。

1. 使用 scp 命令将

2023-09-26 16:22:43

%BD-Vitis-AI-Library

从步骤3下载

vitis-ai-runtime-3.0.0.tar.gz

安装位置为/usr/lib 和 /usr/include

这里面包含了所有需要的库。在/usr/bin中还有

2023-08-27 23:35:48

本文首先将会对Vitis统一软件平台和Vitsi AI进行简单介绍,然后介绍如何在KV260上部署DPU镜像,最后在KV260 DPU镜像上运行Vitis AI自带的图像分类示例。通过本文,你将会

2023-09-10 23:01:02

1、使用Vitis HLS创建属于自己的IP高层次综合(High-level Synthesis)简称HLS,指的是将高层次语言描述的逻辑结构,自动转换成低抽象级语言描述的电路模型的过程。对于AMD

2022-09-09 16:45:27

。3.Vitsi 开始调试在 Vivado 2019.2 中启动 Vitis 的方式 与我现在用的 vivado 2017.4 有些不一样,当然这一点也不清楚是在 2019.2 版本中做的改变还是在2018版本

2020-03-06 22:59:12

里面U-BOOT的版本为“u-boot-2013.01.01-psp06.00.00.00”,看U-BOOT里面设定MPU和DDR的频率的时候,有几点疑问:

1. 在clock.c的文件中(路径

2018-06-21 05:06:58

如何在VMware中安装ubuntu 16.04如何安装Vitis AI几个常见的docker指令

2021-02-24 06:24:00

我尝试将RTT移植到Vitis2019.2工程中,硬件平台为Zynq Ultrascale+ MPSoC ZU3EG 的自制板子。我已经移植了RTT源码/bsp/zynqmp-r5-axu4ev

2022-09-15 14:11:28

Vivado硬件平台更新后Vitis工程如何快捷更新

2021-03-08 08:00:55

如何在编程过程中修改NuMicro®系列芯片的外部晶体(H XT)的设定值?

2020-11-27 06:00:02

实时操作系统T-Kernel的源代码已在T-Engine Forum开放,它在嵌入式系统中的应用也逐渐增多。本文档总结了在新硬件中实施T-Kernel时必须探讨的事项以及实施要点等,目的是使那些对RTOS并不

2011-04-05 23:22:48 15

15 如何在PCB下设定不同的铺铜区域安全间距及切铜,有借鉴意义。

2016-12-16 21:54:48 0

0 在这个简短的视频中,您将学习如何在OpenCL 2.0中实现Sierpinski Carpet Kernel。

2018-11-07 06:20:00 3907

3907 Kernel 一般来说适用于任何机器学习算法,你可能会问为什么

2019-06-19 09:54:30 4379

4379 Vitis 2019.2 使用 gcc 编译 C 语言源代码,使用 Vivado HLS 编译与 SDAccel 流匹配的加速内核。此外,Vitis 也使用与 SDAccel 相同的目标平台和赛灵思

2020-06-28 10:05:51 2658

2658

在实际使用中不少用户只是按照变频器制造单位原有的设定值,并没有根据现场的实际情况进行调整,因而造成因载波频率值选择不当,而影响正确,感觉的有效工作状态,因此在变频器使用过程中如何来正确选择变频器的载波频率值亦是重要的事。本文就此提供应该从以下诸方面来考虑,并正确选择载波频率值的依据。

2020-07-26 11:47:32 11323

11323

在本教程中,我们将来聊一聊有关如何在 Vitis HLS 中使用 AXI4-Lite 接口创建定制 IP 的基础知识。

2020-09-13 10:04:19 7395

7395

Linux嵌入式设计中最基本的任务之一是创建用户应用程序。 在本篇博文中,我们将探讨如何在 Vitis 中使用 UIO 驱动框架创建简单的 Linux 用户应用。 1 硬件设计 本次

2020-11-20 14:05:34 5335

5335 Vitis迎来了版本更新,Vitis 2020.2 带来更加快捷智能的使用体验。首次引入Vitis™AI Engine( AI引擎)编译器,并提供多个加速功能。

2020-12-09 09:10:25 1782

1782 这是《创建 Vitis 加速平台》系列的第 3 篇博文。在前文中,我们讲解了如何创建硬件和软件工程。在本文中,我们将讲解如何在 Vitis 中将所有这些工程封装在一起。 在 Vitis 中加速软件

2020-12-26 10:20:54 3443

3443

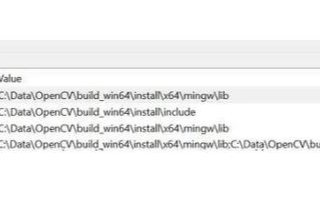

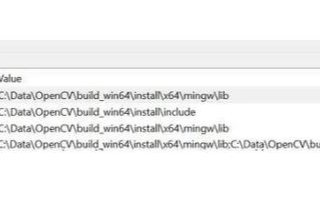

高层次综合工具中调用视觉库遇到的大多数问题都和 opencv 库以及Xilinx Vision 库的安装路径有关,如今 Vitis HLS 2020.1 之后的版本都不再提供OpenCV 的预编译库

2020-12-29 11:12:19 4272

4272

赛灵思公司(Xilinx)推出Vitis——这是一款统一软件平台,可以让包括软件工程师和AI科学家在内的广大开发者都能受益于硬件灵活应变的优势。历经5年、投入总计1000人打造而成,Vitis统一软件平台无需用户深入掌握硬件专业知识,即可根据软件或算法代码自动适配和使用赛灵思硬件架构。

2022-07-25 18:07:14 18858

18858

在学习ZYNQ嵌入式开发的过程中,正点原子的教程是采用SDK,而我下载的vivado2020.1已经变成了vitis,所以写一这篇博客,方便后续查阅。

2022-07-25 18:03:30 6190

6190

第一个Xilinx Vitis IDE入门helloworld程序

2022-07-25 17:37:23 1775

1775

在论坛上遇到在高层次综合工具中调用视觉库遇到的大多数问题都和 opencv 库以及Xilinx Vision 库的安装路径有关,如今 Vitis HLS 2020.1 之后的版本都不再提供

2021-01-27 06:17:45 6

6 赛灵思公司(Xilinx)推出Vitis——这是一款统一软件平台,可以让包括软件工程师和AI科学家在内的广大开发者都能受益于硬件灵活应变的优势。历经5年、投入总计1000人打造而成,Vitis统一软件平台无需用户深入掌握硬件专业知识,即可根据软件或算法代码自动适配和使用赛灵思硬件架构。

2021-01-31 07:49:37 16

16 在学习ZYNQ嵌入式开发的过程中,正点原子的教程是采用SDK,而我下载的vivado2020.1已经变成了vitis,所以写一这篇博客,方便后续查阅。

2021-02-21 06:48:51 20

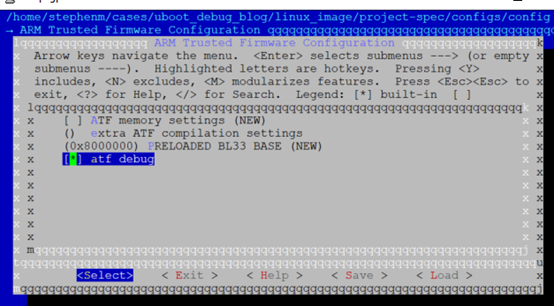

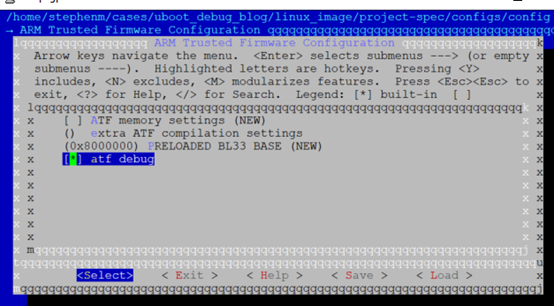

20 在本篇博文中,我们将探讨如何在 Vitis 中调试 Zynq UltraScale 器件启动镜像。这些启动镜像包括 ARM 可信固件 (ATF) 和 U-boot。 本篇博文乃是系列博文中的一篇,此

2021-06-01 15:35:45 4265

4265

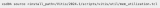

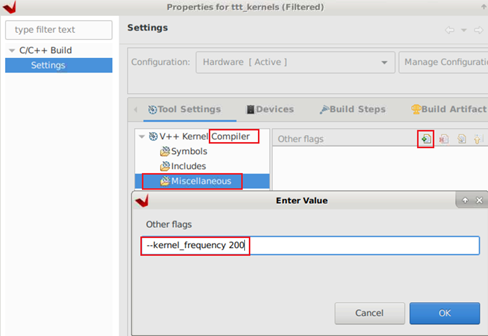

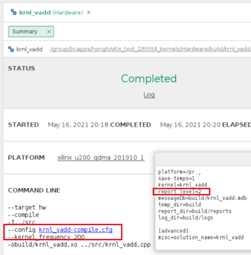

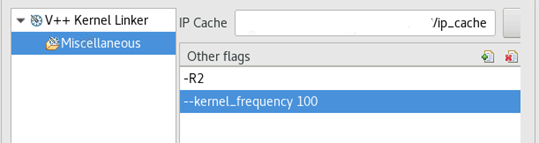

在Vitis 统一软件平台中使用Alveo系列开发板设计加速Kernel时,系统会自动为Kernel的时钟设置默认频率。 以 xilinx_u200_qdma_201910_1 平台为例,在

2021-06-12 14:19:00 37580

37580 本文来自赛灵思高级产品应用工程师 Hong Han Alveo系列开发板上的平台其实是一个DFX设计的静态部分,在Vitis 统一软件平台中使用Alveo系列开发板设计加速Kernel, 最终这些

2021-06-18 10:15:14 37454

37454 在Vitis 统一软件平台中使用v++ -link命令,可以把各种类型Kernel(C, C++, OpenCL C, 以及 RTL)的对象文件(.XO)整合到目标平台中,最终生成器件的二进制文件

2021-07-28 10:12:47 2858

2858

当 U-Boot 将设备树加载到内存指定位置后,ARM 内核的 SoC 以通用寄存器 r2 来传递 dtb 在内存中的地址。kernel 获取到该地址后对 dtb 文件做进一步的处理。 设备树的传递

2021-07-29 11:19:45 3042

3042

Q1 HLS导出的.xo文件如何导入到Vitis里面?需要把.xo文件解压,然后把文件夹导入到Vitis Kernel/src文件夹下吗? 这下图中,将xo文件作为源文件import时,xo文件显示

2021-08-26 17:03:52 3410

3410 Vitis Vision库是OpenCV和Vision功能的加速库,可在Vitis环境中使用,这些库的L1目录是示例设计。为了适应各种用户环境,从2020.1版本开始,Xilinx不再

2022-02-16 16:21:38 3239

3239

对Kernel进行性能分析需要对其进行仿真,同时还要用到Vitis Analyzer。为便于说明,我们以一个简单的Vitis工程为例。这个工程中有两个kernel,相应的代码如下图所示

2022-03-15 15:30:23 2503

2503 Vitis HLS 是一种高层次综合工具,支持将 C、C++ 和 OpenCL 函数硬连线到器件逻辑互连结构和 RAM/DSP 块上。Vitis HLS 可在Vitis 应用加速开发流程中实现硬件

2022-05-25 09:43:36 3450

3450 生成的 device tree 里 axigpio core 的 driver 是 xilinx driver,我们需要把它替换为我们生成的 kernel module 的 drivername

2022-06-30 09:48:49 1144

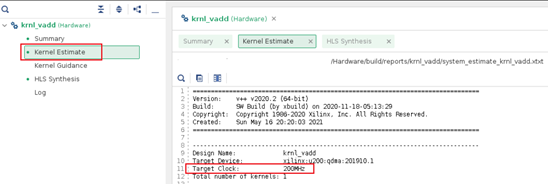

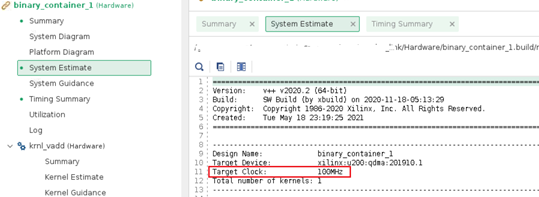

1144 在Kernel Estimate报告中,可以看到,Target Clock已经按要求设置成200Mhz. 说明 Vitis_HLS是按照200Mhz的要求来综合Kernel的代码的.

2022-07-01 09:52:53 37149

37149 您是否想创建自己带有 AXI4-Lite 接口的 IP 却感觉无从着手?本文将为您讲解有关如何在 Vitis HLS 中使用 C 语言代码创建 AXI4-Lite 接口的基础知识。

2022-07-08 09:40:43 2808

2808 HLS导出的.xo文件如何导入到Vitis里面?需要把.xo文件解压,然后把文件夹导入到Vitis Kernel/src文件夹下吗?

2022-08-03 11:20:26 3933

3933

本篇博文将继续介绍在Vitis中把Settings信息传递到底层的Vivado。

2022-08-02 10:26:41 1517

1517

Alveo系列开发板上的平台其实是一个DFX设计的静态部分,在Vitis 统一软件平台中使用Alveo系列开发板设计加速Kernel, 最终这些Kernel的逻辑会在分布在DFX设计的动态区域。

2022-08-02 09:38:37 37376

37376

在本篇博文中,我们将探讨如何在 Vitis 中调试 Zynq UltraScale 器件启动镜像。这些启动镜像包括 ARM 可信固件 (ATF) 和 U-boot。

2022-08-02 10:14:59 5052

5052

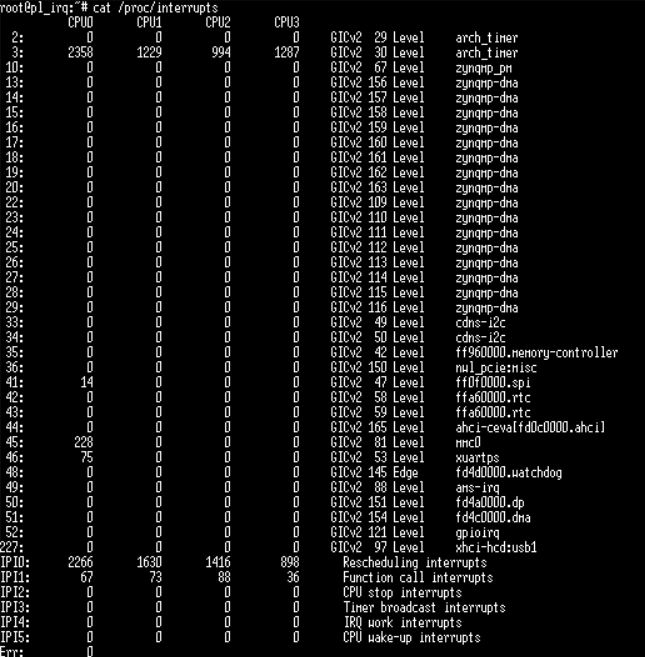

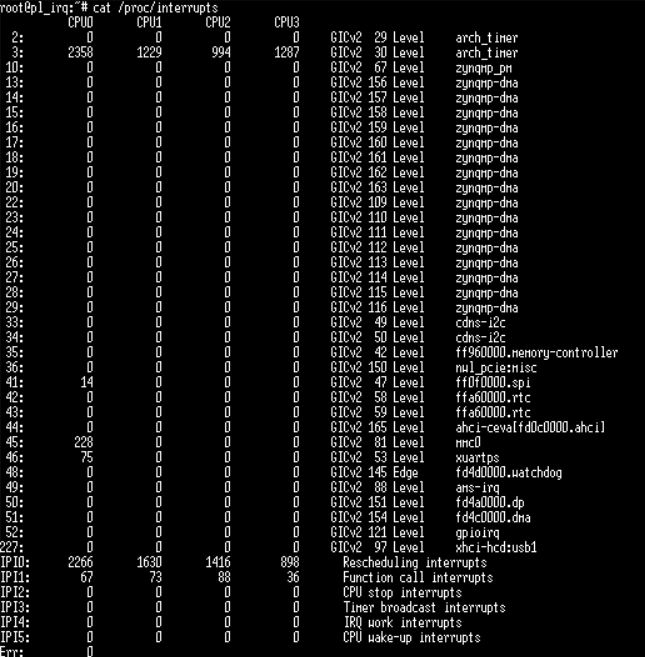

有时我们需要为官方 IP 或者自己创建的 IP 生成 kernel module,然后在 linux kernel space 里使用 kernel module 来控制这个 IP。如果要使用 IP 中断,我们需要在 kernel module 代码里获取设备中断并建立中断服务程序。

2022-08-02 11:35:23 963

963

在 AXI 基础第 6 讲 - Vitis HLS 中的 AXI4-Lite 简介中,使用 C 语言在 HLS 中创建包含 AXI4-Lite 接口的 IP。在本篇博文中,我们将学习如何导出 IP

2022-08-02 09:43:05 1247

1247

Vitis HLS 工具能够将 C++ 和 OpenCL 功能部署到器件的逻辑结构和 RAM/DSP 块上。在 GitHub 上提供 Vitis HLS 前端为研究人员、开发人员和编译器爱好者开启了无限可能的新世界,使他们可以利用 Vitis HLS 技术并根据其应用的特定需求进行修改。

2022-08-03 09:53:58 1602

1602 对于AMD Xilinx而言,Vivado 2019.1之前(包括),HLS工具叫Vivado HLS,之后为了统一将HLS集成到Vitis里了,集成之后增加了一些功能,同时将这部分开源出来了。Vitis HLS是Vitis AI重要组成部分,所以我们将重点介绍Vitis HLS。

2022-09-02 09:06:23 4612

4612 电源技巧:如何在隔离式电源中测量频率响应

2022-11-04 09:51:39 0

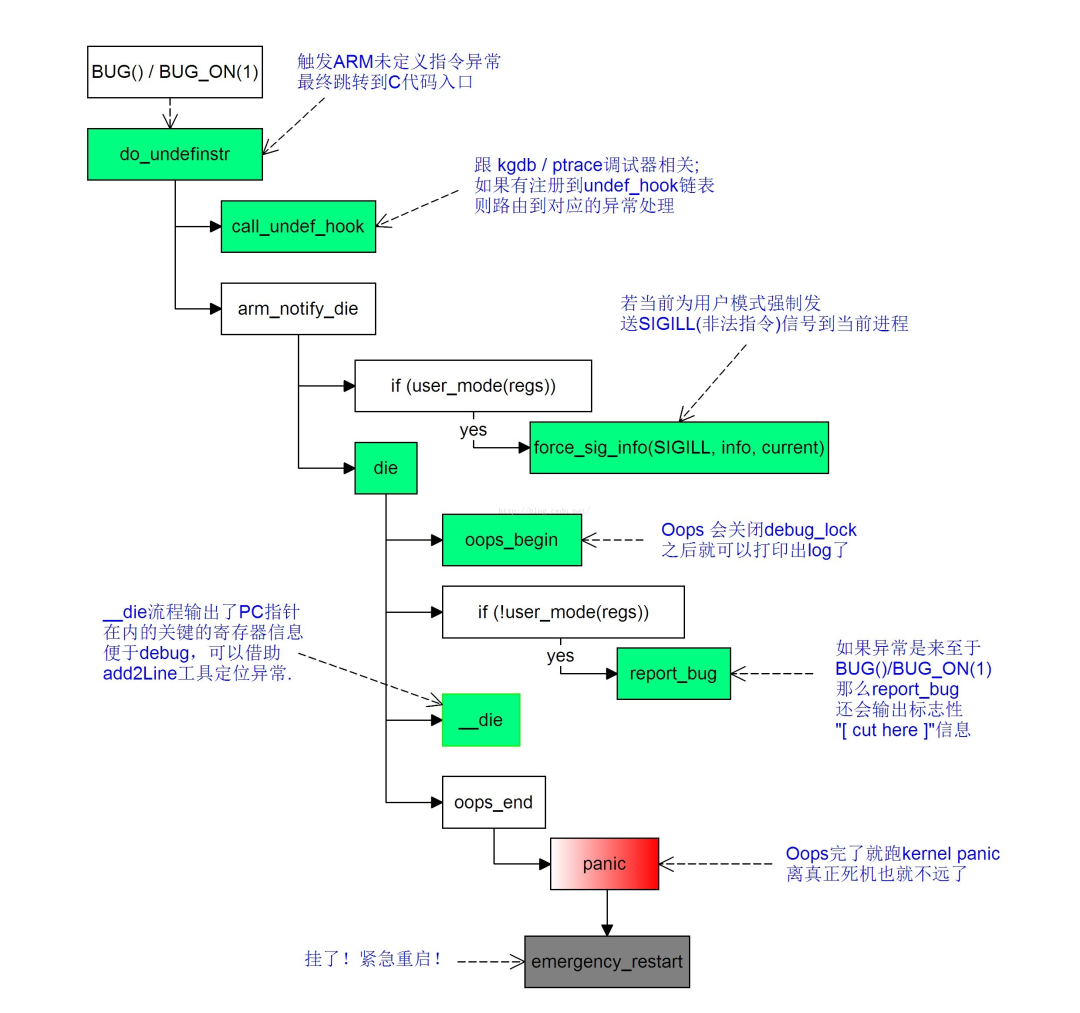

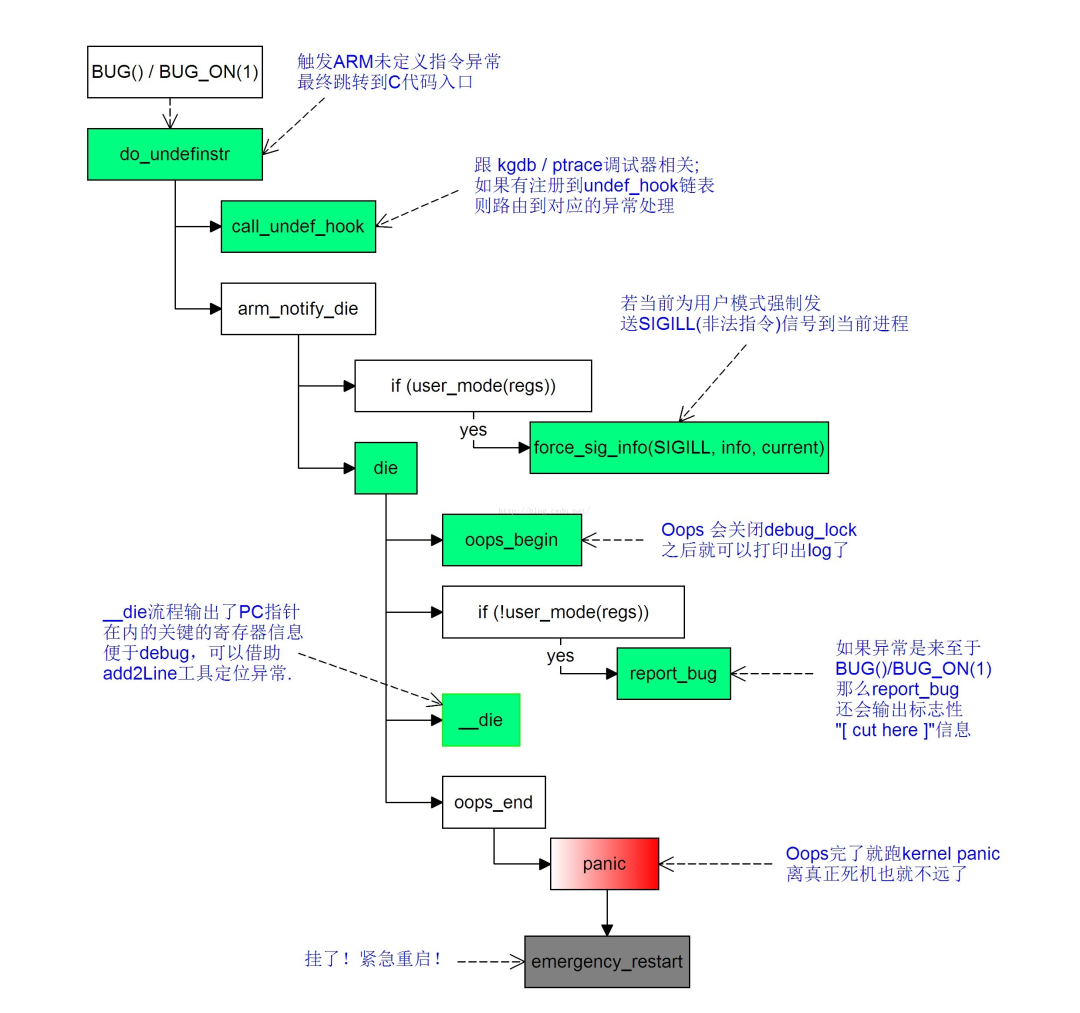

0 我们在项目开发过程中,很多时候会出现由于某种原因经常会导致手机系统死机重启的情况(重启分Android重启跟kernel重启,而我们这里只讨论kernel重启也就是 kernel panic 的情况

2023-01-19 16:14:00 1931

1931

电机控制中载波频率是非常重要的因素,其值不能设定太高,同样也不能设定太低,通常载波频率设定与五个因素有关:基波频率、硬件限制、谐波电流、内部软件的实现、功率模块温升,这期主要讲讲与这几个因素有关的原因。

2023-01-13 14:58:50 16584

16584

AMD Vitis HLS 工具允许用户通过将 C/C++ 函数综合成 RTL,轻松创建复杂的 FPGA 算法。Vitis HLS 工具与 Vivado Design Suite(用于综合、布置和布线)及 Vitis 统一软件平台(用于所有异构系统设计和应用)高度集成。

2023-04-23 10:41:01 1730

1730

在本快速入门演示中,将探讨如何在 Vitis 中使用 Git 集成以及如何使用团队操作来共享 Vitis 工程。

2023-05-12 15:01:00 1889

1889

本文演示了在Vitis™ 中对 Linux 应用程序开发的过程中如何使用外部库

2023-07-07 14:14:51 1792

1792

Vitis™ HLS 2023.1 支持新的 L1 库向导,本文将讲解如何下载 L1 库、查看所有可用功能以及如何在 Vitis HLS GUI 中使用库函数。

2023-08-16 10:26:16 2123

2123

本文首先将会对Vitis统一软件平台和Vitsi AI进行简单介绍,然后介绍如何在KV260上部署DPU镜像,最后在KV260 DPU镜像上运行Vitis AI自带的图像分类示例。通过本文,你将会

2023-09-12 10:02:08 3326

3326

电子发烧友网站提供《Vitis AI优化器指南.pdf》资料免费下载

2023-09-14 11:04:38 2

2 电子发烧友网站提供《Vitis Model Composer教程.pdf》资料免费下载

2023-09-14 09:52:29 7

7 档旨在逐步指导您熟悉各种 Vitis 工具,这些工具采用自下而上的设计流程来开发系统组件,随后将其集成到顶层系统工程中。 如果您希望获取完整版用户指

2023-09-13 08:15:02 1792

1792

电子发烧友网站提供《Vitis AI用户指南.pdf》资料免费下载

2023-09-13 15:00:21 3

3 电子发烧友网站提供《Vitis HLS移植指南.pdf》资料免费下载

2023-09-13 09:21:12 1

1 本文将介绍如何使用Vitis-AI加速YOLOX模型实现视频中的目标检测,并对相关源码进行解读。由于演示的示例程序源码是Vitis-AI开源项目提供的,本文演示之前会介绍所需要的准备工作。演示之后会对关键源码进行解析。

2023-10-16 15:43:25 2612

2612

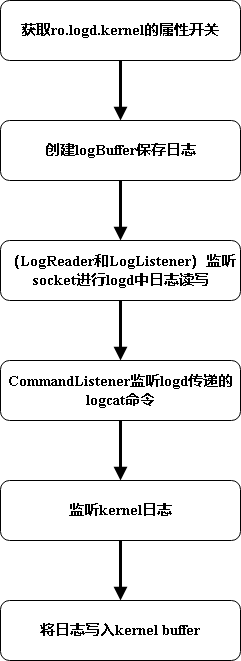

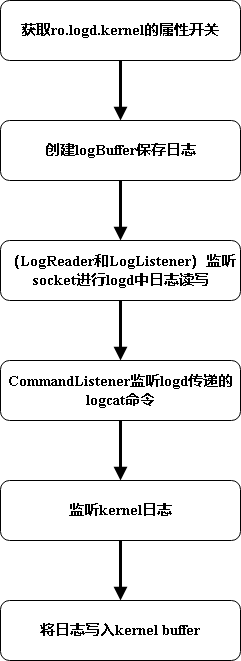

kernel日志写入logd介绍 通过logcat命令获取kernel日志比较特殊,故作为一个例子进行梳理。 2.3.1 整体流程 2.3.2 命令打印kernel日志 通过logcat -b

2023-11-23 17:11:17 1435

1435

AMD Vitis 软件平台是一款开发环境,主要用于开发包括 FPGA 架构、Arm 处理器子系统和 AI 引擎在内的设计。Vitis 工具与 AMD Vivado ML 设计套件相结合,可为

2023-12-20 10:00:02 1414

1414

电子发烧友网站提供《Vitis AI用户指南.pdf》资料免费下载

2024-01-03 10:51:52 5

5 本篇文章将演示创建一个使用 AMD Vitis™ 视觉库的 Vitis HLS 组件的全过程。此处使用的是 Vitis Unified IDE。如果您使用的是旧版 AMD Vitis Software Platform,大多数步骤相同。

2024-05-08 14:02:52 1743

1743

AMD Vitis™ 2023.2 设计工具是 Vitis 设计工具变化较大的一个版本,设计流程和界面都发生了变化。

2024-05-29 09:50:26 1465

1465

,并在 Unified IDE 中仍可使用。本文涵盖了如何在 Vitis 中使用分析工具在应用程序调试期间对栈和堆进行监控。

2025-10-24 16:54:06 708

708

与电机匹配问题 当电机负载惯性过大或存在机械卡阻时,变频器可能自动降低输出频率以保护系统。例如离心泵负载若叶轮变形,会导致实际运行频率始终低于设定值5-10Hz。此时需检查: 1. 机械传动系统润滑状态。 2. 联轴器对中精度

2026-01-05 07:39:41 26

26

电子发烧友App

电子发烧友App

评论