介绍

DesignLinx 及其客户是赛灵思 SDAccel 开发环境的早期用户。他们使用 SDAccel 开发环境,针对搭载加速软件的亚马逊 AWS F1 和赛灵思 Alveo 数据中心加速器卡,开发云端应用和本地应用。

结合 SDSoC 和赛灵思 SDK,SDAccel 流现在是 2019.2 Vitis 统一软件平台的组成部分,便于开发者针对赛灵思器件上的所有软件任务使用统一平台。下面分享来自 DesignLinx 公司高级嵌入式软件工程师 Nathan Sullivan 所撰写的技巧:

1. Vitis 的优势

Vitis 2019.2 采用经过更新的 v++ 编译器,强化 IDE 项目组织,为嵌入式应用和数据中心应用提供统一的工具流。因为全部三种流程现在都集成在 Vitis 内部,所以无需针对不同类型的应用在 SDAccel、SDK 和 SDSoC 之间进行切换。除了 Vitis IDE 以外,通过 v++ 工具和 SDAccel 提供的 xocc/xcpp 流等生成文件,也为构建软件提供完整的命令行流程。

2. 易于迁移

Vitis 2019.2 使用 gcc 编译 C 语言源代码,使用 Vivado HLS 编译与 SDAccel 流匹配的加速内核。此外,Vitis 也使用与 SDAccel 相同的目标平台和赛灵思运行时。这意味着新环境能够兼容源代码,SDAccel 项目只需少量修改或完全无需任何修改就能在 Vitis 内完成构建。在迁移源代码时,用户能够使用 Vitis IDE 或 v++ 命令行工具链选择性构建新项目。

3. IDE 迁移

使用 Vitis IDE 迁移项目时,只需将所有源代码文件从 SDAccel 项目添加到新的 Vitis 项目中,最好是指向同一器件。使用右键菜单上的“import sources”选项能够轻松完成这一操作。一旦源文件导入完成,必须向二进制容器添加内核函数(如同它们在原始项目中那样),并且任何定制构建设置也需要手动复制。

4. 命令行迁移

要对使用命令行(通常是通过生成文件)构建的项目进行迁移,必须用 v++ 调用替换 xocc 调用。类似地,必须用 g++ 调用替换 xcpp 调用,即直接调用主机 c++ 编译器。新的 v++ 工具提供的命令行选项与 SDAccel 下的 xocc 工具一样,因此无需做其他修改。请参阅 UG1393 进一步了解 Vitis 2019.2 有关工具变化的详细说明。

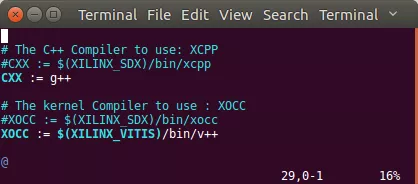

在 SDAccel 样例生成文件中替换 XOCC 和 CXX

修改完成后,就可以使用 Vitis 工具构建之前的 SDAccel 项目:

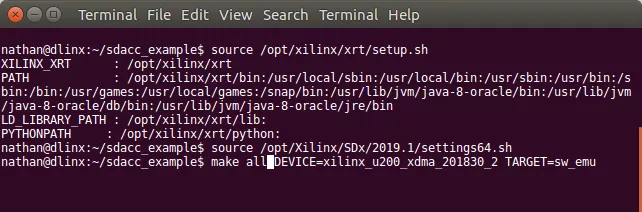

和以往一样构建 SDAccel 示例,但这次使用 Vitis 路径和工具

5.结论

虽然 Vitis 2019.2 将所有赛灵思软件工具集成在统一平台上,但 SDAccel 流并没有显著变化,这使得迁移工作简单易行。现有项目在源代码上兼容新工具链,因此基本无需修改,它们就能直接获得 Vitis 2019.2 统一软件平台提供的优势。

赛灵思高级合作伙伴 DesignLinx 为运行在 Vitis 和 SDAccel 平台上的加速应用提供开发服务,同时提供云端和本地硬件部署服务。

-

赛灵思

+关注

关注

33文章

1798浏览量

133663 -

数据中心

+关注

关注

18文章

5773浏览量

75209

原文标题:将 SDAccel 项目迁移到 Vitis 2019.2 的技巧

文章出处:【微信号:FPGA-EETrend,微信公众号:FPGA开发圈】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

Freescale半导体QFN封装迁移及MC9S08QG8/4微控制器解析

基于Vitis Model Composer完成全流程AI Engine开发

急急急!我正在使用vivado2019.2,请帮忙生成一个项目。

电子材料抗离子迁移方案!东亚合成 IXE/IXEPLAS,智美行科技免费试样

无质量损失的数据迁移:Nikon SLM Solutions信赖3Dfindit企业版

如何在AMD Vitis Unified IDE中使用系统设备树

AMD Vitis AI 5.1测试版现已开放下载

AMD Vitis AI 5.1测试版发布

如何在AMD Vitis Unified 2024.2中连接到QEMU

全新AMD Vitis统一软件平台2025.1版本发布

使用AMD Vitis Unified IDE创建HLS组件

如何使用AMD Vitis HLS创建HLS IP

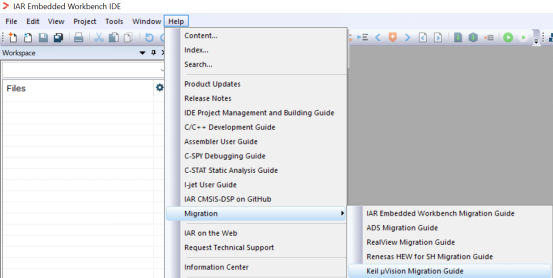

从Keil MDK到IAR EWARM:通过工程迁移实现项目资产的更好管理

将SDAccel项目迁移到Vitis 2019.2的技巧

将SDAccel项目迁移到Vitis 2019.2的技巧

评论