在Vitis 统一软件平台中使用Alveo系列开发板设计加速Kernel时,系统会自动为Kernel的时钟设置默认频率.

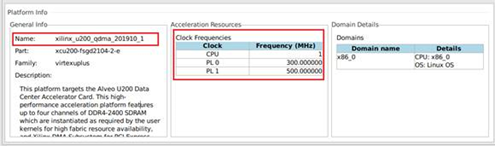

以 xilinx_u200_qdma_201910_1 平台为例,在Vitis中选择平台时可以看到默认的时钟频率是300Mhz和500Mhz.

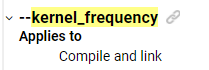

在Vitis Application Acceleration Development Flow 中我们看到--kernel_frequency选项可以用于覆盖默认的 Kernel 频率

(https://www.xilinx.com/html_docs/xilinx2020_2/vitis_doc/buildtargets1.html#ldh1504034328524)

那么 --kernel_frequency设置在Compile阶段或者Link阶段有什么区别呢?

我们以经典 Example design“Vector Addition” 为例探索一下:

1. 打开Vitis 2020.2,创建新的 Application Project

File -> New -> Application project

2. 选择 xilinx_u200_qdma_201910_1 平台

3. 选择打开 Example Design "Vector Addition"

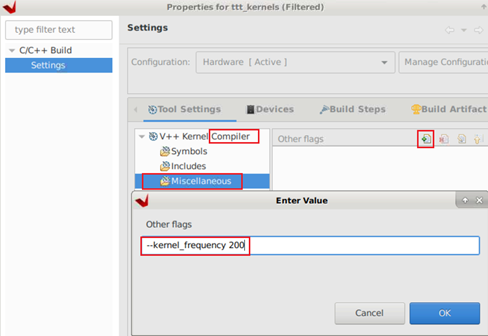

4.对 Hardware Flow 在Compile阶段设置“kernel_frequency” 为200MHz,然后编译工程

注意:默认的Kernel频率只允许改小,不允许改大.

在log看到执行的命令是:

v++ --target hw --compile --kernel_frequency 200 …

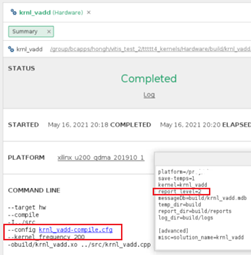

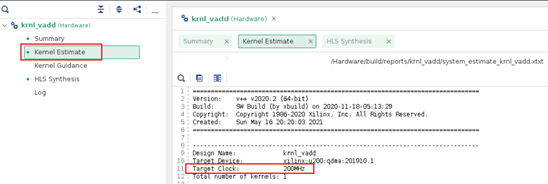

5. Compile Kernel 完成后可以在Compile Summary中看到“--kernel_frequency 200" 已经设置成功.

在Kernel Estimate报告中,可以看到,Target Clock已经按要求设置成200Mhz. 说明 Vitis_HLS是按照200Mhz的要求来综合Kernel的代码的.

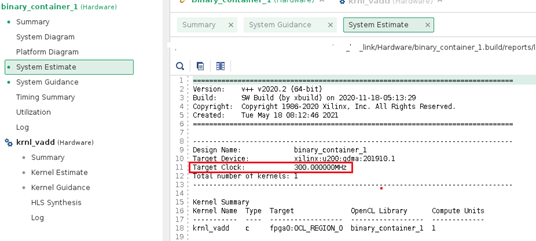

在Link Summary中可以看到,在把Kernel合入平台后的Implementation中,目标时钟还是平台默认的300Mhz,而不是在Compile 阶段设置的200Mhz.

同时我们也可以翻看Implemented Design的时序报告(Timing Summary)查看Kernel实际的时钟要求:

clk_out1_pfm_top_clkwiz_kernel_0_1 {0.000 1.667} 3.333 300.000

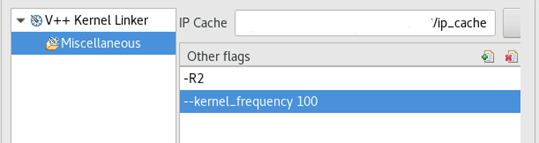

6. 在Link阶段加上“--kernel_frequency 100" 选项

在log看到执行的命令是:

v++ --target hw --link -R2 --kernel_frequency 100 …

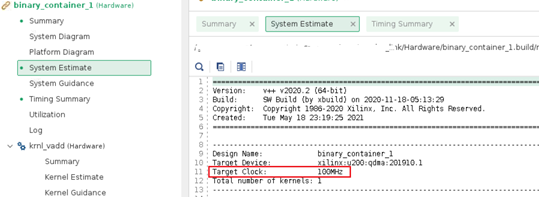

7. 完成Hardware Build之后,查看Summary,可以看到这时100Mhz Kernel 频率的设置在整个Vitis Platform Link生效, 覆盖默认的300Mhz

和之前一样翻看Implemented Design的时序报告(Timing Summary)查看Kernel实际的时钟要求,kernel的目标频率已经被正确修改了.

clk_out1_pfm_top_clkwiz_kernel_0_1 {0.000 5.000} 10.000 100.000

总结:

选项“--kernel_frequency" 加在Compile阶段,影响的是对Kernel做高级综合的Vitis_HLS的目标频率,不影响Kernel合入平台后的Implementation的目标频率;

选项“--kernel_frequency" 加在Link阶段, 不会影响对Kernel做高级综合的Vitis_HLS的默认目标时钟频率,但是可以设置Kernel合入平台后的Implementation的目标频率

审核编辑 :李倩

-

Kernel

+关注

关注

0文章

49浏览量

11989 -

Vitis

+关注

关注

0文章

154浏览量

8260

原文标题:开发者分享 | 如何在Vitis中设定Kernel 的频率

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

如何在AMD Vitis Unified IDE中使用系统设备树

AMD Vitis AI 5.1测试版现已开放下载

AMD Vitis AI 5.1测试版发布

如何在AMD Vitis Unified 2024.2中连接到QEMU

如何在Unified IDE中创建视觉库HLS组件

使用AMD Vitis Unified IDE创建HLS组件

如何使用AMD Vitis HLS创建HLS IP

CPU怎么降频 bios中如何把cpu调低频率

使用AMD Vitis进行嵌入式设计开发用户指南

如何在Vitis中设定Kernel的频率

如何在Vitis中设定Kernel的频率

评论