在无线通信中,功率测量是一个关键环节。无论是日常使用的手机信号,还是复杂的雷达系统,都需要精确测量信号的功率。功率过大可能干扰其他设备,过小又会影响通信质量。本文将介绍几种常见的射频信号功率测量方法,帮助大家理解如何准确测量不同信号的功率。

2025-06-26 10:14:12 1922

1922

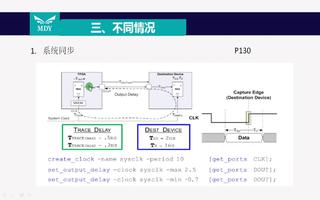

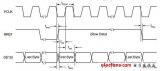

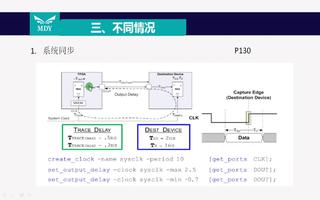

对于数据采集接收的一方而言,所谓源同步信号,即传输待接收的数据和时钟信号均由发送方产生。FPGA应用中,常常需要产生一些源同步接口信号传输给外设芯片,这对FPGA内部产生

2012-05-04 11:42:26 6415

6415

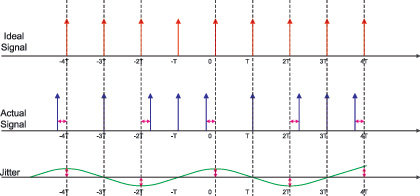

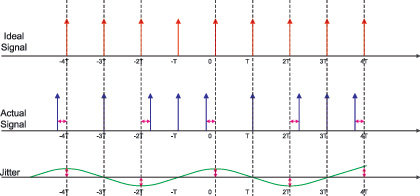

为了正确理解时钟相关器件的抖动指标规格,同时选择抖动性能适合系统应用的时钟解决方案,本文详细介绍了如何理解两种类型时钟驱动器的抖动参数,以及从锁相环输出噪声特性理解时钟器件作为合成器、抖动滤除功能时的噪声特性。

2013-06-21 15:40:41 19925

19925

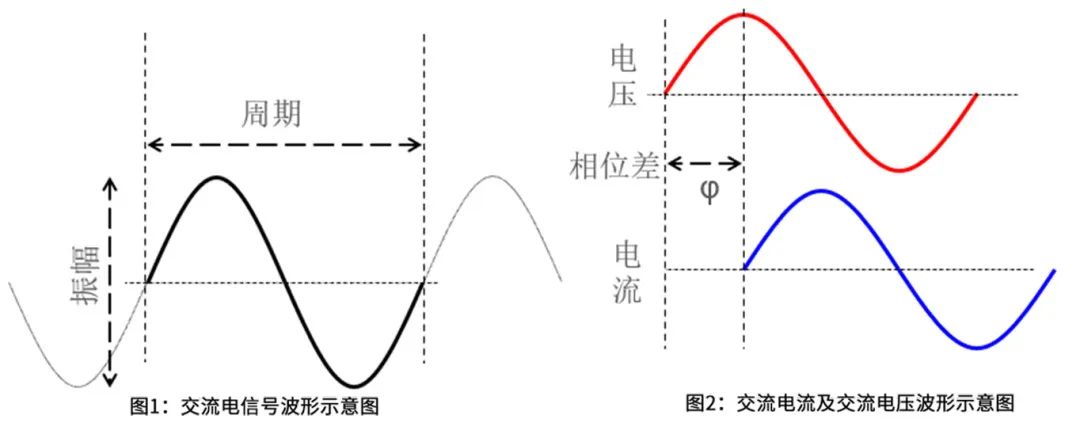

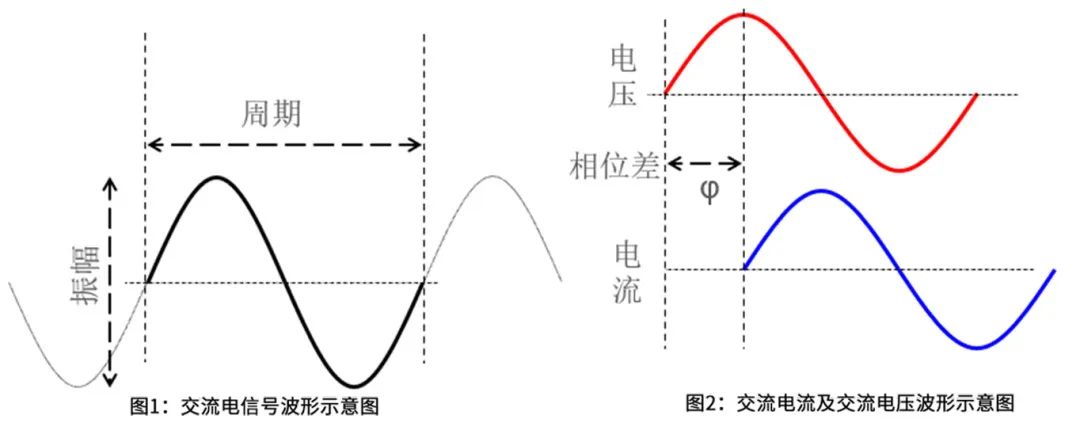

使用功率分析仪测量数据时,要选择合适的同步源,如果同步源设定不当,测量值有可能不稳定或出现错误,谐波测量模式还要选择合适的PLL源,不少客户经常提出疑惑,同步源和PLL源有什么异同,他们的作用是什么?

2015-07-09 10:37:11 4830

4830

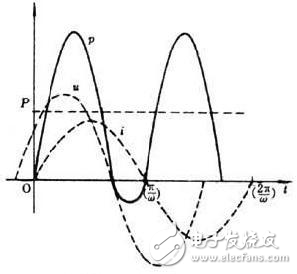

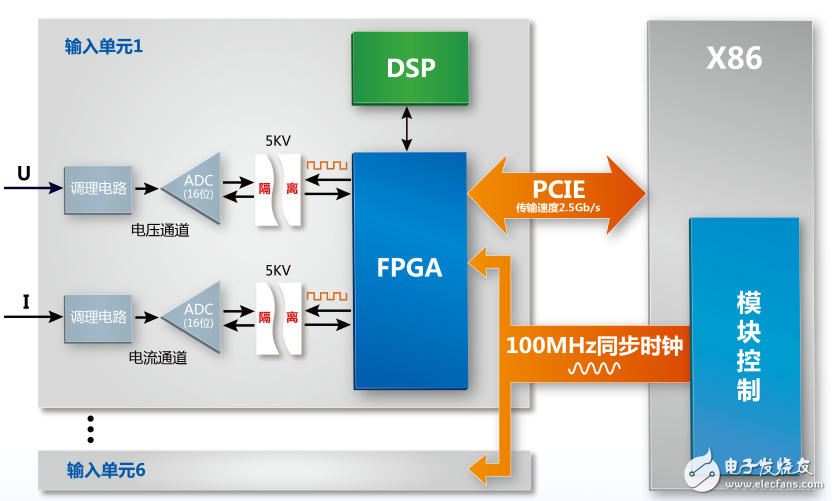

我们在使用示波器的时候,要想稳定的显示波形,我们往往需要选择一个合适的触发方式。而在功率测量领域,如何实现“电压”和“电流”的同步测量至关总要,今天我们就来揭秘周立功致远电子是如何来实现功率测量的“神同步”!

2015-07-22 16:30:56 3331

3331

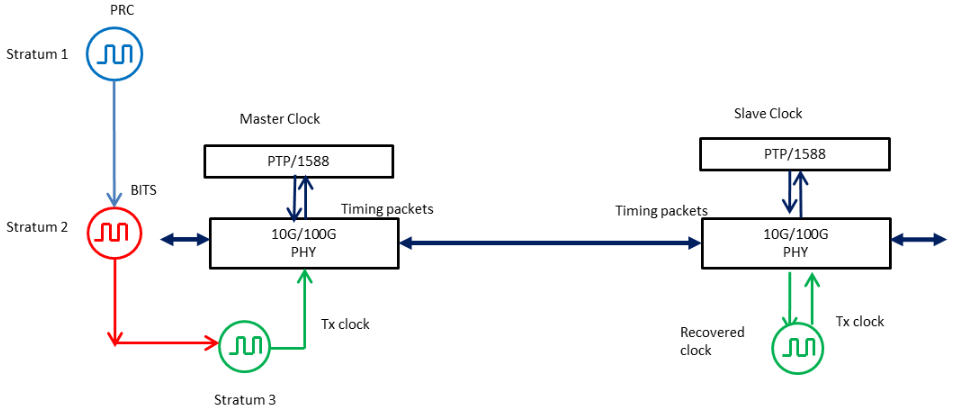

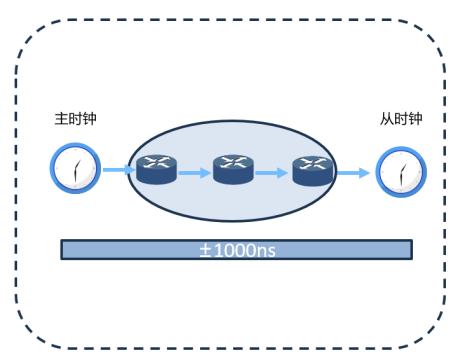

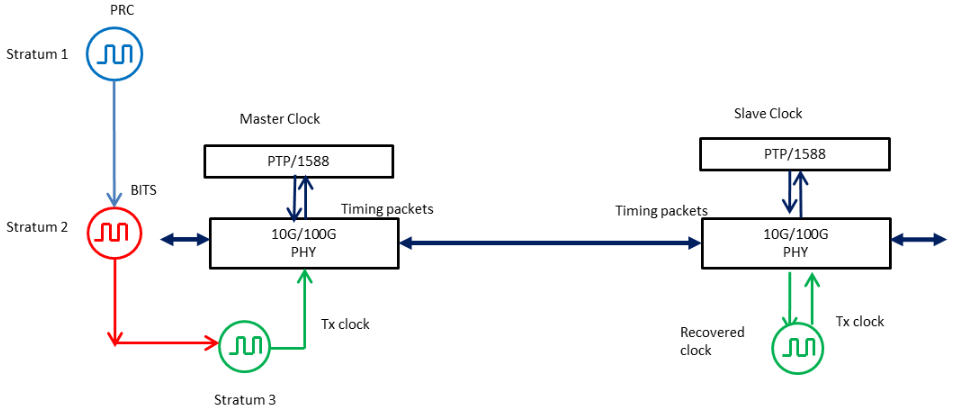

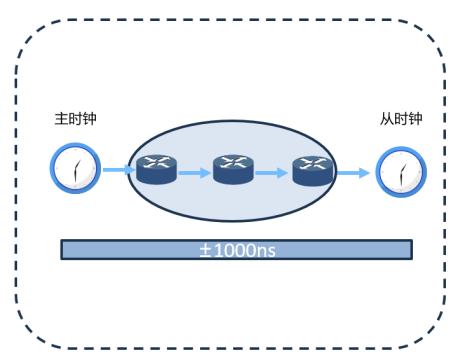

同步以太网是一种采用以太网链路码流恢复时钟的技术, 简称SyncE。同步以太网通过从串行数据码流中恢复出发送端的时钟,从而实现网络时钟同步。但SyncE不能提供时间同步。

2020-05-12 09:24:02 2733

2733

FPGA与外部器件共用外部时钟;源同步(SDR,DDR)即时钟与数据一起从上游器件发送过来的情况。在设计当中,我们遇到的绝大部分都是针对源同步的时序约束问题。所以下文讲述的主要是针对源同步的时序约束。 根据网络上收集的资料以及结合自

2020-11-20 14:44:52 9157

9157

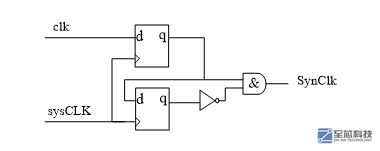

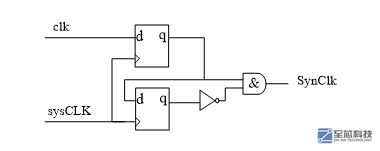

时钟使能电路是同步设计的重要基本电路,在很多设计中,虽然内部不同模块的处理速度不同,但是由于这些时钟是同源的,可以将它们转化为单一的时钟电路处理。在FPGA的设计中,分频时钟和源时钟的skew不容易

2020-11-10 13:53:41 6225

6225

如果在主机架中包含 CP1243-1 等 CP 模块,而这些 CP 也是有时钟的,一般情况下需要将 CPU 和 CP 进行时间同步,在一个机架中只需有一个 CPU 或者 CP 作为 NTP 客户端

2022-12-14 09:26:23 7286

7286 你是否曾好奇过,手机、电脑甚至智能手表的时间为何能精准同步?这背后离不开两类关键元器件的协作:时钟芯片和晶振。尽管它们都与时间信号相关,但功能定位和技术原理却截然不同。本文将深入解析两者的区别,帮助

2025-12-16 15:58:04 3878

3878

学习STM32的同学知道,STM32有好多时钟,如32.768Khz,8Mhz,被时钟树搞迷糊了,下面一一解析。HSE:高速外部时钟信号(4--16Mhz常用的为8Mhz)HSI:高速内部时钟信号

2017-04-27 16:34:26

工作。唯有通过参考时钟来同步这样的“对表操作”,才能让它们步调一致,从而紧密连接形成网络。

对于参考时钟,它首先要确定一个参考源,然后再是不同节点之间的同步关系。在通信系统中,一般来说精度较低的节点

2023-05-10 17:09:50

利用9401测量频率,采用“隐式测量”,可以测量,但是采样率与信号频率一致。现在希望可以自己设定采样率,所以必须要设置成“采样时钟”但是设置成采样时钟后,必须要提供“外部时钟”(测量频率必须要提供

2017-04-12 23:48:44

,这个选通信号也可以称为源同步时钟信号。源同步时钟系统中,数据和源同步时钟信号是同步传输的,我们保证这两个信号的飞行时间完全一致,这样只要在发送端的时序是正确的,那么在接收端也能得到完全正确的时序。整个

2014-12-30 13:54:22

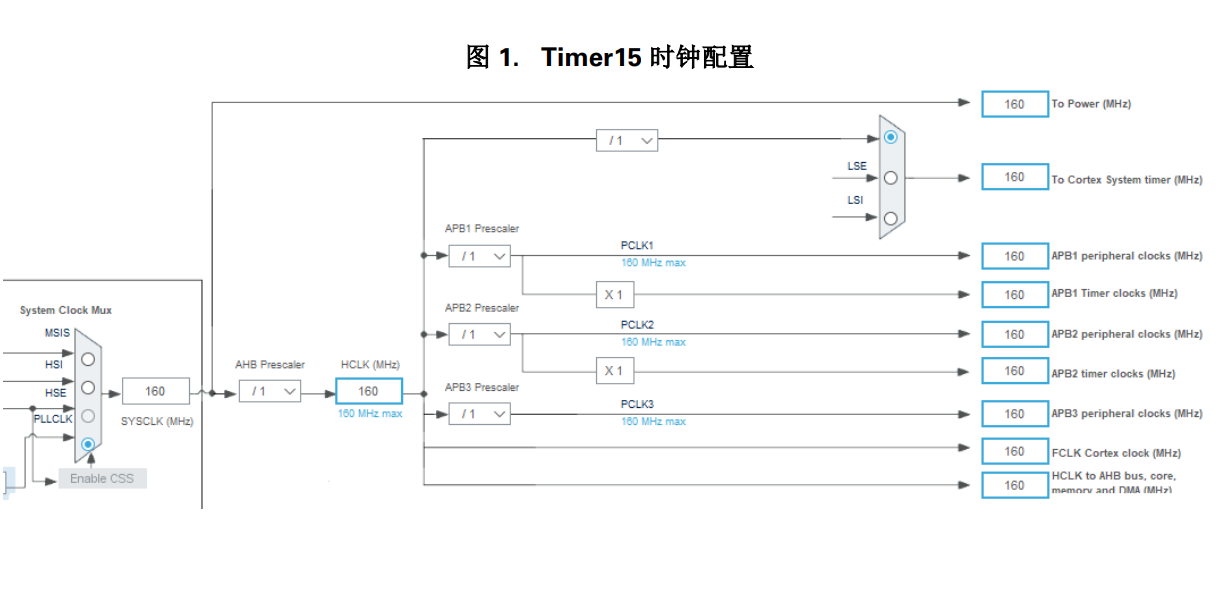

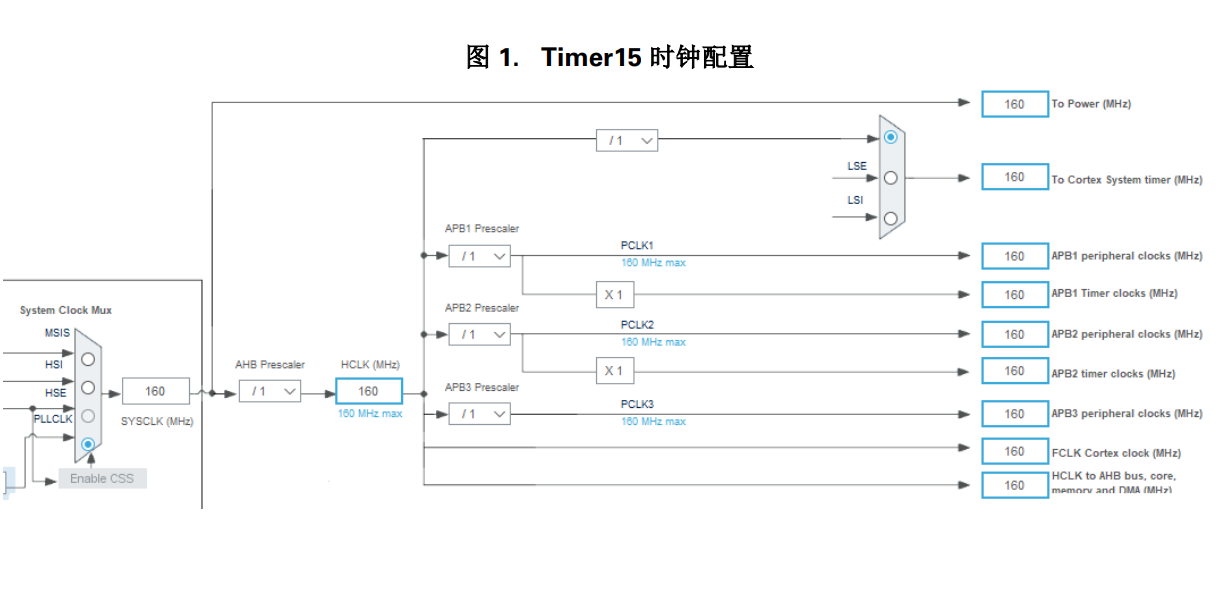

STM32中定时器的时钟源是什么?

2021-11-24 06:22:09

一、在STM32中,有五个时钟源,为HSI、HSE、LSI、LSE、PLL。①HSI是高速内部时钟,RC振荡器,频率为8MHz。②HSE是高速外部时钟,可接石英/陶瓷谐振器,或者接外部时钟源,频率范围为4MHz~16MHz。③LSI是低速内部时钟,RC振荡器,频率...

2021-08-13 07:24:19

:时钟频率速度,英语:clock rate),是指同步电路中时钟的基础频率,它以“若干次周期每秒”来度量,量度单位采用SI单位赫兹(Hz)。它是评定CPU性能的重要指标。一般来说主频数字值越大越好...

2021-08-18 07:21:56

在学习STM32的过程中,一个需要我们理解的知识点就是时钟STM32的时钟源有4个:HSL :内部高速时钟源HSE:外部高速时钟LSl:低速内部时钟LSE:低速外部时钟STM32输入时钟源1.1

2021-08-19 07:06:25

在看u***,书上说u***数据包的同步域可以同步主机端和从机端的时钟,这个怎么理解u***接口没有时钟线,我又想到了单片机串口的波特率,不知道有没有关系,向大家请教了这个简单的问题,很想知道答案

2019-07-02 18:06:13

就是时钟同步,计数器输出脉冲和数字I/O口接受脉冲数据同时进行,如何将计数器通道的时钟作为数字通道的时钟源啊?同时数字通道中还有触发,触发的时钟源也是计数器的时钟 如图中所示,这是别人做的,但是我

2015-01-14 11:26:01

对stm32时钟源的进一步理解stm32中五个时钟源的介绍HSI 是高速内部时钟,RC 振荡器,频率为 8MHz。HSE 是高速外部时钟,可接石英/陶瓷谐振器,或者接外部时钟源,频率范围为4MHz

2021-08-18 07:45:18

源同步输入的1080P视频信号,148.5M时钟,从fifo写入端输入。读出端时钟采用50M主时钟经2级DCM产生148.5M的时钟clkfx。然后输出到pad给下级器件。请问此方案是否合理?疑问是输出时序如何确定?调整?器件选用spartan3 1400a。希望***下

2015-01-21 14:20:53

为什么功率测量需要时钟?同步源是什么?

2021-05-11 06:39:23

一个紧密同步的仪器中。图1.一个ADALM1000 SMU通道的框图。所述ADALM1000处于其心脏一个源测量单元,但它也可以被看作是一个独立的示波器和函数发生器。但是,由于输出功能(发生器)和输入

2018-10-24 10:34:08

我正在使用由计时器触发的注入转换来测量缓冲电压。如参考手册中所述,我已将 ADC 的频率限制为 F_adc < F_adc_hclk/4。当我使用同步时钟

2023-01-04 07:11:27

,这个接口是不是读FD的数据的时钟啊?就一个输入时钟,它同步到底是和谁同步?异步是与谁异步?我理解的意思是:同步就是读和写的速度一样,异步就是不一样,要注意它到底能缓存多少,最终的速率是否满足。我只要

2016-12-15 10:34:51

STM32F103学习笔记四时钟系统本文简述了自己学习时钟系统的一些框架,参照风水月1. 单片机中时钟系统的理解1.1 概述时钟是单片机的脉搏,是单片机的驱动源用任何一个外设都必须打开相应的时钟不使

2021-08-12 08:06:09

一、综述: 1、时钟源在 STM32 中,一共有 5 个时钟源,分别是 HSI 、 HSE 、 LSI 、 LSE 、 PLL 。①HSI 是高速内部时钟, RC 振荡器,频率为 8MHz

2021-08-18 07:56:26

—————————————————————————————————————————————————————————在STM32中,有五个时钟源,为HSI、HSE、LSI、LSE、PLL。 其实是四个时钟源,如下图所示(灰蓝色),PLL是由锁相环电路倍频得到PLL时钟

2021-08-23 07:54:07

一、在STM32中,有五个时钟源,为HSI、HSE、LSI、LSE、PLL。①HSI是高速内部时钟,RC振荡器,频率为8MHz。②HSE是高速外部时钟,可接石英/陶瓷谐振器,或者接外部时钟源,频率

2021-08-06 09:01:16

的协议会定义特殊的码型(常见的码型如8B/10B编码中的K28.5)用于字对齐处理。另一些带源同步时钟的LVDS接口,通常会利用低频的源同步时钟来携带字对齐信息,用于接收端的正确恢复。FPGA对上述两种

2019-07-29 07:03:50

如何利用大功率数字源表构建多源测量单元系统?

2021-05-14 06:11:56

在串行数据传输的过程中,如何在FPGA中利用低频源同步时钟实现LVDS接收字对齐呢?

2021-04-08 06:39:42

我最初在错误的论坛上发布了这个,我无法编辑它 - 可能是因为我太新了。如果你再看到这个,我道歉。大家好 - 我有一个设计,我需要读取源同步DDR数据与500MHz时钟,所以1GHz比特率。时钟到达

2020-08-14 08:46:30

【追踪嫌犯的利器】定位技术原理解析(4)

2020-05-04 12:20:20

微波作为无线和传输设备的重要接入设备,在网络设计和使用中要针对接入业务的类型,提供满足其需求的时钟同步方案。当前阶段,微波主要支持的时钟同步类型包括:GPS,BITS,1588,1588

2019-07-12 07:46:39

我对使用源同步时钟将大量数据从一个FPGA移动到另一个FPGA感兴趣。但由于设计的性质,我没有很多可用的PLL,因此我无法发送许多时钟数据对。假设所有迹线具有相同的延迟,是否可以将一个源同步时钟与多个数据线相关联?非常感谢你

2020-08-07 09:14:30

本篇文章为永磁同步电机谐波电流注入控制策略原理解析及仿真教程目前关于此方向的资源教程较少,我个人对其进行了原理总结,仿真实验分析希望大家有所收获,喜欢本篇文章的话点个关注收藏赞吧!!!!!!永磁

2021-06-30 06:16:44

大家好,又到了每日学习的时候了。今天我们来聊一聊异步电路中的时钟同步处理方法。既然说到了时钟的同步处理,那么什么是时钟的同步处理?那首先我们就来了解一下。时钟是数字电路中所有信号的参考,没有时钟或者

2018-02-09 11:21:12

高速互联链路中参考时钟的抖动分析与测量

在高速互联链路中,发送器的参考工作时钟的抖动是影响整个

2010-04-15 14:01:39 19

19 使用时钟PLL的源同步系统时序分析一)回顾源同步时序计算Setup Margin = Min Clock Etch Delay – Max Data Etch Delay – Max Delay

2010-10-05 09:47:48 31

31 同步模块是每个系统的心脏,它为系统中的其他每个模块馈送正确的时钟信号。因此需要对同步模块的设计和实现给予特别关注。本文对影响系统设计的时钟特性进行了考察,

2006-03-11 13:21:00 2291

2291

分布式数据采集系统中的时钟同步

在高速数据传输的分布式数据采集系统中,各个组成单元间的时钟同步是保证系统正常工作的关键。由于系统工作于局

2009-03-29 15:10:53 2241

2241

华为NodeB采用的同步方式,失去同步源后可以保持的时间

WCDMA基站之间是不需要同步的。系统时钟的时钟源有GPS、BITS、Iub接口(从RNC来的时

2009-06-30 09:43:10 1963

1963 基于FPGA的提取位同步时钟DPLL设计

在数字通信系统中,同步技术是非常重要的,而位同步是最基本的同步。位同步时钟信号不仅用于监测输入码元信号,确保收发

2010-01-25 09:36:18 3699

3699

同步网时钟及等级

基准时钟 同步网由各节点时钟和传递同步定时信号的同步链路构成.同步网的功能是准确地将同步定时信号从基

2010-04-03 16:27:34 4060

4060 摘要:在对时间同步及网络延时进行分析的基础上,对RBS、TPSN、DMTS、连续时钟同步协议等主要的无传感网络的时钟同步协议进行了论述,并对其协议特点及适用范围进行了比较和分析. 关键词:无线传感网络 时钟同步 数据融合

2011-02-08 11:17:15 43

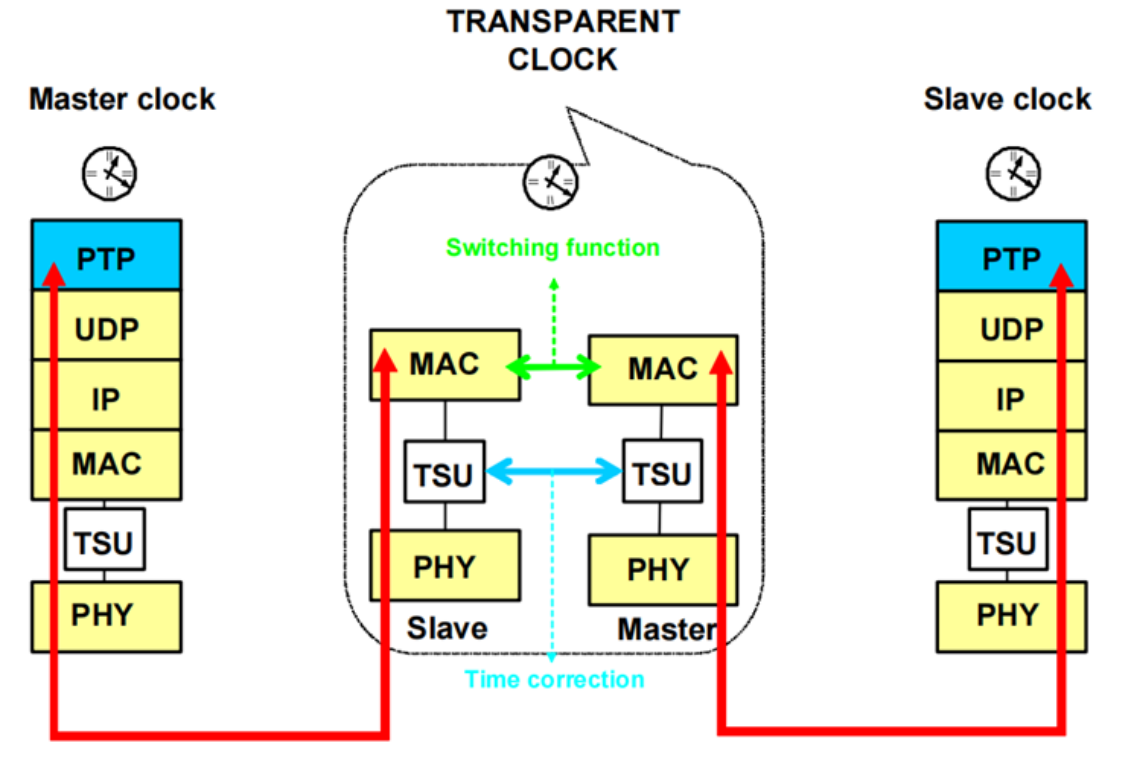

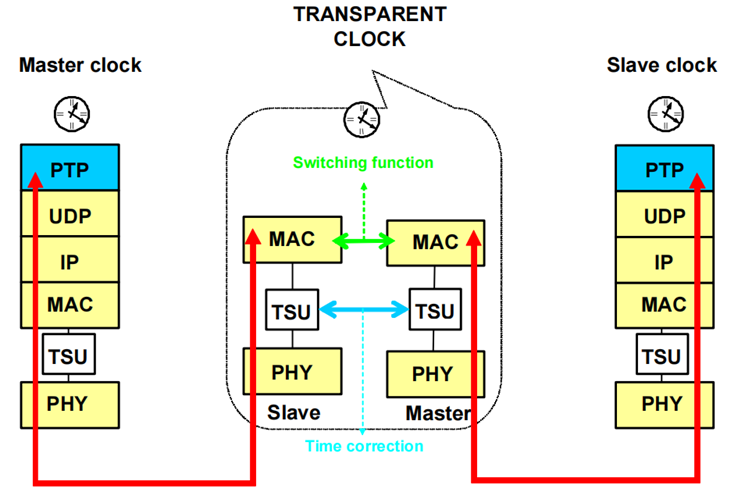

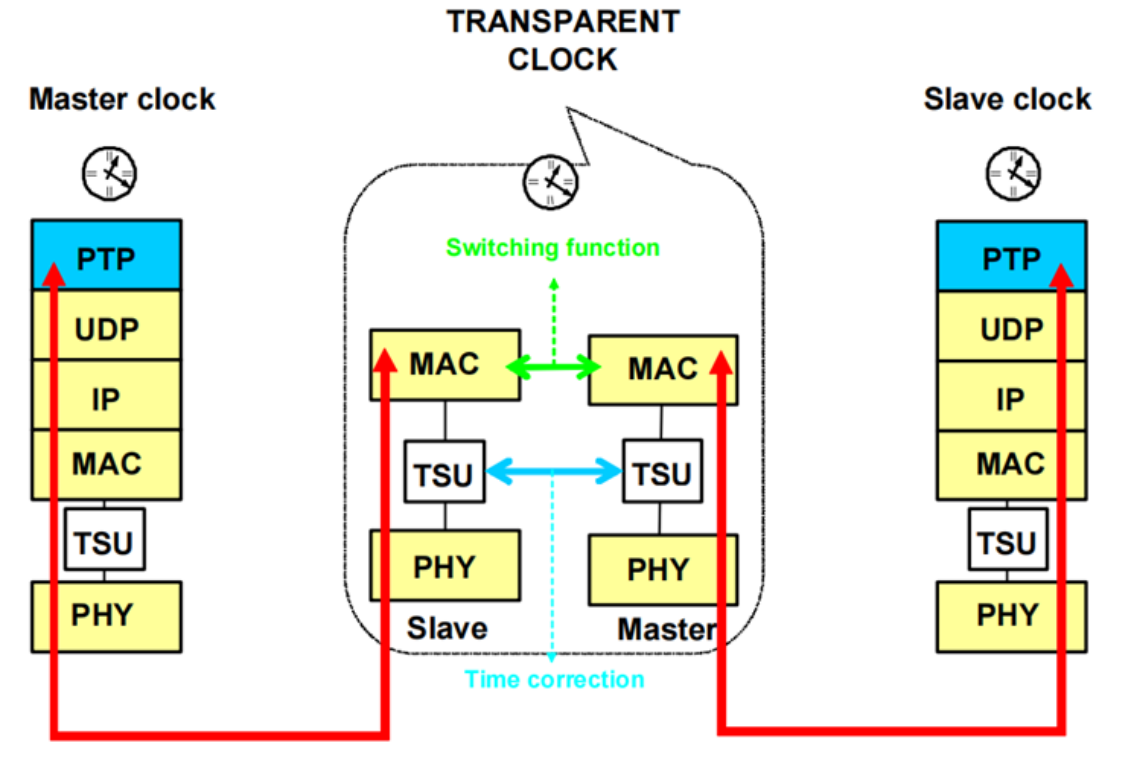

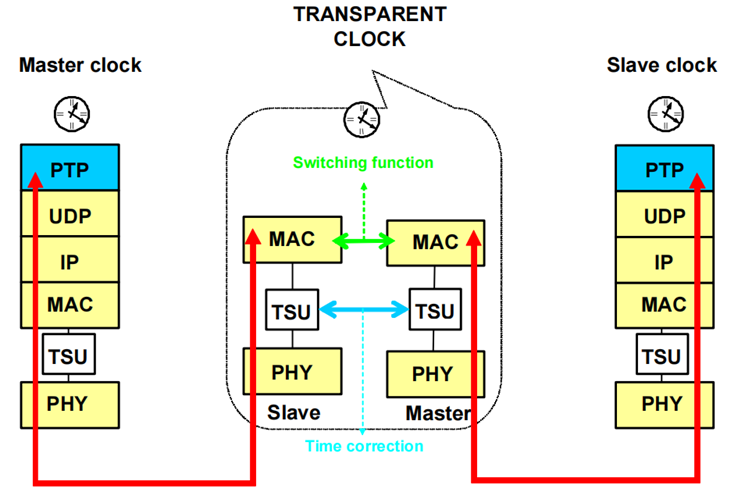

43 详细分析了IEEE1588时钟同步的基本原理,介绍了阿尔卡特朗讯TSS-5产品中实现IEEE1588时钟同步系统的方案,给出具体的硬件架构框图以及系统功能框图,最后列出TSS-5网元在实验室做的时

2012-05-30 14:55:49 46

46 各个设备之间时间的一致性和准确性,系统中配备时钟源进行授时,同步时钟卡从时钟源获取高精度的时间,使系统中各个设备与主机时钟源保持高精度的同步。同步时钟卡采用PCI-E总线的方式,PCI-E总线具有点对点串行互联,双通道、

2017-10-30 13:25:17 2

2 介绍了精密时钟同步协议(PTP)的原理。本文精简了该协议,设计并实现了一种低成本、高精度的时钟同步系统方案。该方案中,本地时钟单元、时钟协议模块、发送缓冲、接收缓冲以及系统打时标等功能都在FPGA中

2017-11-17 15:57:18 8779

8779

STM32中有一个全速功能的USB模块,其串行接口引擎需要一个频率为48MHz的时钟源。该时钟源只能从PLL输出端获取,可以选择为1.5分频或者1分频,也就是,当需要使用USB模块时,PLL必须使能,并且时钟频率配置为48MHz或72MHz。

2017-11-30 09:14:18 8325

8325

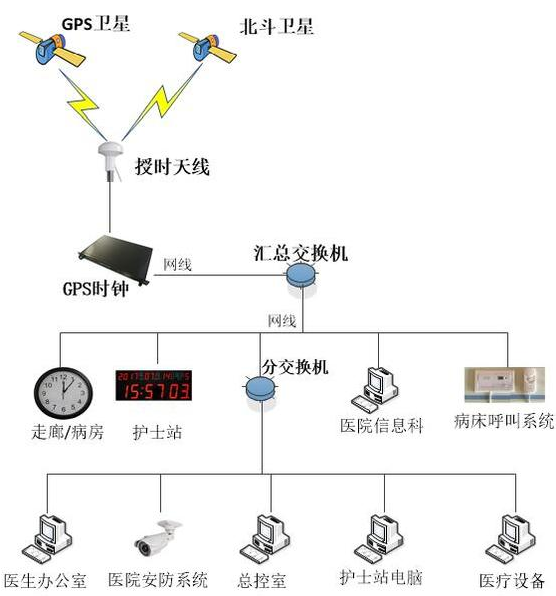

本文致力于解决系统时钟高精度和高稳定度的问题。通过UM220IIIN双系统接收机和FPGA的结合,输出北斗/GPS中精度最高的秒脉冲作为时钟源,若两者的秒脉冲都失效,就利用FPGA来预测下一时刻的秒

2017-12-05 17:26:20 9

9 微波作为无线和传输设备的重要接入设备,在网络设计和使用中要针对接入业务的类型,提供满足其需求的时钟同步方案。当前阶段,微波主要支持的时钟同步类型包括:GPS,BITS,1588,1588

2017-12-07 20:51:01 1085

1085 现在的硬件设计中,大量的时钟之间彼此相互连接是很典型的现象。为了保证Vivado优化到关键路径,我们必须要理解时钟之间是如何相互作用,也就是同步和异步时钟之间是如何联系。 同步时钟是彼此联系的时钟。

2018-05-12 10:15:00 20927

20927 大家好,又到了每日学习的时候了。今天我们来聊一聊异步电路中的时钟同步处理方法。 既然说到了时钟的同步处理,那么什么是时钟的同步处理?那首先我们就来了解一下。 时钟是数字电路中所有信号的参考,没有时钟

2018-05-21 14:56:55 13596

13596

我们系统中,主板与从板之间通过交换网片的HW0、HW4互连,要使主板与从板的交换网之间能够正常交换,必须使这两个交换网片有一致的帧同步时钟及位同步时钟。在现在的单板中,从板的时钟由主板直接送出。整个系统采用的时钟源有3种方式:

2018-10-30 11:36:23 7

7 1. STM32的5个时钟源

a。高速内部时钟 HSI,大约为8MHz

b。高速外部时钟 HSE,晶振取值范围在4M--16M,一般采用8M晶振

c。低速外部时钟 LSE

2018-11-14 16:30:25 25387

25387 无论是单片机还是微处理器,它们的核心都是大规模的时序逻辑电路,而驱动时序逻辑电路的动力则是准确而稳定的时钟源——不要小看定语“准确而稳定”哦,实际上人类的科技之所以能如此稳定、高速的发展,就是离不开准确而稳定的时钟源。比如单片机所使用的晶体振荡器,就是一种比较准确的时钟源。

2019-07-24 17:36:00 0

0 针对普通时钟系统存在着限制时钟频率的弊端,人们设计了一种新的时序系统,称之为源同步时序系统。它最大的优点就是大大提升了总线的速度,在理论上信号的传送可以不受传输延迟的影响。

2019-12-20 07:09:00 5228

5228

STM32的SysTick时钟源来自哪里?

2020-03-03 14:32:55 8718

8718 GPS时钟源是在GPS卫星定位授时模块开发的基础上新研发的授时应用产品。能够按照用户需求输出符合规约的时间信息格式,从而完成同步授时服务。

2020-11-12 15:09:05 2404

2404

同步接口设计特别有用。7系列器件中的I/O Bank与时钟区域的大小相同。为了理解区域时钟是如何工作的,理解区域时钟信号的信号路径是很重要的。7系列设备中的区域时钟资源和网络由以下路径和组件组成: 时钟输入I/O I/O时钟缓冲器:BUFIO 区域时

2021-03-22 09:47:30 6215

6215

时钟信号好比是单片机的脉搏,了解STM32时钟系统很有必要。下图是STM32F1xx用户手册中的时钟系统结构图。 在STM32F1xx中,有五个时钟源,分别为HSI、HSE、LSI、LSE、PLL

2021-05-25 11:17:46 25482

25482

在UWB定位系统中,TDOA定位算法那的优势明显。我们知道TDOA算法中需要测量UWB信号的到达时间差。如果说TDOA定位的前提是需要测量到达时间差,那么测量到达时间差的前提就是时间需要同步一致

2021-09-26 15:14:44 11189

11189 GPS北斗同步时钟是主要以卫星为基准作为标准时间源的专用对时装置。本文主要结合GPS北斗同步时钟在电厂,变电站等类似场合的成功使用案例,简单阐述了GPS北斗同步时钟在电力系统的应用。电力系统的时钟

2021-12-17 18:26:57 13

13 异步复位,同步释放的理解目录目录 同步复位和异步复位 异步复位 同步复位 那么同步复位和异步复位到底孰优孰劣呢? 异步复位、同步释放 问题1 问题2 问题3 问题4 问题5 参考资料同步

2022-01-17 12:53:57 4

4 在电气测量中,同步是精确匹配测量数据的过程,以便从基本相同的时刻开始。当有来自不同位置和不同时间间隔的数据以及在不同时间范围内测量的数据时,需要同步。LMG600定义了三种不同级别的同步:通道、仪器

2022-09-27 15:18:59 3064

3064

针对普通时钟系统存在着限制时钟频率的弊端,人们设计了一种新的时序系统,称之为源同步时序系统。它最大的优点就是大大提升了总线的速度,在理论上信号的传送可以不受传输延迟的影响。下面我们来看看这种源同步时钟系统的结构。

2022-12-26 17:04:55 1648

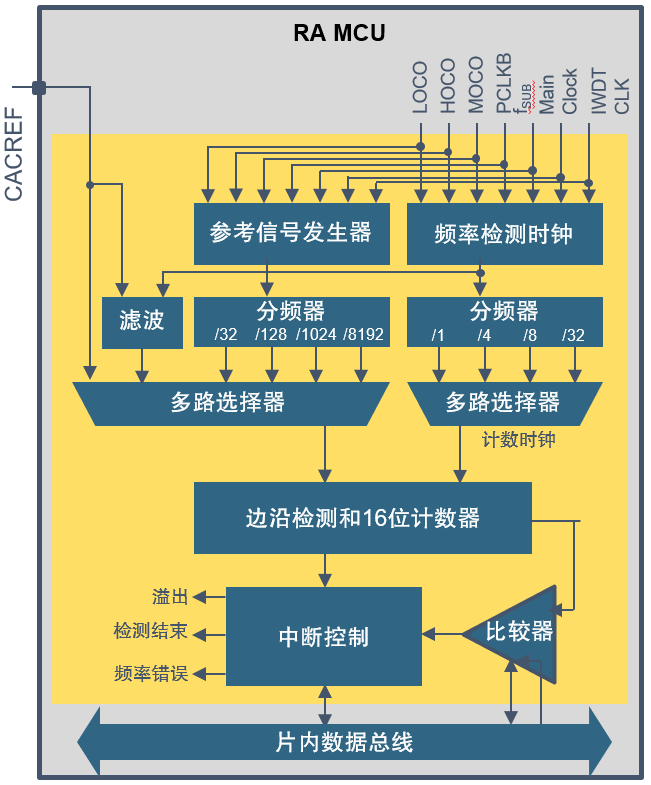

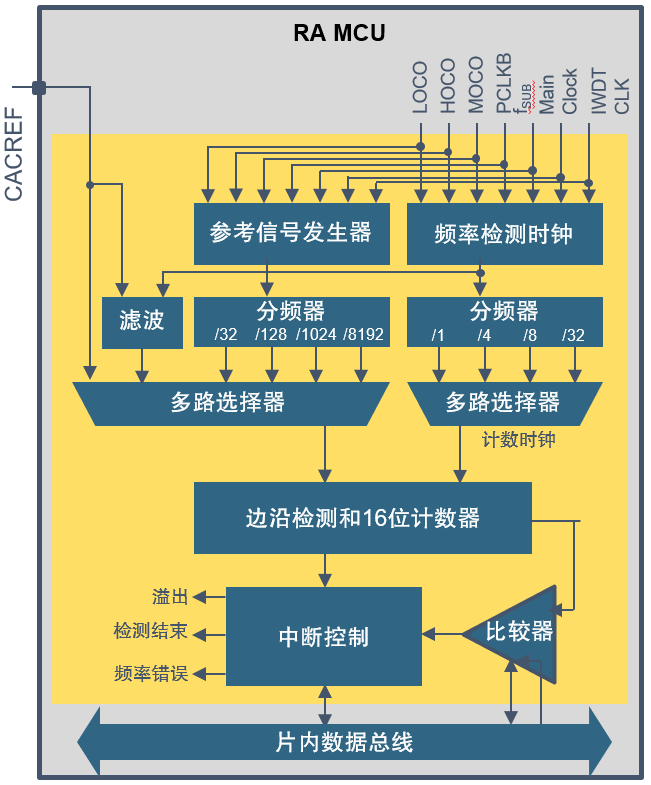

1648 本篇文章我们将向您介绍RA微控制器系列中一个不太常见和不太容易理解的外设,即时钟频率精度测量电路(CAC)。时钟频率精度测量电路旨在使我们能够通过将RA微控制器上可用的许多内部和外部时钟源相互对比,检查它们的精度,并在比较结果出现意外偏差时指示出来。

2023-08-08 02:54:30 1225

1225

使用HSE时钟源对LSE精度进行测量

2023-09-19 16:43:33 1710

1710

时钟信号的同步 在数字电路里怎样让两个不同步的时钟信号同步? 在数字电路中,时钟信号的同步是非常重要的问题。因为在信号处理过程中,如果不同步,就会出现信号的混淆和错误。因此,在数字电路中需要采取一些

2023-10-18 15:23:48 2931

2931 丢失。 为了实现FPGA和DSP的同步时钟频率,可以采用以下两种方式: 1. 外部时钟源同步 通过引入外部时钟源,让FPGA和DSP的时钟信号由同一个时钟源提供,以此保证两者的时钟频率保持同步。在这种情况下,需要将时钟源的频率设置为两者的最大频率。 2. PLL同步 如

2023-10-18 15:28:13 2793

2793 电子发烧友网站提供《IEEE1588时钟同步在PTN网中的实现.pdf》资料免费下载

2023-10-24 09:39:34 0

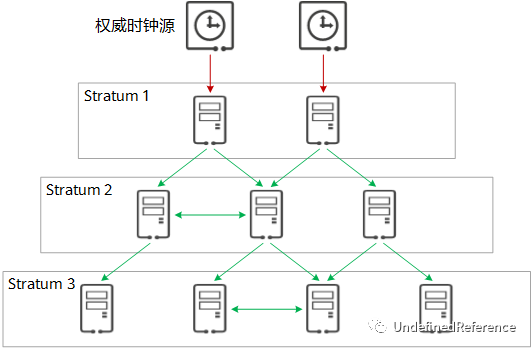

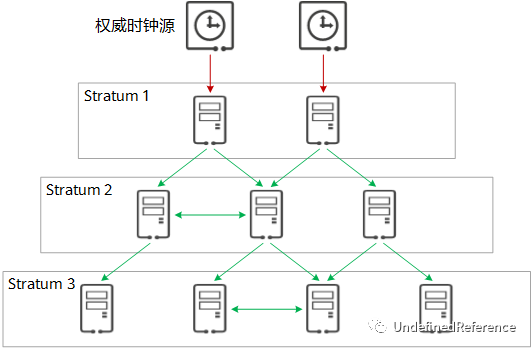

0 NTP ntp时钟层级 ntp允许客户端从服务器请求和接收时间,而服务器又从权威时钟源(例如原子钟、GPS)接收精确的协调世界时UTC。 ntp以层级来组织模型结构,层级中的每层被称为Stratum

2023-10-27 14:14:49 3828

3828

在电子测量领域,普源示波器是一种关键的工具,用于捕捉和分析电子信号的波形。在测量过程中,确保准确的相位校正至关重要,以保证获得准确可靠的测量结果。本文将探讨普源示波器相位校正的重要性,并提供一些

2024-01-09 17:47:46 1297

1297

异步电路中的时钟同步处理方法 时钟同步在异步电路中是至关重要的,它确保了电路中的各个部件在正确的时间进行操作,从而使系统能够正常工作。在本文中,我将介绍一些常见的时钟同步处理方法。 1. 时钟分配

2024-01-16 14:42:44 2200

2200 如何生成关于时钟同步功能的DTC? 时钟同步功能是指在一个系统内的多个时钟源进行同步,确保它们的时间保持一致。这在许多实时系统中都非常重要,特别是在需要多个设备或组件协同工作的场景中。若时钟同步

2024-01-16 15:10:08 1222

1222 时钟同步怎样组网? 时钟同步是计算机网络中的重要问题,主要用于确保在多个节点之间保持时间的一致性。时钟同步对于网络的可靠性和性能至关重要,因此组网时时钟同步必须仔细考虑。 在计算机网络中,各个节点

2024-01-16 15:10:13 1357

1357 网络时钟同步有哪些要求?要注意哪些问题?如何在5G网络中测试时间与时钟同步? 网络时钟同步是指在计算机网络中,各个时钟节点之间通过协议和算法进行时间的同步,以确保网络中的各个设备拥有相近的时间,从而

2024-01-16 16:03:25 2667

2667 在现代通信技术中,精确时间同步对于保障网络性能至关重要。PTP(PrecisionTimeProtocol)时钟源设备作为实现高精度时间同步的关键组件,其配置和选择对于网络架构师和工程师来说至关重要

2024-02-22 08:04:14 2701

2701

在现代通信技术中,精确时间同步对于保障网络性能至关重要。PTP(Precision Time Protocol)时钟源设备作为实现高精度时间同步的关键组件,其配置和选择对于网络架构师和工程师来说

2024-02-22 16:12:02 1464

1464

导读:在现代通信技术中,精确时间同步对于保障网络性能至关重要。PTP(Precision Time Protocol)时钟源设备作为实现高精度时间同步的关键组件,其配置和选择对于网络架构师和工程师

2024-02-26 16:19:14 1387

1387

天线是时钟同步系统中至关重要的组成部分,其故障可能会导致时间同步精度下降或无法正常工作。故障原因可能包括天线损坏、连接线松动等。 时间同步精度不够 时钟同步系统的精度直接影响着整个系统的运行效果,时间同步精度不够可能导致

2024-03-19 10:42:27 3661

3661

微控制器依赖于其时钟源。处理器、总线和外围设备都使用时钟来同步它们的操作。

2024-04-15 14:17:03 1884

1884 安徽京准-时间源服务器(NTP网络时钟源)在医疗中的重要性

2024-06-11 10:14:23 873

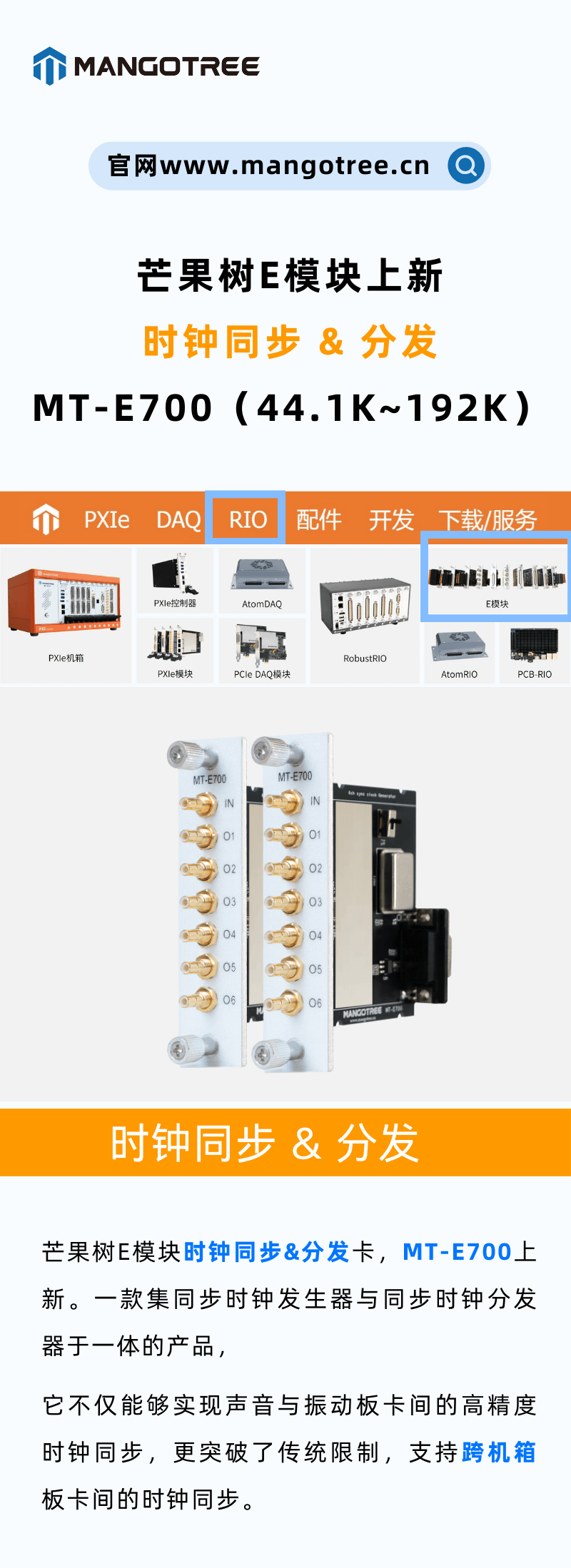

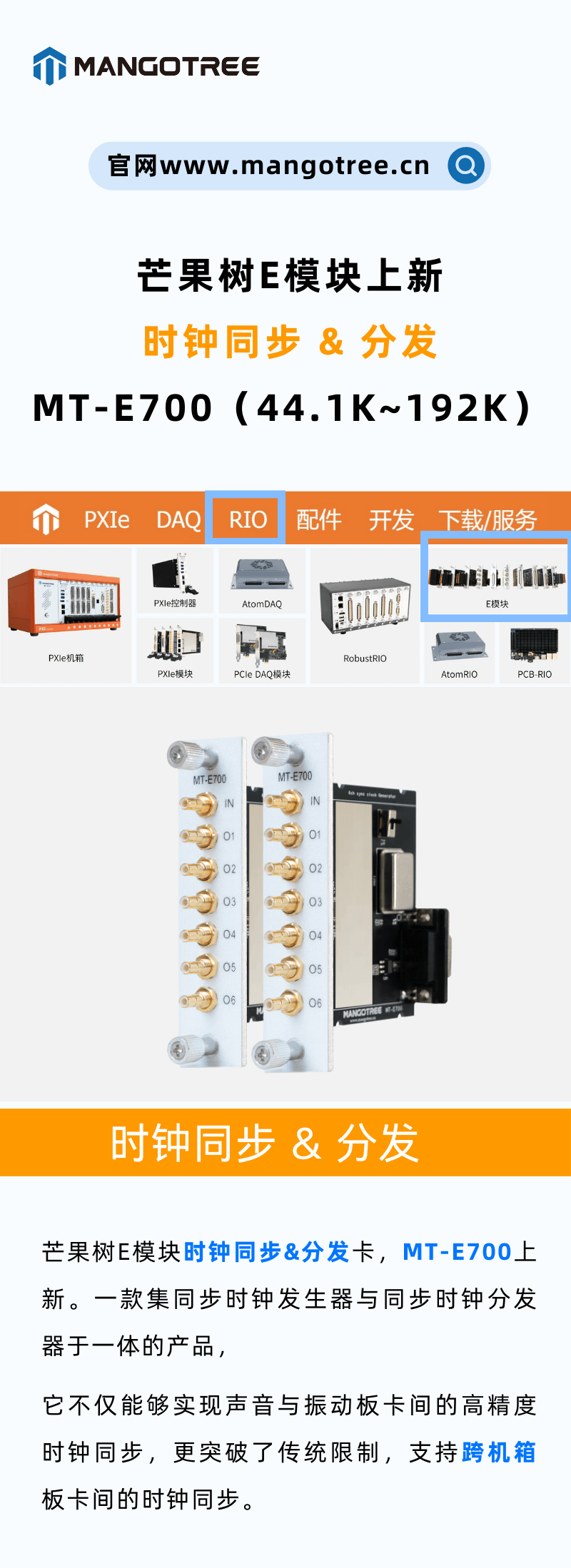

873 同步时钟发生器 + 同步时钟分发器

2024-09-14 15:00:54 669

669

一、引言 在现代网络通信领域,时钟同步精度至关重要,时间敏感网络(TSN)作为新一代工业通信的核心技术,其时钟同步精度直接影响数据传输的实时性与系统协同效率。尤其在工业自动化、车载网络等高精度场景中

2025-04-25 09:56:05 1065

1065

时钟同步是指在一个系统中,各个时钟能够准确地显示相同的时间。在现代科技发展中,时钟同步是非常重要的,特别是在计算机网络和通信系统中。在计算机网络中,时钟同步对于确保数据的传输和处理是至关重要的。网络

2025-04-29 13:44:31 989

989

一、功率分析仪同步源的作用 同步源是功率分析仪进行正确傅里叶变换的前提,选择合理的 功率分析仪同步源 ,可提高傅里叶变换的有效性和准确度。 电机为感性负载,采用变频器供电时,其电流信号的谐波含量远远

2025-05-19 10:13:09 564

564 横河功率分析仪的通用运算原理则是首先检测出指定信号的周期,并将检测周期的整数倍时间设为测量区间,随后对这段时间内采集到的数据进行平均运算,这一测量方式也被称为“同步源周期平均法”,其中用于定义测量周期的输入信号被称为同步源。

2025-06-30 15:30:21 909

909

电子发烧友App

电子发烧友App

评论