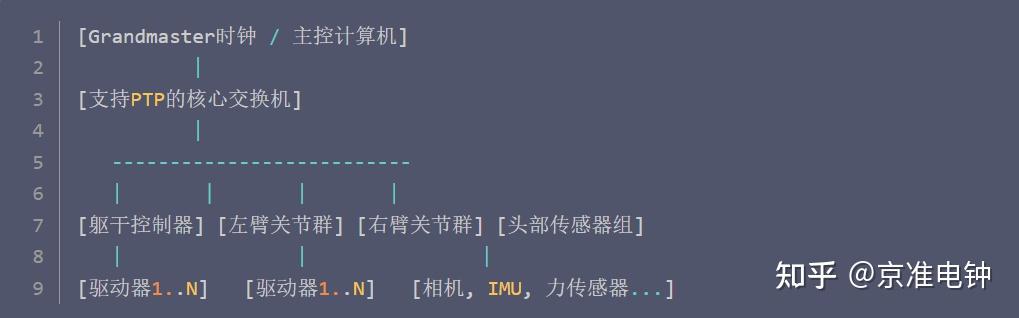

导读:在现代通信技术中,精确时间同步对于保障网络性能至关重要。PTP(Precision Time Protocol)时钟源设备作为实现高精度时间同步的关键组件,其配置和选择对于网络架构师和工程师来说至关重要。本文将探讨普通时钟和透明时钟的特性及配置策略,以助您更好地理解和应用PTP时钟源设备,确保通信网络的高效稳定运行。

普通时钟

普通时钟指的是具有单个PTP端口的PTP时钟,它作为PTP网络中的一个节点运行,并且可以根据BCM算法在一个网段内选择作为主节点或从节点。 普通时钟是PTP网络中最常见的设备,因为它们通常用作网络中的终端节点,连接到需要同步的设备。

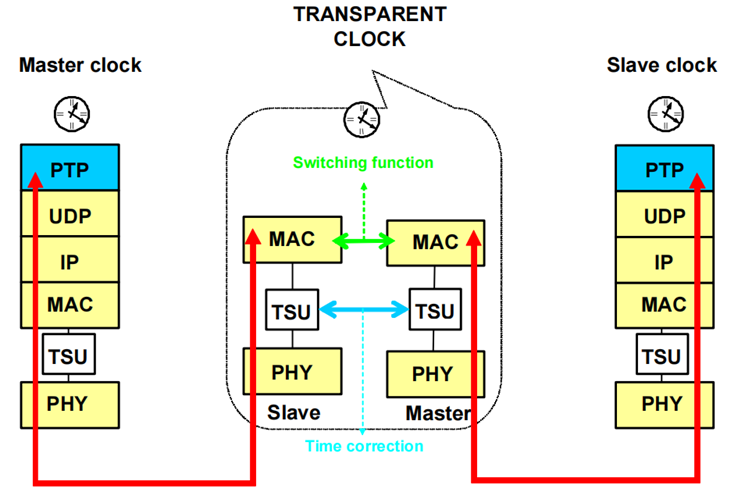

透明时钟

透明时钟在IEEE 1588标准的第二版中得到了引入,作为优化级联拓扑结构的一种创新方法。与边界时钟不同,透明时钟并不扮演多端口普通时钟的角色,而是负责更新PTP事件消息中新引入的时间间隔字段。这一64位时间间隔校正字段的引入,使得交换延迟能够被补偿至小于1皮秒的潜在精度,从而显著提升了时间同步的精确性。

PTP时钟源配置

虹科RELY-RB以两种方式支持IEEE1588v2功能:普通时钟(OC)和透明时钟(TC)。 两者都可以使用Web管理器进行配置。

虹科RELY-RB

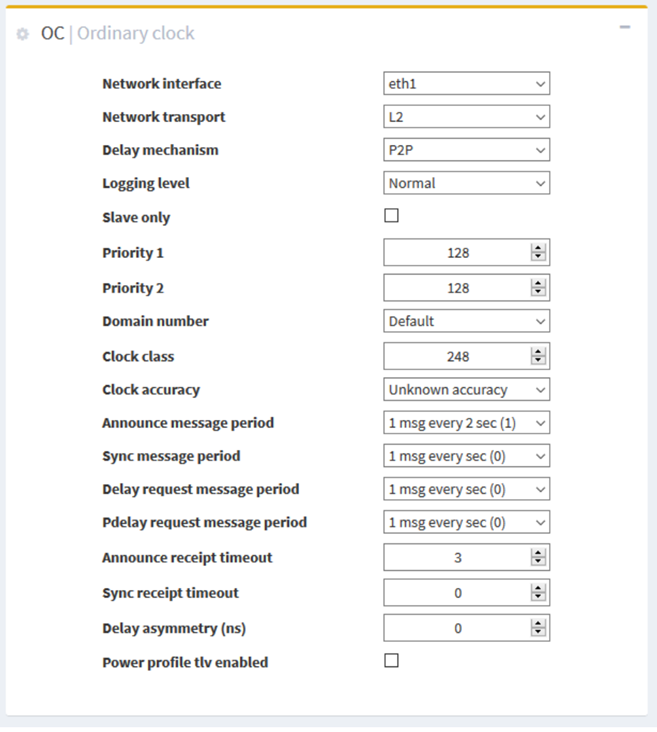

在普通时钟(OC)部分,可以在Web管理器配置以下字段:

• Network interface.选择OC将在哪些可用网络接口上运行。

• Network transport.选择第2层以太网或UDP/IPv4传输层。

• Delay mechanism.在P2P或E2E延迟机制之间进行选择。

• Logging level. PTP堆栈报告的消息的详细信息。

• Slave only.选中此复选框以强制设备充当从时钟设备。

• Priority 1.生成的Announce消息的PTP优先级1。

• Priority 2.生成的Announce消息的PTP优先级2。

• Domain number. PTP域号。

• Clock class.定义时钟的精度级别。

• Clock accuracy.生成的Announce消息的PTP时钟精度。

• Announce message period. Announce消息的期限。

• Sync message period.同步消息的周期。

• Delay request message period.延迟消息的周期。

• Pdelay request message period. Pdelay消息的周期。

•Announce receipt timeout.没有收到Announce报文的数目,用来判断Announce报文超时。

• Sync receipt timeout.没有收到sync/follow报文的数目,用于gPTP模式判断Sync是否超时,是否触发best master clock选择。

• Delay asymmetry (ns).使用此参数校准源自不对称的固定偏移。

• Power profile tlv enabled. Power Profile Master必须将TLV附加到 Announce消息。

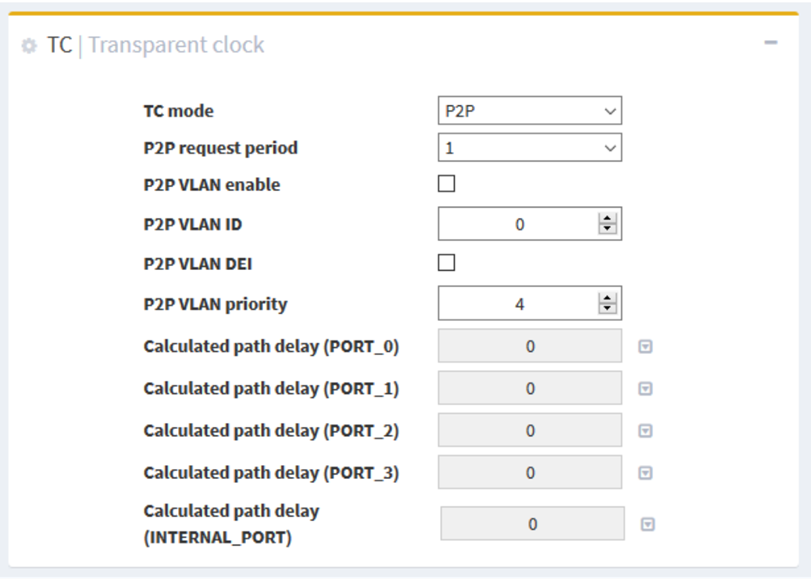

在透明时钟(TC)部分,可以在Web管理器配置以下字段:

• TC mode. TC可以工作在端到端(E2E)或对等(P2P)模式。

• P2P request period(仅在 P2P模式下)。 每秒延迟请求消息(1、2、4或8)。

• P2P VLAN enable.在 P2P消息中包含 VLAN标记。

• P2P VLAN ID. P2P消息中的 VLAN ID。

• P2P VLAN DEI.丢弃 P2P消息的 VLAN标记中的 Eligible位。

• P2P VLAN priority. P2P消息的 VLAN标记中的优先级。

• Calculated path delay (port).基于 P2P机制自动计算延迟。

• Latencies.通过单击每个端口的计算路径延迟框旁边的箭头,将显示取决于 PHY速度的接收和发送延迟。 使用这些值来校准可能出现在路径延迟测量和由于不对称的透明时钟校正中的可能的固定偏移。

结语

通过对普通时钟和透明时钟的解析,我们不难发现,在PTP网络中,这两种时钟源设备各自扮演着不可或缺的角色。普通时钟作为网络中的常见节点,确保了终端设备的时间同步;而透明时钟则通过精确的路径延迟计算和校正,为级联拓扑提供了高效的解决方案。虹科RELY-RB作为支持IEEE1588v2功能的设备,其灵活的Web管理器配置方式为用户提供了便捷的操作体验。在实际应用中,根据网络架构和需求选择合适的时钟源设备,并正确配置其参数,是确保网络时间同步性能的关键。

审核编辑 黄宇

-

时钟源

+关注

关注

0文章

114浏览量

16834 -

PTP

+关注

关注

0文章

101浏览量

9808 -

TSN

+关注

关注

3文章

296浏览量

18072

发布评论请先 登录

多元化PTP主时钟设备都有哪些应用,ptp授时模块,ptp授时服务器

IDT ICS664 - 01数字视频时钟源:高清电视数字视频设备的时钟解决方案

RENESAS ICS664 - 02 PECL数字视频时钟源:高清电视时钟解决方案

虹科技术|PTP时钟源设备全攻略:从普通时钟到透明时钟的进阶之路

虹科技术|PTP时钟源设备全攻略:从普通时钟到透明时钟的进阶之路

评论