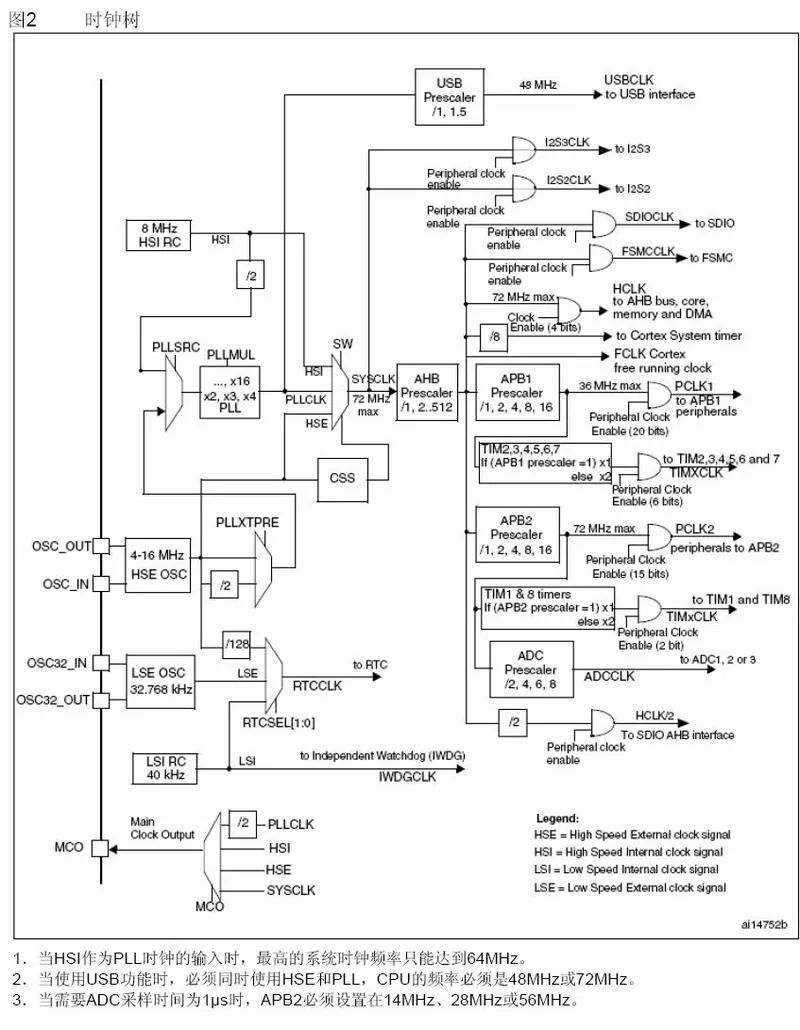

时钟信号好比是单片机的脉搏,了解STM32时钟系统很有必要。下图是STM32F1xx用户手册中的时钟系统结构图。

在STM32F1xx中,有五个时钟源,分别为HSI、HSE、LSI、LSE、PLL。

HSI是高速内部时钟,RC振荡器,频率为8MHz

HSE是高速外部时钟,可接石英/陶瓷谐振器或者接外部时钟源,频率范围为4MHz~16MHz

LSI是低速内部时钟,RC振荡器,频率为40kHz

LSE是低速外部时钟,接频率为32.768kHz的石英晶振

PLL为锁相环倍频输出,其输出频率最大不得超过72MHz

SYSCLK系统时钟SYSCLK最大频率为72MHz,它是供STM32中绝大部分部件工作的时钟源。系统时钟可由PLL、HSI或者HSE提供输出,并且它通过AHB分频器分频后送给各模块使用。HCLKHCLK为高性能总线AHB(advanced high-performance bus)提供时钟信号。由系统时钟SYSCLK分频得到,一般不分频时等于系统时钟,是给外设使用的。

FCLK

FCLK(free running clock)是自由运行时钟,为CPU内核提供时钟信号。我们所说的CPU主频为xxHz,指的就是这个时钟信号频率,CPU时钟周期就是1/FCLK。“自由”表现在它不来自系统时钟HCLK,在系统时钟停止时FCLK也继续运行。FCLK用作采样中断或者为调试模块计时。在处理器休眠时,通过FCLK可以采样到中断和跟踪休眠事件。Cortex-M3内核的FCLK和HCLK互相同步、互相平衡,保证Cortex-M3的延迟相同。

原文标题:STM32时钟系统中的SysTick、FCLK、SYSCLK、PCLK和HCLK

文章出处:【微信公众号:MCU开发加油站】欢迎添加关注!文章转载请注明出处。

责任编辑:haq

-

STM32

+关注

关注

2313文章

11195浏览量

374643 -

时钟

+关注

关注

11文章

1999浏览量

135233

原文标题:STM32时钟系统中的SysTick、FCLK、SYSCLK、PCLK和HCLK

文章出处:【微信号:mcugeek,微信公众号:MCU开发加油站】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

ICS557 - 05A:PCI - Express Gen1时钟源的理想之选

STM32H7 的 3 个 ADC 时钟同步方法

IDT ICS664 - 01数字视频时钟源:高清电视数字视频设备的时钟解决方案

IDT ICS664 - 03数字视频时钟源:设计与应用详解

Renesas ICS660数字视频时钟源:设计与应用详解

探索 RENESAS ICS664 - 01 数字视频时钟源:特性、应用与设计要点

RENESAS ICS664 - 02 PECL数字视频时钟源:高清电视时钟解决方案

CW32系列微控制器的时钟源和定时器选项介绍

CW32 SysClk系统时钟的应用场景与切换规则

STM32系统中的五个时钟源介绍

STM32系统中的五个时钟源介绍

评论