在高速的PCB设计中,时钟等关键的高速信号线,走线需要进行屏蔽处理,如果没有屏蔽或只屏蔽了部分,都会造成EMI的泄漏。建议屏蔽线,每1000mil,打孔接地。##在高速的PCB设计中,时钟等关键

2016-04-26 14:00:01 5836

5836

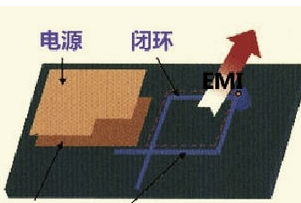

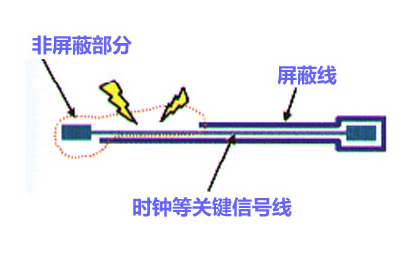

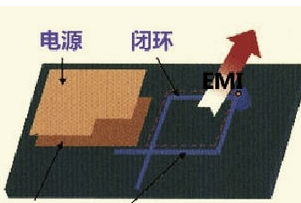

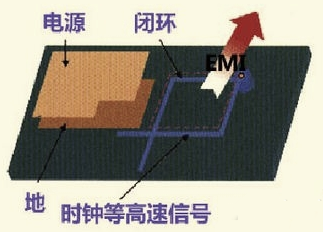

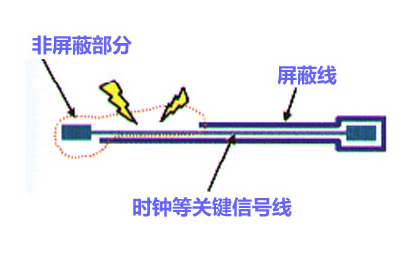

信号走线屏蔽规则 在高速的PCB设计中,时钟等关键的高速信号线,走线需要进行屏蔽处理,如果没有屏蔽或只屏蔽了部分,都会造成EMI的泄漏。建议屏蔽线,每1000mil,打孔接地。

2018-04-13 08:20:00 2201

2201

本文主要详解PCB设计高速模拟输入信号走线,首先介绍了PCB设计高速模拟输入信号走线方法,其次阐述了九大关于PCB设计高速模拟输入信号走线规则,具体的跟随小编一起来了解一下。

2018-05-25 09:06:44 10092

10092

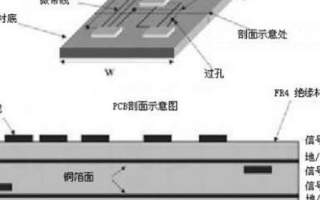

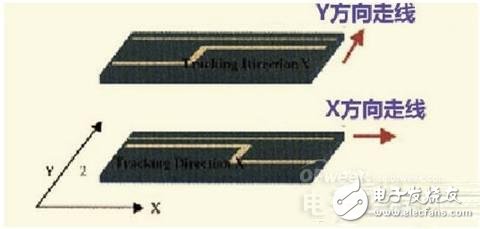

高速产品的轻薄化,PCB厚度限制了走线层数,就有了高速线走在相邻两层上,为了减少相互的串扰,走线的方法有间距管控(DDR部分实现难度比较大),垂直走线(这种方法实现难度比较大),30度角走线。

2022-07-13 15:53:27 4072

4072

一站式PCBA智造厂家今天为大家讲讲高速PCB设计中的屏蔽方法有哪些?高速PCB设计中的屏蔽方法高速PCB设计布线系统的传输速率随着时代的更迭也在不断加快,但这也给其带来了一个新的挑战——抗干扰能力

2023-08-08 10:19:06 1922

1922

PCB设计布线(Layout)的好坏将直接影响到整个系统的性能,大多数高速的设计理论也要最终经过 Layout 得以实现并验证,由此可见,布线在高速 PCB 设计中是至关重要的。下面将针对实际布线中可能遇到的一些情况,分析其合理性,并给出一些比较优化的走线策略。

2016-07-18 14:07:10 48837

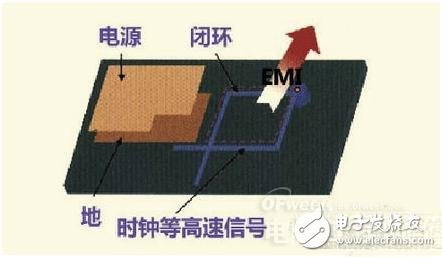

48837 规则一:高速信号走线屏蔽规则在高速的PCB设计中,时钟等关键的高速信号线,走线需要进行屏蔽处理,如果没有屏蔽或只屏蔽了部分,都会造成EMI的泄漏。建议屏蔽线,每1000mil,打孔接地。图1 高速

2018-11-28 11:14:18

布线(Layout)是PCB设计工程师最基本的工作技能之一。走线的好坏将直接影响到整个系统的性能,大多数高速的设计理论也要最终经过Layout得以实现并验证,由此可见,布线在高速PCB设计中

2014-08-13 15:44:05

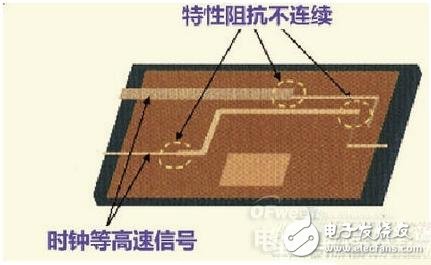

的设计理论也要最终经过 Layout得以实现并验证,由此可见,布线在高速PCB设计中是至关重要的。下面将针对实际布线中可能遇到的一些情况,分析其合理性,并给出一些比较优化的走线策略。主要从直角走线,差分走线

2017-07-07 11:45:56

布线(Layout)是PCB设计工程师最基本的工作技能之一。走线的好坏将直接影响到整个系统的性能,大多数高速的设计理论也要最终经过Layout得以实现并验证,由此可见,布线在高速PCB设计中

2019-08-05 06:40:24

PCB布线规则解析

铺设通电信号的道路以连接各个器件,即PCB布线。在PCB设计中,布线是完成产品设计的重要步骤。PCB布线有些规则相关知识,用此文来和大家分享一番:

走线的方向控制规则

在 PCB

2023-11-14 16:06:37

,它不仅完成了导通孔的作用,还省出许多布线通道使布线过程完成得更加方便,更加流畅,更为完善,PCB 板的设计过程是一个复杂而又简单的过程,要想很好地掌握它,还需广大电子工程设计人员去自已体会,才能得到其中的真谛。那么大家还知道PCB设计中,有哪些布线规则吗?掌握好规则是最重要的准备。

2019-08-01 08:04:25

@[TOC]PCB设计经验(1)#PCB设计规则#PCB走线经验#快捷键的使用#易犯错误汇总

2021-11-10 08:19:25

请问PCB设计规则怎样设置?怎样设置PCB的电气规则检查?比如说线宽,焊盘间的距离,线与线之间的间距,焊盘与线之间的间距怎样定义设置?

2016-08-13 16:57:56

PCB设计走线的规则是什么

2021-03-17 06:36:28

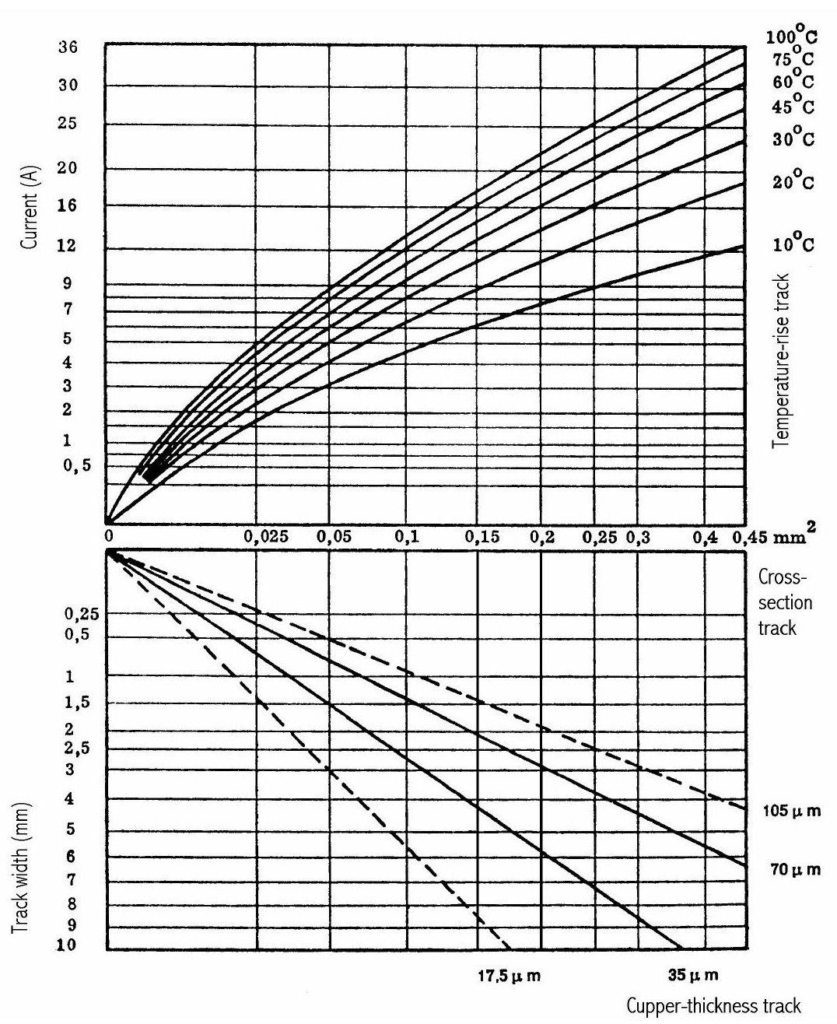

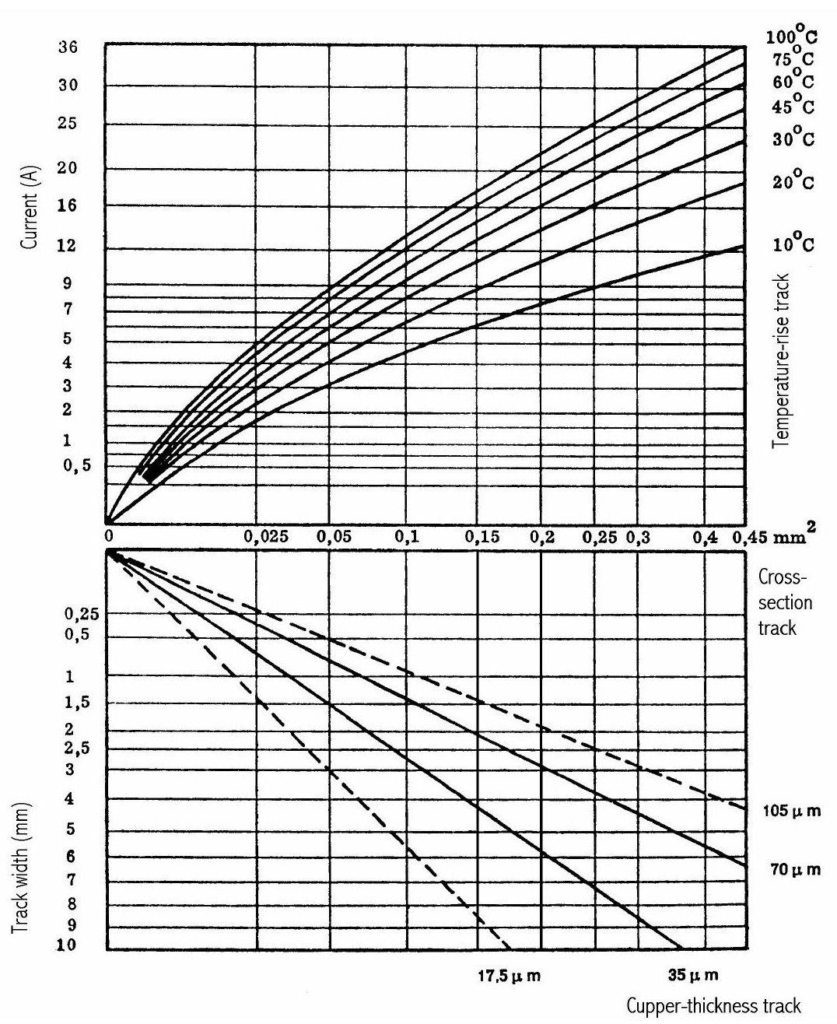

PCB设计走线的宽度与最大允许电流有何关系?PCB设计走线的宽度与铜厚有何关系?

2021-10-11 09:49:14

减少布线层,降低PCB成本。 当然,这样做的代价是冒一些技术风险,甚至牺牲一半成功率。 对于背板的层叠设计,鉴于常见背板很难做到相邻走线互相垂直,不可避免地出现平面长距离布线。 对于高速背板

2023-04-12 15:12:13

电容,反射,EMI等效应在TDR测试中几乎体现不出来,高速PCB设计工程师的重点还是应该放在布局,电源/地设计,走线设计,过孔等其他方面。当然,尽管直角走线带来的影响不是很严重,但并不是说我们以后都可以

2018-09-17 17:31:52

高速PCB信号走线的九条规则.pdf(220.78 KB)

2019-09-16 07:26:43

设计,一些心得和大家交流、交流。规则一、高速信号走线屏蔽规则如上图所示:在高速的PCB设计中,时钟等关键的高速信号线,走线需要进行屏蔽处理,如果没有屏蔽或只屏蔽了部分,都是会造成EMI的泄漏。建议屏蔽线

2021-03-31 06:00:00

通过高速PCB来控制解决。做了4年的EMI设计,一些心得和大家交流、交流。规则一、高速信号走线屏蔽规则 如上图所示:在高速的PCB设计中,时钟等关键的高速信号线,走线需要进行屏蔽处理,如果没有屏蔽或只

2022-04-18 15:22:08

我们定义了传输线效应发生的前提条件,但是如何得知线延时是否大于1/2驱动端的信号上升时间? 一般地,信号上升时间的典型值可通过器件手册给出,而信号的传播时间在PCB设计中由实际布线长度决定。下图为信号

2015-05-05 09:30:27

高速PCB设计布线系统的传输速率在稳步加快的同时也带来了某种防干扰的脆弱性,这是因为传输信息的频率越高,信号的敏感性增加,同时它们的能量越来越弱,此时的布线系统就越容易受干扰。 干扰无处不在,电缆

2018-11-28 17:00:27

高速PCB设计布线系统的传输速率在稳步加快的同时也带来了某种防干扰的脆弱性,这是因为传输信息的频率越高,信号的敏感性增加,同时它们的能量越来越弱,此时的布线系统就越容易受干扰。干扰无处不在,电缆

2019-07-17 18:55:38

高速PCB设计布线系统的传输速率在稳步加快的同时也带来了某种防干扰的脆弱性,这是因为传输信息的频率越高,信号的敏感性增加,同时它们的能量越来越弱,此时的布线系统就越容易受干扰。干扰无处不在,电缆

2016-09-14 11:03:51

高速PCB设计布线系统的传输速率在稳步加快的同时也带来了某种防干扰的脆弱性,这是因为传输信息的频率越高,信号的敏感性增加,同时它们的能量越来越弱,此时的布线系统就越容易受干扰。干扰无处不在,电缆

2016-09-21 10:25:21

`请问高速PCB设计规则有哪些?`

2020-02-25 16:07:38

。 问:在高速PCB设计中,串扰与信号线的速率、走线的方向等有什么关系?需要注意哪些设计指标来避免出现串扰等问题? 答:串扰会影响边沿速率,一般来说,一组总线传输方向相同时,串扰因素会使边沿速率变慢

2019-01-11 10:55:05

规则一:高速信号走线屏蔽规则 在高速的PCB设计中,时钟等关键的高速信号线,走线需要进行屏蔽处理,如果没有屏蔽或只屏蔽了部分,都会造成EMI的泄漏。建议屏蔽线,每1000mil,打孔接地

2016-01-19 22:50:31

。 而绝对的要求是控制两个器件之间的走线延迟为某一个值,比如器件A、B之间的延迟为Ins,而这样的要求往往由高速电路设计者提出,而由PCB工程师去实现。要满足这个要求,就必须知道信号的传播速度c但需要

2018-11-27 15:22:54

、高速信号走线屏蔽规则如上图所示:在高速的PCB设计中,时钟等关键的高速信号线,则需要进行屏蔽处理,如果没有屏蔽或只屏蔽了部分,都是会造成EMI的泄漏。建议屏蔽线,每1000mil,打孔接地。2...

2021-12-31 06:22:08

PCB Layout中的走线策略布线(Layout)是PCB设计工程师最基本的工作技能之一。走线的好坏将直接影响到整个系统的性能,大多数高速的设计理论也要最终经过Layout得以实现并验证,由此可见

2009-08-20 20:58:49

一线工程师整理的PCB设计技巧,包含高速,混合信号和低电平应用,例举众多实例说明。工程师们绝对福利~PCB设计是一门艺术,好的PCB设计需要花费数十年的时间才能不断磨砺而成。设计一个可靠的高速,混合

2017-07-26 17:37:44

图解在高速的PCB设计中的走线规则

2021-03-17 07:53:30

的进行干扰抑制呢?规则一:高速信号走线屏蔽规则在高速的PCB设计中,时钟等关键的高速信号线,走线需要进行屏蔽处理,如果没有屏蔽或只屏蔽了部分,都会造成EMI的泄漏。建议屏蔽线,每1000mil,打孔

2016-07-07 15:52:45

电源布局、网口电路、音频走线的PCB设计

2021-03-04 06:10:24

规则一:高速信号走线屏蔽规则 在高速的设计中,时钟等关键的高速信号线,走线需要进行屏蔽处理,如果没有屏蔽或只屏蔽了部分,都会造成EMI的泄漏。建议屏蔽线,每1000mil,打孔接地。 图1

2018-09-20 10:38:01

高速PCB设计布线系统的传输速率在稳步加快的同时也带来了某种防干扰的脆弱性,这是因为传输信息的频率越高,信号的敏感性增加,同时它们的能量越来越弱,此时的布线系统就越容易受干扰。干扰无处不在,电缆

2016-01-06 16:43:09

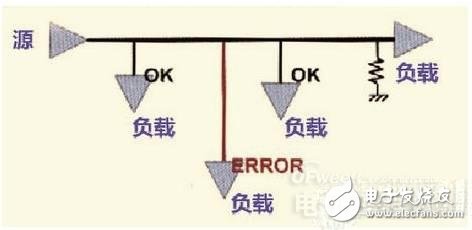

的PCB设计中,时钟等关键的高速信号线,走线需要进行屏蔽处理,如果没有屏蔽或只屏蔽了部分,都会造成EMI的泄漏。建议屏蔽线,每1000mil,打孔接地。规则二:高速信号的走线闭环规则由于PCB板的密度越来越高

2017-11-02 12:11:12

什么是高速pcb设计高速线总体规则是什么?

2019-06-13 02:32:06

PCB走线策略

布线(Layout)是PCB设计工程师最基本的工作技能之一。走线的好坏将直接影响到整个系统的性能,大多数高速的设计理论也要最终经过Layout得

2006-09-25 14:11:02 7284

7284 高速信号走线规则教程

随着信号上升沿时间的减小,信号频率的提高,电子产品的EMI问题,也来越受到电子工程师的关注。高速PCB设计的成功,对EMI

2009-04-15 08:49:27 3220

3220

PCB设计与走线PCB设计与走线layout对PCB走线与摆件规则全面了解和 掌握提升走线和摆件技能。

2016-07-21 16:33:13 0

0 开关电源的PCB设计(布局、排版、走线)规范,感兴趣的小伙伴们可以看看。

2016-07-26 14:09:33 0

0 开关电源的PCB设计(布局、排版、走线)规范

2016-09-06 16:03:47 0

0 PCB设计布线中的3种特殊走线技巧,学习资料,感兴趣的可以看看。

2022-05-12 10:34:20 0

0 在高速的PCB设计中,时钟等关键的高速信号线,走线需要进行屏蔽处理,如果没有屏蔽或只屏蔽了部分,都会造成EMI的泄漏。建议屏蔽线,每1000mil,打孔接地。

2017-08-25 15:35:24 2566

2566

PADS可提供强大且易于使用的多走线高速布线功能,帮助您应对这些挑战。让您可以根据PCB设计定义的规则选择并完成多走线布线。以及根据需要选择要完成的走线数量。如果采用PADS多走线HSDRouter,一切尽在您的掌握之中。

2017-09-19 11:41:38 29

29 高速PCB设计规则 1)、线与线,线与元件焊盘,线与贯通孔,元件焊盘与贯通孔,贯通孔与贯通孔之间的距离是否合理,是否满足生产要求。 (2)、电源线和地线的宽度是否合适,电源与地线之间是否紧耦合(低

2017-09-26 16:04:33 0

0 规则一:高速信号走线屏蔽规则 在高速的PCB设计中,时钟等关键的高速信号线,走线需要进行屏蔽处理,如果没有

2017-11-25 07:43:00 8707

8707

布线(Layout)是PCB设计工程师最基本的工作技能之一。走线的好坏将直接影响到整个系统的性能,大多数高速的设计理论也要最终经过 Layout得以实现并验证,由此可见,布线在高速PCB设计中

2017-12-01 10:37:31 0

0 布线(Layout)是PCB设计工程师最基本的工作技能之一。走线的好坏将直接影响到整个系统的性能,大多数高速的设计理论也要最终经过Layout得以实现并验证,由此可见,布线在高速PCB设计中是至关重要的。下面将针对实际布线中可能遇到的一些情况,分析其合理性,并给出一些比较优化的走线策略。

2018-04-14 11:06:00 4042

4042

本文主要介绍的是pcb开窗,首先介绍了PCB设计中的开窗和亮铜,其次介绍了如何实现PCB走线开窗上锡,最后阐述了PCB设计怎样设置走线开窗的步骤,具体的跟随小编一起来了解一下。

2018-05-04 15:37:30 40670

40670

布线(Layout)是 PCB设计工程师最基本的工作技能之一。走线的好坏将直接影响到整个系统的性能,大多数高速的设计理论也要最终经过 Layout 得以实现并验证,由此可见,布线在高速 PCB设计中

2018-07-06 15:28:18 6751

6751 学习高速PCB设计,首先要知道什么是传输线。信号会产生反射,就是因为PCB上的走线具有一定的阻抗,线上阻抗与输出端的阻抗不匹配,就会导致信号反射。信号在PCB中传输会有延时,如果时序没有匹配,系统就会罢工。这些都是因为传输线产生的问题。

2019-12-16 07:59:00 7828

7828

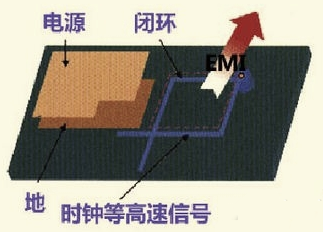

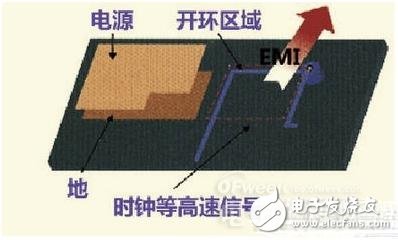

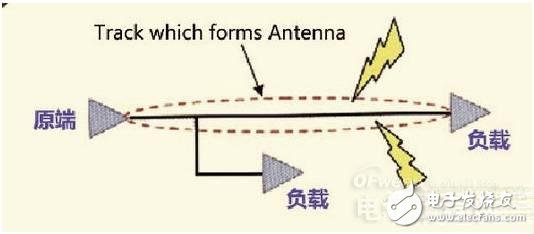

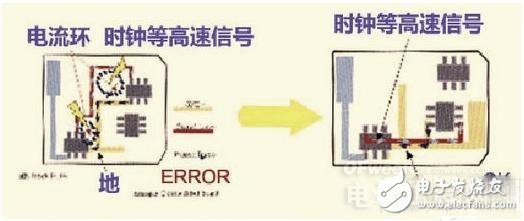

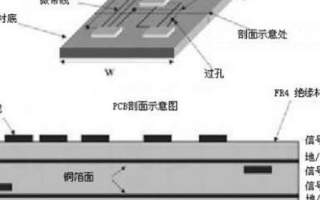

规则 由于PCB的密度越来越高,很多PCBlayout工程师在走线的过程中,很容易出现这样的失误,如图2所示。 图2 时钟信号等高速信号网络,在多层的PCB走线的时候产生了闭环现象,这种闭环现象会产生环形天线,增加EMI的辐射强度。 规则三、高速信号的走线开

2018-09-12 09:10:01 1771

1771 布线(Layout)是PCB设计工程师最基本的工作技能之一。走线的好坏将直接影响到整个系统的性能,大多数高速的设计理论也要最终经过Layout得以实现并验证,由此可见,布线在高速PCB设计中是至关重要的。

2019-02-05 08:49:00 4773

4773

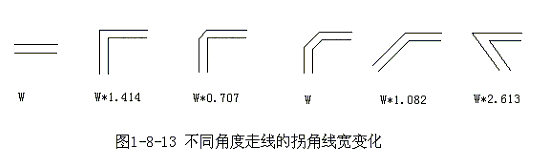

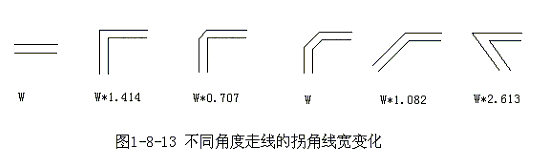

直角走线一般是PCB布线中要求尽量避免的情况,也几乎成为衡量布线好坏的标准之一,那么直角走线究竟会对信号传输产生多大的影响呢?从原理上说,直角走线会使传输线的线宽发生变化,造成阻抗的不连续。其实不光是直角走线,顿角,锐角走线都可能会造成阻抗变化的情况。

2019-07-24 15:12:01 1967

1967

布线(Layout)是PCB设计工程师最基本的工作技能之一。走线的好坏将直接影响到整个系统的性能,大多数高速的设计理论也要最终经过Layout得以实现并验证,由此可见,布线在高速PCB设计中是至关重要的。

2019-06-04 14:18:23 1676

1676 布线(Layout)是PCB设计工程师最基本的工作技能之一。走线的好坏将直接影响到整个系统的性能,大多数高速的设计理论也要最终经过Layout得以实现并验证,由此可见,布线在高速PCB设计中

2019-04-30 08:00:00 0

0 在高速的PCB设计中,时钟等关键的高速信号线,走线需要进行屏蔽处理,如果没有屏蔽或只屏蔽了部分,都会造成EMI的泄漏。建议屏蔽线,每1000mil,打孔接地。

2019-05-06 18:08:15 4913

4913 布线(Layout)是PCB设计工程师最基本的工作技能之一。走线的好坏将直接影响到整个系统的性能,大多数高速的设计理论也要最终经过Layout得以实现并验证,由此可见,布线在高速PCB设计中

2019-07-01 15:24:50 6358

6358 布线(Layout)是PCB设计工程师最基本的工作技能之一。走线的好坏将直接影响到整个系统的性能,大多数高速的设计理论也要最终经过Layout得以实现并验证,由此可见,布线在高速PCB设计中

2019-07-19 16:47:50 0

0 高速PCB设计EMI有什么规则

2019-08-21 14:38:03 1321

1321

在高速的PCB设计中,时钟等关键的高速信号线,走需要进行屏蔽处理,如果没有屏蔽或只屏蔽了部分,都是会造成EMI的泄漏。

2019-12-16 14:52:30 3830

3830

规则一:高速信号走线屏蔽规则 如上图所示: 在高速的PCB设计中,时钟等关键的高速信号线,走需要进行屏蔽处理,如果没有屏蔽或只屏蔽了部分,都是会造成EMI的泄漏。 建议屏蔽线,每1000mil,打孔

2020-02-14 11:53:40 13255

13255 如上图所示:在PCB设计中,时钟等关键的高速信号线,走需要进行屏蔽处理,如果没有屏蔽或只屏蔽了部分,都是会造成EMI的泄漏。建议屏蔽线,每1000mil,打孔接地。

2

2020-06-05 10:54:04 3682

3682 布线(Layout)是PCB设计工程师最基本的工作技能之一。走线的好坏将直接影响到整个系统的性能,大多数高速的设计理论也要最终经过Layout得以实现并验证,由此可见,布线在高速PCB设计中

2020-10-14 10:43:00 6

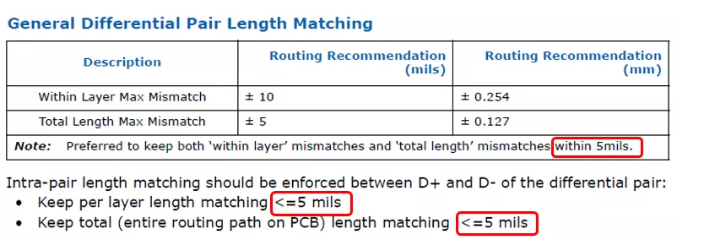

6 在PCB设计中,等长走线主要是针对一些高速的并行总线来讲的。 由于这类并行总线往往有多根数据信号基于同一个时钟采样,每个时钟周期可能要采样两次(DDRSDRAM)甚至4次,而随着芯片运行频率的提高

2020-10-24 09:29:38 10836

10836 在 PCB 设计中,等长走线主要是针对一些高速的并行总线来讲的。由于这类并行总线往往有多根数据信号基于同一个时钟采样,每个时钟周期可能要采样两次(DDR SDRAM)甚至 4 次,而随着芯片运行

2020-11-22 11:54:17 20854

20854 电子发烧友网为你提供图解在高速的PCB设计中的走线规则资料下载的电子资料下载,更有其他相关的电路图、源代码、课件教程、中文资料、英文资料、参考设计、用户指南、解决方案等资料,希望可以帮助到广大的电子工程师们。

2021-03-27 08:43:14 24

24 电子发烧友网为你提供8条规则,讲讲PCB设计走线资料下载的电子资料下载,更有其他相关的电路图、源代码、课件教程、中文资料、英文资料、参考设计、用户指南、解决方案等资料,希望可以帮助到广大的电子工程师们。

2021-03-29 16:50:27 12

12 @[TOC]PCB设计经验(1)#PCB设计规则#PCB走线经验#快捷键的使用#易犯错误汇总

2021-11-05 18:35:59 19

19 PCB设计规则你知几何,20个PCB设计规则送给你。

2021-11-06 15:36:00 71

71 布线(Layout)是pcb设计工程师最基本的工作技能之一。走线的好坏将直接影响到整个系统的性能,大多数高速的设计理论也要最终经过Layout得以实现并验证,由此可见,布线在高速pcb设计中

2022-02-10 12:11:07 40

40 布线(Layout)是PCB设计工程师最基本的工作技能之一。走线的好坏将直接影响到整个系统的性能,大多数高速的设计理论也要最终经过 Layout 得以实现并验证,由此可见,布线在高速 PCB 设计中

2022-02-11 15:24:33 30

30 由于PCB板的密度越来越高,很多PCB LAYOUT工程师在走线的过程中,很容易出现一种失误,即时钟信号等高速信号网络,在多层的PCB走线的时候产生了闭环的结果,这样的闭环结果将产生环形天线,增加EMI的辐射强度。

2022-08-08 10:09:05 1294

1294 布线(Layout)是PCB设计工程师最基本的工作技能之一。走线的好坏将直接影响到整个系统的性能,大多数高速的设计理论也要最终经过Layout得以实现并验证,由此可见,布线在高速PCB设计中是至关重要的。

2022-08-12 14:38:39 2167

2167 蛇形走线是PCB设计中会遇到的一种比较特殊的走线形式(如下图所示),很多人不理解蛇形走线的意义,下面对蛇形走线的作用进行简单介绍。

2023-03-30 18:14:23 6219

6219 设计 PCB 变得非常容易, 由于可用的工具负载。对于正在接触PCB设计的初学者来说, 他可能不太关心PCB中使用的走线特性。然而,当你爬上梯子时,注意PCB走线是非常重要的。在本文中,我们汇总了一些您应该了解的有关PCB走线以及如何为您的PCB设计正确走线的重要事项。

2023-05-13 15:15:46 6742

6742

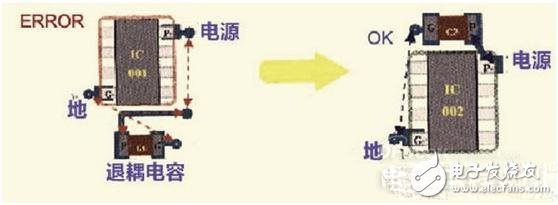

解决。 高速信号走线屏蔽规则 如上图所示:在高速的PCB设计中,时钟等关键的高速信号线,则需要进行屏蔽处理,如果没有屏蔽或只屏蔽了部分,都是会造成EMI的泄漏。 建议屏蔽线每1000mil打孔接地 。 高速信号的走线闭环规则 由于PCB板的密度越来越高,很多PCB

2023-05-22 09:15:58 2338

2338

高速电路无疑是PCB设计中要求非常严苛的一部分,因为高速信号很容易被干扰,导致信号质量下降,所以在PCB设计的过程中就需要避免或降低这种情况的发生。 在具体的高速电路布局布线中,这些知识技能需要掌握

2023-11-06 14:55:20 1317

1317 PCB设计中常见的走线等长要求

2023-11-24 14:25:36 6535

6535

由于 PCB 板的密度越来越高,许多 PCB LAYOUT 工程师在走线的过程中,较容易出现一种失误,即时钟信号等高速信号网络,在多层的 PCB 走线的时候产生了闭环的结果,这样的闭环结果将产生环形天线,增加 EMI 的辐射强度。

2024-01-08 15:33:04 2544

2544

随着电子产品的迅速发展,PCB(Printed Circuit Board)在电子设计中扮演着重要的角色。设计PCB走线时,合理设置规则是确保电路在安全、稳定、高效工作的基础。本文将详细介绍PCB走

2024-01-09 10:45:15 4008

4008 在高速的 PCB 设计中,时钟等关键的高速信号线,走线需要进行屏蔽处理,如果没有屏蔽或只屏蔽了部分,都会造成 EMI 的泄漏。

2024-01-10 16:03:05 1828

1828

的关注。据统计,几乎60%的EMI问题都可以通过优化高速PCB设计来解决。本文将详细介绍高速PCB设计解决EMI问题的九大规则,帮助工程师们在设计中有效减少EMI的产生。 高速PCB设计EMI九大关键规则 规则一:高速信号走线屏蔽规则 在高速PCB设计中,时钟等关键的高速信号线

2024-12-24 10:08:42 934

934 在高速数字电路设计中,信号完整性(SI)是确保系统性能和可靠性的核心要素。高速信号线的走线规则对于维持信号质量、减少噪声干扰以及优化时序性能至关重要。本文将深入探讨高速信号线走线的关键规则,旨在为工程师提供全面的设计指导和实践建议。

2025-01-30 16:02:00 2427

2427 : 高速电路PCB设计EMI方法与技巧 一、信号走线规则 屏蔽规则: 关键高速信号线(如时钟线)需进行屏蔽处理,可在信号线周围设置接地的屏蔽层,或将高速线布置在内部信号层,上下层铺铜接地作为屏蔽。 建议屏蔽线每1000mil打孔接地,确保屏蔽有效性。 闭环与开环规则: 避

2025-11-10 09:25:22 433

433

电子发烧友App

电子发烧友App

评论