FPGA/ASIC技术

电子发烧友本栏目为FPGA/ASIC技术专栏,内容有fpga培圳资料、FPGA开发板、FPGA CPLD知识以及FPGA/ASIC技术的其它应用等;是您学习FPGA/ASIC技术的好栏目。新型“扩散式忆阻器”可逼真模拟突触行为

据美国趣味科学网站26日报道,美国科学家研制出了一种新型“扩散式忆阻器”,模拟了人脑两个神经元的结点——突触内钙离子的行为,逼真度有史以来最高。研究人员表示,新设备有助于开...

2017-11-10 969

Vivado Design Suite HLx 版本 2016.4 现已发布

最新版 Vivado HLx Edition 现已推出, 其中包括: 支持 Zynq® UltraScale+™ MPSoC ZCU102-ES2 和 Virtex® UltraScale+ VCU118-ES1 开发板 支持 Virtex UltraScale+ XCVU11P 和 XCVU13P 器件 针对 Kintex® 和 Virtex UltraScale™ 器件的...

2017-11-10 1275

玩转Xilinx嵌入式视觉开发者专区 让视觉系统开发更加简单

开发下一代视觉系统的 “一站式平台” ——Xilinx嵌入式视觉开发者专区 赛灵思近日推出了面向软件、硬件及系统开发人员的嵌入式视觉开发者专区,以帮助他们加速生产力并打造 All Programma...

2017-11-10 1389

Enclustra公司在ESC2016大会上推出Mercury+ XU1 SOM核心模块

ESC是Embedded Systems Conference的简称,即嵌入式系统大会,每年都会举行一次。ESC2016于2016年12月6号至2016年12月8号在美国加州圣何塞(San Jose)会议中心举行,为期三天。行业内的各大电子和半导体...

2017-11-10 1610

TSN开放标准挂保证 车用以太网抢进ADAS市场

作者:Arthur Marris/Sachin Dhingra/Robert Schweiger 以太网络技术具有成本低、重量轻、数据传输率高的特性,且并非专有性质,因此成为实现先进驾驶辅助系统(ADAS)应用及自动驾驶的关键。为达成操控...

2017-11-10 1766

“让系统具有自愈能力”:基于Artix

冗余系统是为了为增加系统的可靠性,采取两套或两套以上相同、相对独立配置的设计。采取两套同样配置的独立硬件、软件或设计等,可以做到在其中一套系统出现故障时,另一套系统能立即...

2017-11-10 647

popping:一个基于Zynq架构,OpneCV库的目标跟踪系统

1999年,Intel建立了OpenCV库(Open Source Computer Vision library),如今由Willow Garage提供支持。它是一个基于BSD许可的开源发行的跨平台计算机视觉库,可以运行在Linux,Windows和Mac OS操作系统上。OpenC...

2017-11-10 1157

数据中心加速,一文说清FPGA与GPU、ASIC目前的竞争格局

作者:李卫忠 文章来源:doit 超大规模云计算中心、电子商务和社交网络数据中心,正面临着数据类型复杂的工作负载加速之难题。 数据中心加速的主要途径 传统CPU处理能力的需要突破已经成...

2017-11-10 574

基于OpenPOWER的深度学习方案扩展到新发布版本

作者:Michael Gschwind,IBM Systems机器学习和深度学习首席工程师 我很荣幸地宣布推出面向OpenPOWER深度学习框架的重大更新,作为软件“distros”(发布版本)的安装如同使用Ubuntu系统安装程序一样...

2017-11-10 478

详细解读Zynq的三种启动方式(JTAG,SD,QSPI)

本文介绍zynq上三种方式启动文件的生成和注意事项,包括只用片上RAM(OCM)和使用DDR3两种情况。 JTAG方式 JTAG方式是调试中最常用的方式,在SDK中 在“Project Explorer”窗口工程上右键->Debug As->...

2017-11-10 16173

I/O接口标准解析系列教程(3):HCSL和LPHCSL

LPHCSL(Low-Power HCSL)是为了降低传统的HCSL驱动器的功耗而开发的。LPHCSL的主要优点包括更好的驱动长线的性能,易于AC耦合,减少PCB板子面积,易于布线,降低材料成本,本文将讨论这些优点,...

2017-11-10 10274

在Microzed上构建嵌入式linux系统(ubuntu16.04下)

Linux启动需要4个文件: 1. boot.bin 2. device_tree.dtb 3. uImage 4. uramdisk.image.gz a1.生成boot.bin文件需要:(生成boot.bin时,下面三个文件顺序不能错。) (1)FSBL:第一级启动引导程序,选择Zynq FSBL模版...

2017-11-10 1841

I/O接口标准解析系列教程(2):CML、PECL、LVECL和LVDS

CML(Current-mode llogic)它并没有一个标准,是基于简单的差分放大器,如图2所示。通常取R1=R2=50欧姆,|VOUT+ - VOUT-| = R1 * i1 = 50*i1,不同的厂家i1值不一样,所以,电压摆幅不同的厂家也不一样。不...

2017-11-10 6876

手把手教你创建Linux设备驱动和应用程序

其实我们创建的myLed IP相对于Linux操作系统可以是它的一个底层设备,因为PS总线为myLed IP分配了寻址地址,这样我们就可以创建myLed IP模块的硬件驱动,然后搭建应用程序,实现软硬件协同设计...

2017-11-10 4847

Zybo全栈开发入门教程(基于Linux嵌入式系统):10个步骤自定义IP模块

可以说zybo是mini-zedboard。Zybo全栈开发教程共分为三部分:自定义IP、移植Linux操作系统、编写驱动模块和应用。通过这三部分你将能够全面熟悉Zynq AP SoC架构的开发流程,包括FPGA逻辑电路设计、...

2017-11-10 4656

如何利用Vivado HLS处理许多位准确或任意精度数据类型

我们在设计硬件时,它往往是要求更精确的位宽。例如,一个filter的输入是12位和一个累加器的结果只需要一个最大范围为27位。然而对于硬件设计来说,使用标准的C数据类型会造成硬件成本的...

2017-11-10 3435

7Series FPGA高速收发器使用教程分享

GTX RX接收端的结构和TX发送端类似,数据流方向相反,不过和发送端也有一些区别,GTX的RX接收端结构图如图1所示: 图1 下面将根据数据流方向介绍一下RX接收端各个电路部分的功能。 RX Equali...

2017-11-10 6201

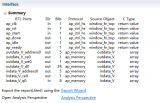

Adam Taylor玩转MicroZed系列第76部分:关联布局宏的约束

By Adam Taylor 在约束系列的最后,我们讲讲关联布局宏(RPM)的约束。RPM允许你在FPGA的布局中将DSP、FF、LUT和RAMS等资源组合在一起。与PBlocks不同,RPM并不把设计元素的位置限制到特定区域去(除...

2017-11-10 1242

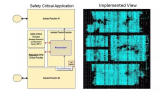

嵌入式视觉要考虑哪些安全性与保密性问题

作者:Aaron Behman 和 Adam Taylor 嵌入式视觉 (EV) 系统的广泛应用已经是无所不在,高级驾驶员辅助系统 (ADAS)、机器视觉、医疗成像、增强现实以及众多其他应用等等, 都离不开一个高效的嵌入式...

2017-11-10 1316

卷积神经网络(CNN)的参数优化方法

著名: 本文是从 Michael Nielsen的电子书Neural Network and Deep Learning的深度学习那一章的卷积神经网络的参数优化方法的一些总结和摘录,并不是我自己的结论和做实验所得到的结果。我想Michael的...

2017-11-10 6285

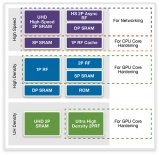

使用DesignWare逻辑库和嵌入式存储器以获得16FFC SOC最佳PPA

作者:Ken Brock,Synopsys产品市场营销经理 TSMC最近宣布其第四代主要16纳米工艺,即16FFC(16纳米FinFET紧凑版), 进入批量生产。该工艺提供了一种简单的从28纳米工艺进行转移的方式,它具有优异...

2017-02-07 1155

高级驾驶员感知系统和All Programmable SoC

作者:Aaron Behman 和 Adam Taylor 道路安全也能从摩尔定律中受益良多?是的,处理能力的提升以及 CMOS 图像传感器 (CIS) 和其他传感器技术的发展,让车辆制造商得以推出高级驾驶员感知系统 (ADA...

2017-02-07 711

赛灵思重点发展领域 高效率视频编码是什么

视频无处不在。它一直是用于娱乐、信息与教育的工具,为赛灵思带来了大量极好的机遇,特别是在涉及到更多、更好、更快像素时。我们已经看到分辨率超过 1080p60 ,向 4K 乃至 8K 分辨率迈进...

2017-02-07 1127

在汽车、物联网中实施MIPI相机和显示接口

在汽车、物联网和多媒体应用中,对相机和显示屏的使用正在不断增加,设计人员需要多种图像和显示接口解决方案,来满足日益严格的功率和性能要求。...

2017-02-07 2267

Python常用PEP8编码规范和建议经验分享

缩进 每级缩进用4个空格。 括号中使用垂直隐式缩进或使用悬挂缩进。 EXAMPLE: # (垂直隐式缩进)对准左括号 foo = long_function_name(var_one, var_two, var_three, var_four) # (悬挂缩进) 一般情况只需多一层缩进...

2017-02-07 1399

使用教程分享连载:在Zynq AP SoC设计中高效使用HLS IP(二)

对于硬件加速模块来说,这些硬件加速模块会消耗源于CPU存储器的数据,并且以streaming方式产生数据。本文使用Vivado HLS和xfft IP模块(在IP Integrator使用HLS IP那节用过)。这些模块是连接到HP0的...

2017-02-07 4263

使用教程分享:在Zynq AP SoC设计中高效使用HLS IP(一)

高层次综合设计最常见的的使用就是为CPU创建一个加速器,将在CPU中执行的代码移动到FPGA可编程逻辑去提高性能。本文展示了如何在Zynq AP SoC设计中使用HLS IP。 在Zynq器件应用Vivado HLS IP 这里集...

2017-02-07 4363

C++中常用的复合数据类型在Vivado Hls中的应用方法

Vivado hls既支持结构体,也支持枚举类型,这两种类型都可以作为接口出现在顶层函数。如果结构体出现在顶层函数,可以通过field_level 和struct_level进行封装,如果枚举类型作为接口出现在顶层...

2017-02-07 2450

在进行时序分析时为什么CPR操作得出的效果却是相反的?

在进行时序分析时片上工艺差别通常会导致严重的“时钟悲观效应”。这种问题可以通过CPR(Clock Pessimism Reduction)操作来恢复.然而经常有用户咨询我们说在他们的设计中CPR操作并没有降低“时...

2017-02-07 1725

Vivado环境下如何在IP Integrator中正确使用HLS IP

介绍如何设计HLS IP,并且在IP Integrator中使用它来作一个设计——这里生成两个HLS blocks的IP,并且在一个FFT(Xilinx IP)的设计中使用他们,最终使用RTL testbench来验证设计。 Integrate带有Xilinx IP B...

2017-02-07 4851

编辑推荐厂商产品技术软件/工具OS/语言教程专题

| 电机控制 | DSP | 氮化镓 | 功率放大器 | ChatGPT | 自动驾驶 | TI | 瑞萨电子 |

| BLDC | PLC | 碳化硅 | 二极管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 无刷电机 | FOC | IGBT | 逆变器 | 文心一言 | 5G | 英飞凌 | 罗姆 |

| 直流电机 | PID | MOSFET | 传感器 | 人工智能 | 物联网 | NXP | 赛灵思 |

| 步进电机 | SPWM | 充电桩 | IPM | 机器视觉 | 无人机 | 三菱电机 | ST |

| 伺服电机 | SVPWM | 光伏发电 | UPS | AR | 智能电网 | 国民技术 | Microchip |

| 开关电源 | 步进电机 | 无线充电 | LabVIEW | EMC | PLC | OLED | 单片机 |

| 5G | m2m | DSP | MCU | ASIC | CPU | ROM | DRAM |

| NB-IoT | LoRa | Zigbee | NFC | 蓝牙 | RFID | Wi-Fi | SIGFOX |

| Type-C | USB | 以太网 | 仿真器 | RISC | RAM | 寄存器 | GPU |

| 语音识别 | 万用表 | CPLD | 耦合 | 电路仿真 | 电容滤波 | 保护电路 | 看门狗 |

| CAN | CSI | DSI | DVI | Ethernet | HDMI | I2C | RS-485 |

| SDI | nas | DMA | HomeKit | 阈值电压 | UART | 机器学习 | TensorFlow |

| Arduino | BeagleBone | 树莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 华秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |