FPGA/ASIC技术

电子发烧友本栏目为FPGA/ASIC技术专栏,内容有fpga培圳资料、FPGA开发板、FPGA CPLD知识以及FPGA/ASIC技术的其它应用等;是您学习FPGA/ASIC技术的好栏目。7 六大成员公开, 想知道他们都是谁吗?

赛灵思今天公布了其最新 Spartan-7 FPGA系列 的六大成员。 所有六大成员均为 28nm 7系列中的最低成本器件, 专为低成本和低单位I/O 成本优化,却同时提供出色的单位功耗性能比。 和 Xilinx Spa...

2017-02-08 545

直指嵌入式视觉和工业物联网应用,Xilinx全线扩充成本优化型产品系列

赛灵思扩充其 Spartan、Artix 和 Zynq 系列,满足下一代应用的任意互联、传感器融合、精确控制、图像处理、分析、安全性与保密性需求。 All Programmable 技术和器件的全球领先企业赛灵思公司(...

2017-02-08 335

百度研究院首推开源测算工具DeepBench

据美国新闻网站“Forward Geek”9月26日报道,在26、27两日举行的奥莱利人工智能大会(O’Reilly AI Conference)上,百度硅谷人工智能实验室高级研究员格雷格•迪亚摩斯(Greg Diamos)和夏朗•纳兰(Sharan...

2017-02-08 242

如何加速你的PCIe 4.0系统设计

PCIe是目前最新的总线和接口标准,最早是由英特尔于2001年提出的。PCIe属于高速串行点对点双通道高带宽传输,所连接的设备分配独享通道带宽,不共享总线带宽,主要支持主动电源管理,错误...

2017-02-08 1398

一款基于Zynq的4通道VITA49标准的射频(RF)信号接收器

目前VITA49无线传输标准是软件定义无线电(SDR)接收器供应商共同遵守的行业标准,在之前各大供应商会自定义自己规范的数字化数据格式和元数据格式,造成了不同品牌设备之间的不可互操作...

2017-02-08 1429

全球最大望远镜阵列实现超深空最深层观测

向更深层次进军。对宇宙遥远角落的新观测已经使得人们对于早期宇宙的理解更深一层。日前,国际天文学家团队利用强有力的阿塔卡玛大型毫米/亚毫米波望远镜(ALMA)阵列,对来自哈勃望远...

2017-02-08 398

Photonfocus公司推出高性能GigE摄像机QR1,速度是标准的四倍!

Photonfocus公司是一家专门从事于CMOS图像传感器和工业CMOS摄像机的高科技公司,因此该公司在CMOS图像传感器设计方面有着非常深厚的经验,开发除了HDR(高动态范围)CMOS图像传感器,并且积累了...

2017-02-08 821

UltraScale Prodigy Logic Module Series

S2C的UltraScale Prodigy™ Logic Modules系列产品主要基于Xilinx的Virtex UltraScale和Kintex UltraScale FPGA而设计。Logic Modules 包含业内最全面性价比最高的五种解决方案:四颗Virtex UltraScale(VU),双颗VU,单颗VU,...

2017-02-08 673

网上研讨会: Xilinx 高精度视觉系列研讨会之二:面向机器人与无人机的视觉系统

嵌入式视觉是现如今最令人兴奋的应用之一。赋予机器“看见”并“感知”我们周围世界的能力,创造出无穷无尽的商业机会。在本次研讨会中,赛灵思将针对视觉导向的机器人和无人机应用展...

2017-02-08 269

深入浅出玩转Xilinx Vivado工具实战设计技巧

Xilinx采用先进的 EDA 技术和方法,提供了全新的工具套件Vivado,面向未来“All-Programmable”器件。Vivado开发套件提供全新构建的SoC 增强型、以IP和系统为中心的下一代开发环境,以解决系统级集成...

2017-02-08 934

IEEE最新白皮书《软件定义的5G生态系统》综述

IEEE的SDN研究组(IEEE SDN Initiative)于2016年7月15日发布了其第二份白皮书“Towards 5G Software-Defined Ecosystems:Technical Challenges, Business Sustainability and Policy Issues(《软件定义的5G生态系统:技术挑战、...

2017-02-08 908

动态控制实现最佳效率 全新配电架构缓减数据中心耗电成长

传统固定电压配电的做法已无法满足数据大爆炸时代的系统所需。全新配电架构与控制技术的问世,使得转换器可以配合负载条件实时动态调节电压,维持在最佳效率。藉由这项技术,数据中心...

2017-02-08 534

2016 IBM Edge大会,Supervessel 分享FPGA云端加速领先技术

一年一度的IBM Edge大会在美国拉斯维加斯正式举行。来自全球6000余名IT企业代表、CTO、CIO、开发者齐聚拉斯维加斯参加这场技术交流盛宴。SuperVessel 超能云再次受到大会邀请,陈飞博士代表开发...

2017-02-08 306

免费下载!一款基于Zynq的Harris角点检测算法实现Demo

作者:Stark 角点检测(Corner Detection)是计算机视觉系统中用来获取图像特征的一种方法,广泛应用于运动检测、图像匹配、视频跟踪、三维建模和目标识别等领域中,也称为特征点检测。角点...

2017-02-08 682

7000 ARM+FPGA进阶级处理器+全可编程逻辑智能互联开发系统

ZedBoard™是一款搭载Xilinx Zynq™-7000 all programmable系统芯片(AP系统芯片)的低成本开发板。无论是Linux®,Android®,Windows®亦或基于其它操作系统/实时操作系统进行设计,ZedBoard都能满足开发者的...

2017-02-08 480

你知道嵌入式系统三项标准是什么吗?

作者:Steve Leibson, 赛灵思战略营销与业务规划总监 George T Haber,Cresta基金创建者,CrestaTech的创建者,发表了他自己的“哈勃定律”—— “ 如果一个事情可以用软件实现,那它一定可以被实现...

2017-02-08 1010

Adam Taylor玩转MicroZed系列69:关于Zynq的约束简介

通过前面的学习,我们已经对Zynq系列的PL和PS部分已经有了相当多的了解。其中有关约束的部分我们曾经提到过但是没有重点关注。约束可以添加特定的信息到你的设计,并在综合工具和实现工...

2017-02-08 1036

FPGA上的MACsec IP提高数据中心安全性

(摘抄和节选自最新一期的Xcell杂志) By Paul Dillien and Tom Kean, PhD 保护信息的典型策略是当数据在网络中传递和在数据中心内流动的时候,对数据进行加密处理。万一数据被未经授权的嗅探链接...

2017-02-08 553

如何削减设计中复杂的多接口标准?

作者:Steve Leibson, 赛灵思战略营销与业务规划总监 互联标准的数量在广播和专业A/V设备市场上持续上升,它会使你的生活变得多样,但是却会使你的设计更加复杂,同时,它会使可编程器件的...

2017-02-08 332

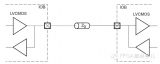

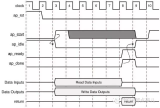

NI LabVIEW Communications 802.11应用架构

802.11应用架构根据IEEE 802.11无线标准,提供了立即可用、方便修改的实时正交频分复用(OFDM)物理层(PHY)和底层媒体访问控制层(MAC)参考设计。 802.11应用架构包含于LabVIEW Communications系统设计套件...

2017-02-08 3196

MicroZed开发板笔记,第70部分:约束

By Adam Taylor 在之前的博客中介绍了Vivado的基本时序约束,时序约束定义了系统频率或自己所定义的时钟频率。为建立良好的时序约束,下一步是需要建立时钟路径之间关系的定义。这样,Vivad...

2017-02-08 394

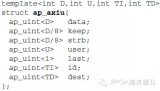

HLS系列–High Level Synthesis(HLS)的端口综合6

在上一章,介绍了Block Level Interface。 本章里着重介绍下Port Level Interface的2中子类别:No I/O Protocol和Wire handshakes 下面先介绍下No I/OProtocol ap_none: ap_none是HLS最简单的一种接口协议类型,不论是...

2017-02-08 935

Xilinx FPGA I/O电平标准简介(一)

Xilinx FPGA的I/O兼容多种电平标准,包括LVTTL、LVCMOS、LVDS、LVPECL等,下面对各类电平标准做简要介绍。 一、LVTTL(LowVoltage Transistor-Transistor Logic) LVTTL电平标准即低电压三极管-三极管逻辑电平标准...

2017-02-08 11310

基于OpenCV的双目摄像机标定

本文CameraCalibrator类源代码来自于OpenCV2 计算机视觉编程手册(Robert Laganiere 著 张静 译) 阅读本文之前请先阅读以下三篇博文: 机器视觉学习笔记(4)——单目摄像机标定参数说明 机器视觉学...

2017-02-08 1284

HLS系列–High Level Synthesis(HLS)的端口综合5

在之前的3章里,着重讲解了HLS对AXI端口(包括axi-lite,axi-stream和full axi端口)的综合实现问题,下面让我们来介绍一下其它的端口类型是如何实现的。 在开始之前,先来个总结回顾,看看HLS支...

2017-02-08 912

基于OpenCV的单目摄像机标定

本文CameraCalibrator类源代码来自于OpenCV2 计算机视觉编程手册(Robert Laganiere 著 张静 译) 强烈建议阅读机器视觉学习笔记(4)——单目摄像机标定参数说明之后再阅读本文 1.单目摄像机标定目的...

2017-02-08 1248

HLS系列–High Level Synthesis(HLS)的端口综合4

在上一章HLS提到了axi lite端口的综合方式,以及directive的一些语法规则。这一章里面,介绍一下axi-stream和full axi端口的综合实现问题。 AXI FULL端口的实现 HLS支持在数组或者指针参数上,AXI Mast...

2017-02-08 1162

美国开始测试内置模拟人脑芯片的计算机

腾讯科技讯 3月30日,为解决世界上最棘手的一些计算难题,美国劳伦斯利弗莫尔国家实验室(Lawrence Livermore National Laboratory)希望能够从人脑结构中获取灵感,因此该实验室计划于本月31日对一台...

2017-02-08 303

HLS系列–High Level Synthesis(HLS)的端口综合3

在上一章HLS提到了axi lite端口的综合方式,以及directive的一些语法规则。这一章里面,介绍一下axi-stream和full axi端口的综合实现问题。 1. AXI-Stream端口的实现 Stream端口没有地址的概念,使用Viv...

2017-02-08 821

HLS系列 – High LevelSynthesis(HLS) 的端口综合1

在之前HLS的基本概念1里有提及,HLS会把c的参数映射成rtl的端口实现。本章开始总结下HLS端口综合的一些知识。 1.HLS综合后的rtl端口大体可以分成2类: Clock Reset端口: 每个设计只能有一个Cloc...

2017-02-08 1210

编辑推荐厂商产品技术软件/工具OS/语言教程专题

| 电机控制 | DSP | 氮化镓 | 功率放大器 | ChatGPT | 自动驾驶 | TI | 瑞萨电子 |

| BLDC | PLC | 碳化硅 | 二极管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 无刷电机 | FOC | IGBT | 逆变器 | 文心一言 | 5G | 英飞凌 | 罗姆 |

| 直流电机 | PID | MOSFET | 传感器 | 人工智能 | 物联网 | NXP | 赛灵思 |

| 步进电机 | SPWM | 充电桩 | IPM | 机器视觉 | 无人机 | 三菱电机 | ST |

| 伺服电机 | SVPWM | 光伏发电 | UPS | AR | 智能电网 | 国民技术 | Microchip |

| 开关电源 | 步进电机 | 无线充电 | LabVIEW | EMC | PLC | OLED | 单片机 |

| 5G | m2m | DSP | MCU | ASIC | CPU | ROM | DRAM |

| NB-IoT | LoRa | Zigbee | NFC | 蓝牙 | RFID | Wi-Fi | SIGFOX |

| Type-C | USB | 以太网 | 仿真器 | RISC | RAM | 寄存器 | GPU |

| 语音识别 | 万用表 | CPLD | 耦合 | 电路仿真 | 电容滤波 | 保护电路 | 看门狗 |

| CAN | CSI | DSI | DVI | Ethernet | HDMI | I2C | RS-485 |

| SDI | nas | DMA | HomeKit | 阈值电压 | UART | 机器学习 | TensorFlow |

| Arduino | BeagleBone | 树莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 华秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |