FPGA/ASIC技术

电子发烧友本栏目为FPGA/ASIC技术专栏,内容有fpga培圳资料、FPGA开发板、FPGA CPLD知识以及FPGA/ASIC技术的其它应用等;是您学习FPGA/ASIC技术的好栏目。没有算法功力,是不可能成为高手的

算法是计算机科学领域最重要的基石之一,但却受到了国内一些程序员的冷落。许多学生看到一些公司在招聘时要求的编程语言五花八门就产生了一种误解,认为学计算机就是学各种编程语言,...

2017-02-11 2244

Verilog HDL简明教程(part1)

Verilog HDL是一种硬件描述语言,用于从算法级、门级到开关级的多种抽象设计层次的数字系统建模。被建模的数字系统对象的复杂性可以介于简单的门和完整的电子数字系统之间。数字系统能够...

2017-02-11 1561

FPGA基本知识与发展趋势(part2)

由于基于LUT 的FPGA 具有很高的集成度,其器件密度从数万门到数千万门不等,可以完成极其复杂的时序与逻辑组合逻辑电路功能,所以适用于高速、高密度的高端数字逻辑电路设计领域。...

2017-02-11 1004

针对2K/4K超高清视频验证的原型验证开发平台

北京亚科鸿禹电子有限公司在北京发布一款针对2K/4K超高清视频验证的原型验证开发平台-VeriTiger-M2000T。此平台作为亚科鸿禹”All-In-One”家族的最新成员,主要为广大的视音频SOC/IP的硬件/软件验...

2017-02-11 1936

FPGA实战开发技巧(10)

串行Flash的特点是占用管脚比较少,作为系统的数据存贮非常合适,一般都是采用串行外设接口(SPI 总线接口)。Flash 存贮器与EEPROM根本不同的特征就是EEPROM可以按字节进行数据的改写,而Flash只...

2017-02-11 1281

Xlinx FPGA的DSP设计工具和设计流程

因为手上有一块Xilinx的Spartan--3E开发板,前些日子陆陆续续学习了ISE的一般工程开发,熟悉了Xilinx ISE 10.x的软件操作和开发板的使用。近来没有事情,于是乎,又把那开发板拿出来把弄把弄,开...

2017-02-11 4347

FPGA实战开发技巧(9)

FPGA配置方式灵活多样,根据芯片是否能够自己主动加载配置数据分为主模式、从模式以及JTAG模式。典型的主模式都是加载片外非易失( 断电不丢数据) 性存储器中的配置比特流,配置所需的时钟...

2017-02-11 2407

FPGA实战开发技巧(8)

FPGA 设计的时序性能是由物理器件、用户代码设计以及EDA 软件共同决定的,忽略了任何一方面的因素,都会对时序性能有很大的影响。本节主要给出大规模设计中,赛灵思物理器件和EDA 软件的...

2017-02-11 1308

谈谈赛灵思的局部重配置技术

这里提到的局部重配置技术(Partial Reconfiguration) 是现场可编程门阵列(呵呵,就是FPGA了) 器件中的一部分。指的是在FPGA其他部分还在正常运行的情况下对其局部进行的重新配置。...

2017-02-11 2968

FPGA实战开发技巧(6)

时序性能是FPGA 设计最重要的指标之一。造成时序性能差的根本原因有很多,但其直接原因可分为三类:布局较差、逻辑级数过多以及信号扇出过高。...

2017-02-11 1113

FPGA实战开发技巧(7)

通常我们会为工程添加UCF 约束指定时序要求和管脚约束。但是UCF 约束是给MAP,PAR 等实现使用的,综合工具XST 并不能感知系统的时序要求。而为XST 添加XCF 约束却是使实现结果拥有最高频率的关...

2017-02-11 1185

利用FPGA的自身特性实现随机数发生器

本文主要介绍利用FPGA的自身的特性实现随机数发生器,在Virtex-II Pro开发板上用ChipScope观察随机数序列,以及在PCIe4Base(基于Virtex-4 FPGA)上实现。...

2017-02-11 14334

谈谈如何利用FPGA开发板进行ASIC原型开发

ASIC设计在尺寸和复杂性上不断增加,现代FPGA的容量和性能的新进展意味着这些设计中的2/3能够使用单个FPGA进行建模。...

2017-02-11 1420

FPGA实战开发技巧(5)

一般来讲,添加约束的原则为先附加全局约束,再补充局部约束,而且局部约束比较宽松。其目的是在可能的地方尽量放松约束,提高布线成功概率,减少ISE 布局布线时间。典型的全局约束包...

2017-02-11 843

FPGA实战开发技巧(4)

在代码编写完毕后,需要借助于测试平台来验证所设计的模块是否满足要求。ISE 提供了两种测试平台的建立方法,一种是使用HDL Bencher 的图形化波形编辑功能编写,另一种就是利用HDL 语言,相...

2017-02-11 1276

FPGA实战开发技巧(3)

所谓综合,就是将HDL语言、原理图等设计输入翻译成由与、或、非门和RAM、触发器等基本逻辑单元的逻辑连接( 网表),并根据目标和要求( 约束条件) 优化所生成的逻辑连接,生成EDF 文件。XST...

2017-02-11 1378

FPGA电路必须遵循的原则和技巧

在调试FPGA电路时要遵循必须的原则和技巧,才能降低调试时间,防止误操作损坏电路。通常情况下,能够参考以下步骤执行 FPGA硬件系统的调试。...

2017-02-11 1040

写verilog代码要有硬件的概念

因为Verilog是一种硬件描述语言,所以在写Verilog语言时,首先要有所要写的module在硬件上如何实现的概念,而不是去想编译器如何去解释这个module...

2017-02-11 3172

学好FPGA应该要具备的知识

阅读本文的人群:熟悉数字电路基本知识(如加法器、计数器、RAM等),熟悉基本的同步电路设计方法,熟悉HDL语言,对FPGA的结构有所了解,对FPGA设计流程比较了解。...

2017-02-11 1269

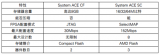

解密业界首款16nm产品核心技术

以赛灵思 20nm UltraScale 系列的成功为基础,赛灵思现又推出了全新的 16nm UltraScale+ 系列 FPGA、3D IC 和 MPSoC,凭借新型存储器、3D-on-3D 和多处理SoC(MPSoC)技术,再次领先一代提供了遥遥领先的价值...

2017-02-11 1190

LX110T的板子上跑demo的时候遇到的一些错误的解决办法总结

.前一段时间在玩xilinx送我在跑XUPV5-LX110T,首先跑xilinx给出的XUPV5-LX110T的demo设计,结果发现遇到了一些错误但是自己在网上发现很少有答案,就把自己的一些总结贴出来:...

2017-02-11 2333

Xilinx ISE是如何调用ModelSim进行仿真的

在我们用ModelSim仿真的时候经常是修改一点一点修改代码,这样会造成一个无奈的操作循环:修改代码--->编译代码--->仿真设置--->进入仿真页面--->添加需要观察的波形--->运行仿真...

2017-02-11 11603

记利用compxlibgui工具编译Xilinx库

当ISE调用ModelSim进行仿真的时候,如果在FPGA设计中使用了Xilinx提供的的IP core或者其他的原语语句,ModelSim不添加Xilinx相应的库文件的话,是无法仿真的。...

2017-02-11 1839

FPGA实战开发技巧(12)

在大规模设计的调试应该按照和设计理念相反的顺序,从底层测试,主要依靠ChipScope Pro 工具。下面主要介绍ChipScope Pro、FPGA Editor 组件的使用方法。...

2017-02-11 1002

ISE11.4对XC6SLX150进行开发时遇到的困难和挑战

目前,使用ISE11.4对XC6SLX150进行开发,在时序上遇到一些困难和挑战。痛定思痛,立即进行问题记录,希望能与各位共同进行探讨和分析。...

2017-02-11 2080

FPGA实战开发技巧(11)

在串行模式下,需要微处理器或微控制器等外部主机通过同步串行接口将配置数据串行写入FPGA芯片,其模式选择信号M[2:0]=3’b111...

2017-02-11 1361

FPGA中的多时钟域设计

在一个SOC设计中,存在多个、独立的时钟,这已经是一件很平常的事情了。大多数的SOC器件都具有很多个接口,各个接口标准都可能会使用完全不同的时钟频率。...

2017-02-11 1585

论工业控制系统的FPGA设计方法(3)

上次博文简要分析了人们研究使用FPGA来进行工业控制的驱动力,并介绍了FPGA器件与开发工具。随着器件成本的降低和器件性能的上升,FPGA必将在工业控制领域发挥更大的作用。...

2017-02-11 1460

编辑推荐厂商产品技术软件/工具OS/语言教程专题

| 电机控制 | DSP | 氮化镓 | 功率放大器 | ChatGPT | 自动驾驶 | TI | 瑞萨电子 |

| BLDC | PLC | 碳化硅 | 二极管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 无刷电机 | FOC | IGBT | 逆变器 | 文心一言 | 5G | 英飞凌 | 罗姆 |

| 直流电机 | PID | MOSFET | 传感器 | 人工智能 | 物联网 | NXP | 赛灵思 |

| 步进电机 | SPWM | 充电桩 | IPM | 机器视觉 | 无人机 | 三菱电机 | ST |

| 伺服电机 | SVPWM | 光伏发电 | UPS | AR | 智能电网 | 国民技术 | Microchip |

| 开关电源 | 步进电机 | 无线充电 | LabVIEW | EMC | PLC | OLED | 单片机 |

| 5G | m2m | DSP | MCU | ASIC | CPU | ROM | DRAM |

| NB-IoT | LoRa | Zigbee | NFC | 蓝牙 | RFID | Wi-Fi | SIGFOX |

| Type-C | USB | 以太网 | 仿真器 | RISC | RAM | 寄存器 | GPU |

| 语音识别 | 万用表 | CPLD | 耦合 | 电路仿真 | 电容滤波 | 保护电路 | 看门狗 |

| CAN | CSI | DSI | DVI | Ethernet | HDMI | I2C | RS-485 |

| SDI | nas | DMA | HomeKit | 阈值电压 | UART | 机器学习 | TensorFlow |

| Arduino | BeagleBone | 树莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 华秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |