相关的另一个重要的应用就是估算信号的延时,这个延时可以是模拟电路通道上的延时,比如测量发射机射频链路延时有多大。也可以是在无线空间传输的延时,比如无线电监测领域的辐射源定位,卫星导航信号的延时估算等等。

2014-01-10 14:28:19 2870

2870 一个卷积操作占用的内存 2. PipeCNN可实现性 PipeCNN论文解析:用OpenCL实现FPGA上的大型卷积网络加速 2.1 已实现的PipeCNN资源消耗 3. 实现大型神经网络

2022-07-10 09:24:45 1672

1672 “全局时钟和第二全局时钟资源”是FPGA同步设计的一个重要概念。合理利用该资源可以改善设计的综合和实现效果;如果使用不当,不但会影响设计的工作频率和稳定性等,甚至会导致设计的综合、实现过程出错

2023-07-24 11:07:04 655

655

大规模的整数加法在数字信号处理和图像视频处理领域应用很多,其对资源消耗很多,如何能依据FPGA物理结构特点来有效降低加法树的资源和改善其时序特征是非常有意义的。

2023-11-08 09:06:32 636

636

1.面积与速度的平衡与互换这里的面积指一个设计消耗 FPGA/CPLD 的逻辑资源的数量,对于 FPGA 可以用消耗的 FF(触发器)和 LUT(查找表)来衡量,更一般的衡量方式可以用设计所占的等价

2020-09-23 09:44:15

的面积。(FPGA/CPLD 中不同,主要是因为单元块的计算方式) 如何实现同步时序电路的延时?异步电路产生延时的一般方法是插入一个 Buffer、两级与非门等,这种延时调整手段是不适用同步时序设计思想

2020-09-01 11:04:22

设计中充分利用资源 ,因为 大部分 FPGA 器件都为时钟、复位、预置等信号提供特殊的全局布线资源,要充分利用这些资源。

6、在设计中 不论是控制信号还是地址总线信号、数据总线信号,都要采用另外的寄存器

2024-02-21 16:26:56

( Lut Levels )。因此,电路中用于实现组合逻辑的延时就是所有Tlut 的总和。在这里取Lut Levels = 4 。故Tlogic = 4 * Tlut 。 图( 2 ) FPGA

2018-08-21 09:46:15

FPGA中组合逻辑门占用资源过多怎么降低呢?有什么方法吗?

2023-04-23 14:31:17

引入到FPGA,或者将信号从FPGA传送到外部。

互连资源 (Interconnect Resources):互连资源是一种复杂的开关网络,它允许在FPGA中的不同逻辑块之间建立连接。用户可以通过编程来

2024-01-26 10:03:55

关于一个FPGA延时电路的设计,最大延时时间为被延迟信号的高电平时间

2016-11-10 19:29:43

)是两种不同的硬件实现方式。

FPGA是一种可编程逻辑器件,其内部资源可以根据需要进行配置和重新配置。这些资源包括但不限于:

逻辑单元(Logic Cells):这些是FPGA的核心计算资源,可以实现各种

2024-02-22 09:52:22

各位大神,小弟最近在做一个项目,由于之前选用的FPGA资源不够,现在需要将程序的资源占用率降下来。经过我的冥思苦想,也找不到好的方法,不知道各位大神平时工作中降低资源利用率的方法有哪些?求助啊!!!!

2015-04-04 00:32:57

数据的分析来诊断故障。因此,用于FPGA测试的仪器或系统的关键技术在于:如何加快单次配置的时间,以节省测试过程中的配置时间开销;如何实现自动重复配置和测试,将FPGA较快速度的在线配置和快速测试结合起来

2020-05-14 07:00:00

逻辑复制与资源共享本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》配套例程下载链接:http://pan.baidu.com/s/1pJ5bCtt 逻辑复制是一种通过增加面积来改善时序条件

2015-07-05 19:54:33

,实现性能的提升。电路实现的速度和消耗的面积是贯穿在FPGA开发过程中两个 矛盾的问题,综合约束是其中一种小范围内实现速度和面见平衡点移动的方式。FPGA开发—位置约束没错,你又想对了,位置约束和我

2017-11-22 09:34:02

1. 面积与速度的平衡与互换这里的面积指一个设计消耗 FPGA/CPLD 的逻辑资源的数量,对于 FPGA 可以用消耗的 FF(触发器)和 LUT(查找表)来衡量,更一般的衡量方式可以用设计所

2020-09-25 11:45:18

请问FPGA的资源使用如何评估?

2024-02-22 09:55:53

FPGA设计中电源管理过去,FPGA 设计者主要关心时序和面积使用率问题。但随着FPGA 不断取代ASSP 和ASIC器件计者们现正期望能够开发低功耗设计,在设计流程早期就能对功耗进行正确估算,以及

2012-08-11 16:17:08

信号需在电源稳定后经过一定的延时才能撤销,FPGA的复位信号需保证正确、稳定、可靠。在FPGA的设计中,多数情况下复位电路的功能虽能够正常完成,但电路并未得到精确合理的设计,仍存在可靠性设计缺陷。为

2021-06-30 07:00:00

D触发器,而一个门即可实现一个2输入与非门,所以一般来说,同步时序电路比异步电路占用更大的面积。(FPGA/CPLD中不同,主要是因为单元块的计算方式)如何实现同步时序电路的延时?异步电路产生延时

2021-07-04 14:16:15

一般来说,同步时序电路比异步电路占用更大的面积。(FPGA/CPLD中不同,主要是因为单元块的计算方式)如何实现同步时序电路的延时?异步电路产生延时的一般方法是插入一个Buffer、两级与非门等,这种

2021-07-13 15:36:00

触发器,而一个门即可实现一个2输入与非门,所以一般来说,同步时序电路比异步电路占用更大的面积。(FPGA/CPLD中不同,主要是因为单元块的计算方式)如何实现同步时序电路的延时?异步电路产生延时的一般

2021-07-25 11:09:06

触发器,而一个门即可实现一个2输入与非门,所以一般来说,同步时序电路比异步电路占用更大的面积。(FPGA/CPLD中不同,主要是因为单元块的计算方式)如何实现同步时序电路的延时?异步电路产生延时的一般

2021-07-26 14:47:48

触发器,而一个门即可实现一个2输入与非门,所以一般来说,同步时序电路比异步电路占用更大的面积。(FPGA/CPLD中不同,主要是因为单元块的计算方式)如何实现同步时序电路的延时?异步电路产生延时的一般

2021-11-22 10:04:03

D触发器,而一个门即可实现一个2输入与非门,所以一般来说,同步时序电路比异步电路占用更大的面积。(FPGA/CPLD中不同,主要是因为单元块的计算方式)如何实现同步时序电路的延时?异步电路产生延时

2021-07-09 14:24:42

触发器,而一个门即可实现一个2输入与非门,所以一般来说,同步时序电路比异步电路占用更大的面积。(FPGA/CPLD中不同,主要是因为单元块的计算方式)如何实现同步时序电路的延时?异步电路产生延时的一般

2021-07-09 14:34:18

触发器,而一个门即可实现一个2输入与非门,所以一般来说,同步时序电路比异步电路占用更大的面积。(FPGA/CPLD中不同,主要是因为单元块的计算方式)如何实现同步时序电路的延时?异步电路产生延时的一般

2021-08-10 14:51:33

触发器,而一个门即可实现一个2输入与非门,所以一般来说,同步时序电路比异步电路占用更大的面积。(FPGA/CPLD中不同,主要是因为单元块的计算方式)如何实现同步时序电路的延时?异步电路产生延时的一般

2020-08-02 10:45:07

本帖最后由 eehome 于 2013-1-5 10:03 编辑

fpga实现滤波器在利用FPGA实现数字信号处理方面,分布式算法发挥着关键作用,与传统的乘加结构相比,具有并行处理的高效性特点

2012-08-11 18:27:41

fpga实现滤波器fpga实现滤波器在利用FPGA实现数字信号处理方面,分布式算法发挥着关键作用,与传统的乘加结构相比,具有并行处理的高效性特点。本文研究了一种16阶FIR滤波器的FPGA设计方法

2012-08-12 11:50:16

小白求问下,如图这种的计数延时,里面的计数器,D触发器,门在编写时有相应的模块么?还是只能用语言写

补充内容 (2017-1-7 16:40):

左上角也是clk,signal是脉冲信号,D模块

2017-01-05 16:25:18

本帖最后由 upmcu 于 2012-7-28 15:07 编辑

截图:FPGA控制实现图像系统视频图像采集.pdfFPGA在多制式视频转换系统中的应用.pdfFPGA在图象处理中

2012-07-28 14:28:52

帮助找到延时最长的关键路径,以便设计者改进设计。对于结构固定的设计,关键路径法是进行速度优化的首选方法,可与其他方法配合使用。 在FPGA设计中,面积优化实质上就是资源利用优化,面积优化有多种实现方法

2008-06-26 16:16:11

本帖最后由 eaglewgliu2 于 2014-2-10 09:20 编辑1.项目背景使用FPGA实现一个14X14的信号切换矩阵,有输入14组、输出14组共28组信号,每组信号为一组BT1120

2014-02-10 16:08:02

ucos中利用OSMboxPendant()/OSMboxPost()是不是比 OSSemPend()/OSSemPost()消耗更多的系统资源?

2019-04-23 06:11:03

项目名称:FPGA PCIe信号拆分应用领域:计算机参赛计划:利用FPGA的并行资源,实现在不使用plx硬核芯片的情况下对PCIe信号的拆分。具体有效带宽视开发板资源而定。使用FPGA相较于使用硬核

2021-05-12 18:05:46

,此时只受限于芯片内块RAM 的数量,而不再受上面两条原则约束。5. 丰富的布线资源布线资源连通 FPGA 内部的所有单元,而连线的长度和工艺决定着信号在连线上的驱动能力和传输速度。FPGA 芯片内部

2012-03-08 11:03:49

把握DCM、PLL、PMCD和MMCM知识是稳健可靠的时钟设计策略的基础。赛灵思在其FPGA中提供了丰富的时钟资源,大多数设计人员在他们的FPGA设计中或多或少都会用到。不过对FPGA设计新手来说

2020-04-25 07:00:00

的CPU资源,导致程序的响应速度慢,很多信号来不及处理,导致控制异常。各位有经验的把你们的经验分享下,大家也可以讨论一下,在实际项目中,你们是如何处理这样的问题呢?有什么技巧吗?另加说明:在一个程序中,有的程序可以放在中断中执行,可是比如矩阵键盘怎么办?矩阵键盘的去抖延时如何实现?

2016-12-12 16:14:12

的面积。(FPGA/CPLD 中不同,主要是因为单元块的计算方式) 如何实现同步时序电路的延时? 异步电路产生延时的一般方法是插入一个 Buffer,两级与非门等。这种延时调整手段是不适用同步时序

2020-01-01 08:00:00

器件中的重要创新之一,2D NoC 为 FPGA 设计提供了几项重要优势,包括:· 提高设计的性能,让 FPGA 内部的数据传输不再成为瓶颈。· 节省 FPGA 可编程逻辑资源,简化逻辑设计,由

2020-09-07 15:25:33

转换器选用TI公司的ADS5500,具有14 b的分辨率和125 MSPS的最高采样率,用来对输入LFM信号进行60 MHz的高速采样。 数字脉冲压缩模块在FPGA中实现,FPGA选用Xilinx

2018-11-09 15:53:22

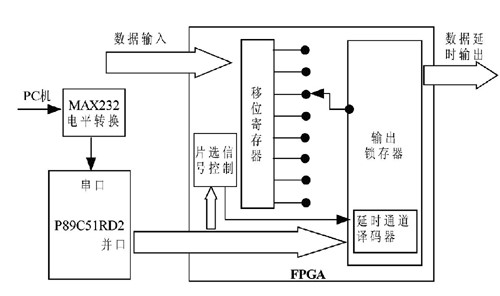

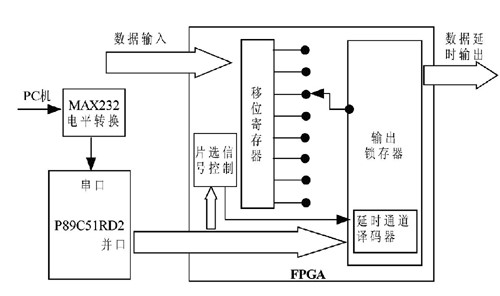

,通过PC机的串口发新数据,P89C51RD2中断收到新数据后,将数据分成两路处理:一路进入到单片机的数据存储区,待下次上电读取使用;另一路则转发至由FPGA控制的延时控制,实现信号的延迟时间调整

2019-09-25 07:27:21

滤波器和变系数FIR滤波器。常系数FIR滤波器的系数固定不变,可根据其特点采用分布式算法进行设计,故实现起来速度快,消耗的资源少。变系数FIR滤波器的系数是不断变化的。当前含有变系数FIR滤波环节的芯片

2019-07-30 07:22:48

的布线资源,对于资源占用很高的设计有效地降低布局布线拥塞的风险。实现真正的模块化设计,减小FPGA设计人员调试的工作量。本文用了一个具体的FPGA设计案例,来体现上面提到的NoC在FPGA设计中的几项

2020-10-20 09:54:00

FFT算法的实现为了提高FFT工作频率和节省FPGA资源,采用3级流水线结构实现64点的FFT运算。流水线处理器的结构如图2所示。每级均由延时单元、转接器(SW)、蝶形运算和旋转因子乘法4个模块组成

2019-06-17 09:01:35

把握DCM、PLL、PMCD和MMCM知识是稳健可靠的时钟设计策略的基础。赛灵思在其FPGA中提供了丰富的时钟资源,大多数设计人员在他们的FPGA设计中或多或少都会用到。不过对FPGA设计新手来说,什么时候用DCM、PLL、PMCD和MMCM四大类型中的哪一种,让他们颇为困惑。

2019-09-18 08:26:21

消耗的资源是否会很大?有没有更好的方法?另外假定设置读取超时为10s,那么这10s时间内程序一直处于读取串口状态吗?

2018-04-25 15:14:53

了使用。 Total combinaTIonal funcTIons 21612/24624(88%): 该芯片的24624个LE资源中,88%用于实现组合逻辑。 Dedicated logic

2019-06-17 09:03:28

的总线,走lvcmos电平.后来朋友告述我说使用这种信号不要超过50M,否则延时很难控制.高速总线信号应该选用带serdes(就是lvds电平+串并转换)的fpga,否则布线和内部延时都很难控制.好彩

2012-11-02 17:47:47

运算作为数字信号处理中最常见的运算之一,各大EDA软件都带有免费的浮点运算IP核。通过对IP核的生成和例化来实现浮点运算,把FPGA设计者从繁重的代码编写中解脱了出来,同时可以对IP核进行功能剪裁

2019-08-29 06:50:37

在设计中, 往往需要对某个信号做一定(任意长)的延时, 有没有好的方法来实现?而不是采用类似移位寄存器的方法来延时.

2019-09-19 04:23:21

哪位高手用Verilog HDL语言能实现2FSK、QPSK 、QAM信号的产生? 然后下载到FPGA中能实现?能分享一下源代码?刚入手还有好多不懂的地方,请多指教!!谢谢你们的帮助! 方便的话可以把打码发到我的QQ:2285341033邮箱里!不胜感激!!!

2015-06-29 22:03:28

现在要做FPGA控制ADS8344E这个芯片,实现A/D转换。可是看完时序图之后不知道该怎么下手,特别是需要延时的地方,应该用状态机实现延时还是其他方法?请各位前辈不吝赐教。

2016-11-23 22:23:29

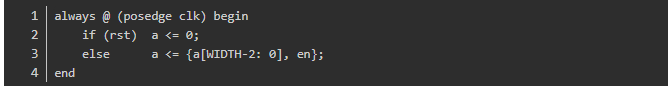

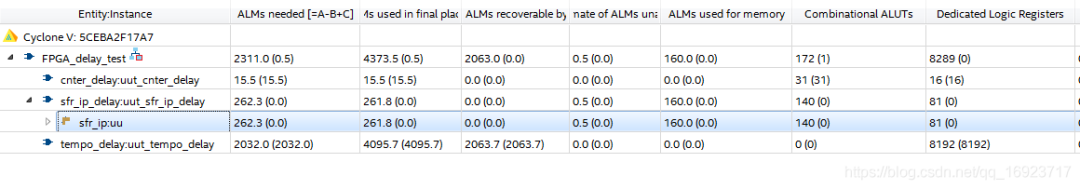

今天和大侠简单聊一聊FPGA设计中不同设计方法硬件资源消耗对比,话不多说,上货。

在这里,我们使用Verilog HDL 设计计数器,通过两种不同的写法,对比资源消耗。计数器实现的功能是计数记到24

2023-05-31 17:25:21

和变系数FIR滤波器。常系数FIR滤波器的系数固定不变,可根据其特点采用分布式算法进行设计,故实现起来速度快,消耗的资源少。变系数FIR滤波器的系数是不断变化的。当前含有变系数FIR滤波环节的芯片普遍存在速度与处理级数的矛盾,有效解决此问题具有重要的现实意义。

2019-07-29 06:08:14

sigmadsp中希尔伯特模块怎么实现调相位?相位可以换算成时间么?也就是,可以通过调相位使信号达到延时效果么?

如上图,我在外部设置一个调节参数,1800000000,可以调节cos和sin

2023-11-28 07:41:39

本文介绍了自适应滤波器的实现方法,给出了基于LMS 算法自适应滤波器在FPGA 中的实现,简单介绍了这种实现方法的各个功能模块,主要包括输入信号的延时输出模块、控制模块

2009-09-14 15:51:00 34

34 基于FPGA的DDS信号源设计与实现

利用DDS和 FPGA 技术设计一种信号发生器.介绍了该信号发生器的工作原理、 设计思路及实现方法.在 FPGA 器件上实现了基于 DDS技

2010-02-11 08:48:05 223

223 高精度的乘除法和开方等数学运算在FPGA实现中往往要消耗大量专用乘法器和逻辑资源。在资源敏感而计算时延要求较低的应用中,以处理时间换取资源的串行运算方法具有广泛的应

2010-07-28 18:05:14 37

37 摘要: 提出了一种采用现场可编程门阵列(FPGA)实现基带信号成形的FIR数字滤波器硬件电路的方案。该方案基于分布式算法的思想,利用FPGA丰富的查找表资源,从

2009-06-20 14:07:44 1086

1086

为利用简单的线缆收发器,实现中等数据率的串行数据传输,提出了一种基于电荷泵式PLL的时钟数据恢复的方法。鉴相器由FPGA实现,用固定延时单元构成一条等间隔的延时链,将输入信号经过每级延时单元后的多个输出用本地的VCO时钟锁存,输入信号的沿变在延时链

2011-03-15 12:39:34 90

90 本文提出基于FPGA的数字收发机信号处理研究与实现

2011-11-01 18:20:42 50

50 本书共分8章,主要内容包括典型fpga器件的介绍、vhdl硬件描述语言、fpga设计中常用软件简介、用fpga实现数字信号处理的数据规划、多种结构类型的fir数字滤波器的fpga实现、不同结构

2011-11-04 15:50:12 0

0 基于FPGA数字信号处理,本文主要探讨了基于FPGA数字信号处理的实现

2015-10-30 10:39:38 30

30 本书比较全面地阐述了fpga在数字信号处理中的应用问题。本书共分8章,主要内容包括典型fpga器件的介绍、vhdl硬件描述语言、fpga设计中常用软件简介、用fpga实现数字信号处理的数据规划、多种

2015-12-23 11:07:46 44

44 数字信号处理的FPGA实现

2016-12-14 22:08:25 32

32 一种低硬件资源消耗快速SVPWM算法_齐昕

2017-01-07 17:16:23 0

0 如何正确使用FPGA的时钟资源

2017-01-18 20:39:13 22

22 在嵌入式系统中,延时是经常需要使用的一种手段,延时的方法可以通过使用类似于NOP的指令来实现,但是如果延时的时间比较 长,如果使用太多的NOP指令则会消耗过多的储存空间,最好的方法是使用子程序

2017-10-18 16:32:17 0

0 在雷达、通信电子设备的设计中经常需要对电信号进行长延时,电延迟线由于材料尺寸限制很难实现长延时,虽然,近年来声表面波延迟线由于结构简单、体积小的特点在雷达、通信等电子系统中能够取代电缆延迟线,但是

2017-11-04 10:16:24 5

5 ,主FPGA实现捕获控制和快速解跳解扩,其余N片FPGA实现码片以下时间差的精细搜索和相干累积。针对信号体制和捕获性能需求,所有芯片均采用Xilinx公司的基于RAM的XQR4VFX系列。本设计解决了单片宇航级FPGA资源受限条件下复杂捕获问题,具有FPGA配置文件数目少、成本低、功耗低的优点。

2017-11-16 15:11:09 1348

1348

布线资源连通FPGA内部的所有单元,而连线的长度和工艺决定着信号在连线上的驱动能力和传输速度。FPGA芯片内部有着丰富的布线资源,根据工艺、长度、宽度和分布位置的不同而划分为4类不同的类别。第一类

2017-12-05 11:48:44 8

8 本文档内容介绍了基于fpga实现信号发生器,供参考

2018-04-20 15:23:35 65

65 通过Storyboard 创建视图对象时,其资源消耗会比直接通过代码创建对象要大非常多,在性能敏感的界面里,storyboard不是一个好的技术选择。

2018-05-16 17:48:58 4170

4170

基于P89C51RD2和FPGA的信号延时模块主要用在传输时钟信号、数字同步信号等对信号延迟有高要求的点对点传输系统中,它可对多路信号进行单独的适当延时调整。造成信号的延迟原因有:不同的传输线路、信号处理时间不同以及器件速度存在差异等。

2019-04-22 08:19:00 2898

2898

资源。为简化设计,降低硬件资源开销,可以在FPGA中利用IP核实现的嵌入式微处理器来对串口数据进行处理。

2019-08-02 08:08:00 3816

3816 在使用FPGA过程中,通常需要对资源做出评估,下面简单谈谈如何评估FPGA的资源。

2019-02-15 15:09:05 3580

3580 在使用 FPGA 过程中,通常需要对资源做出评估,下面简单谈谈如何评估 FPGA 的资源。 FF 和 LUT 的数目:这个在写出具体代码之前,初学者通常没法估算,但资深 FPGA 工程师会估算

2020-12-28 07:59:00 8

8 本文档的主要内容详细介绍的是如何使用Xilinx的FPGA对高速PCB信号实现优化设计。

2021-01-13 17:00:59 25

25 通过FPGA(现场可编程门阵列)时序模型分析得出FPGA门延时的方案,综合利用FPGA各种布局布线EDA工具,摸索出一套人工干预FPGA布局布线的方法,使FPGA门延时能够有效地用于时序调整,调整精度可达到纳秒级。该方法具有不增加任何额外器件,成本低、高效方便的特点。

2021-01-26 16:22:00 13

13 (5,3)整数小波变换的算法,接着阐述了一种多级二维(5,3)整数小波变换的FPGA实现结构,最后给出了硬件资源消耗、最大时钟频率和功能测试结果等FPGA实现结果。为了提高系统的处理速度,降低系统的资源消耗,本设计采用了参数可配置、共享

2021-02-01 11:53:33 9

9 也被设计成支持非常高频率的信号。了解全局时钟的信号路径可以扩展对各种全局时钟资源的理解。全局时钟资源和网络由以下路径和组件组成: 时钟树和网络:GCLK 时钟区域 全局时钟缓冲器 1. 时钟树和网络:GCLK 7系列FPGA时钟树设计用于低偏差和低功

2021-03-22 10:09:58 11527

11527

数字信号处理的FPGA实现.第3版英文

2021-10-18 10:55:32 0

0 (06)FPGA资源评估1.1 目录1)目录2)FPGA简介3)Verilog HDL简介4)FPGA资源评估5)结语1.2 FPGA简介FPGA(Field Programmable Gate

2021-12-29 19:40:45 6

6 采用FPGA的CARRY4进位单元,每个CARRY4的COUT连接到下一个CARRY4的CIN,这样级联起来,形成延时链;每个COUT做为抽头输出到触发器,通过本地时钟进行数据采样。假定每个延时

2022-02-16 16:21:32 5595

5595

关于 FPGA 的 IO资源分析共分为三个系列进行具体阐述,分别为: IO资源:分析FPGA IO资源的电气特性; IO逻辑资源:分析FPGA的输入输出数据寄存器、DDR工作方式、可编程输入延时

2022-12-13 13:20:06 1099

1099 FPGA的BRAM和LUT等资源都是有限的,在FPGA开发过程中,可能经常遇到BRAM或者LUT资源不够用的情况。

2023-08-30 16:12:04 949

949

X为一个32-bit的数,那么 X+32 和 X+1,哪个消耗的资源更多?还是一样多?

2023-09-20 09:31:48 393

393

达到这个目标。 1.使用电子开关: 一种方法是使用电子开关来直接控制电路的通断。当开关关闭时,输入信号可以直接通过电路,从而使得输出信号无延时。这样做的好处是简单易行,且能够实现精确的无延时。 2.使用快速RC组件: 在RC延时电路中

2023-11-20 17:05:33 402

402

电子发烧友App

电子发烧友App

评论