一个有意思的题目。

X为一个32-bit的数,那么 X+32 和 X+1,哪个消耗的资源更多?还是一样多?

假如只允许用 LUT 实现

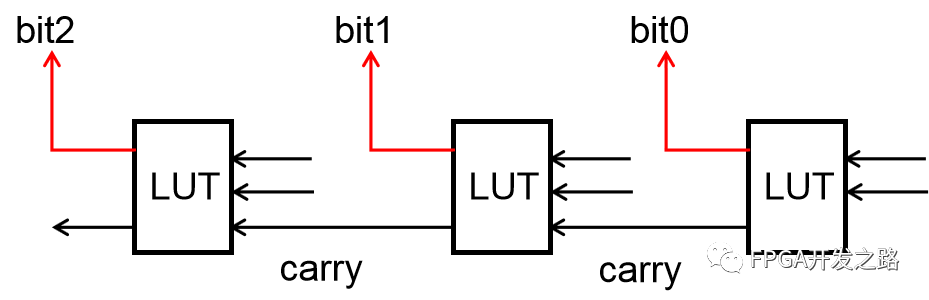

如图1所示每个LUT可以完成1bit的加法,同时产生进位(Xilinx LUT6可以有两个输出)。因此对于32bit的加法,则需要32个LUT。

图1

假如我们要实现的是 A+B,A和B都是32-bit的,那么确实是需要32个LUT。那X+32和X+1的常数加法呢?

32可以表示为32'b0000...0010_0000,1可以表示为32'b0000....0000_0001。

对于 X+32,输出值的低5bit可以直接表示为X[5:0],不需要LUT,其余值需要27个LUT实现加法运算。

对于X+1,只能从bit 0开始相加计算进位,总共需要32个LUT。

因此 X+1 消耗的资源更多。

假如是Vivado综合,即使用Carry8

对于32bit的加法,需要4个carry8,那么是否意味着 X+32 和 X+1 有相同的资源消耗呢?

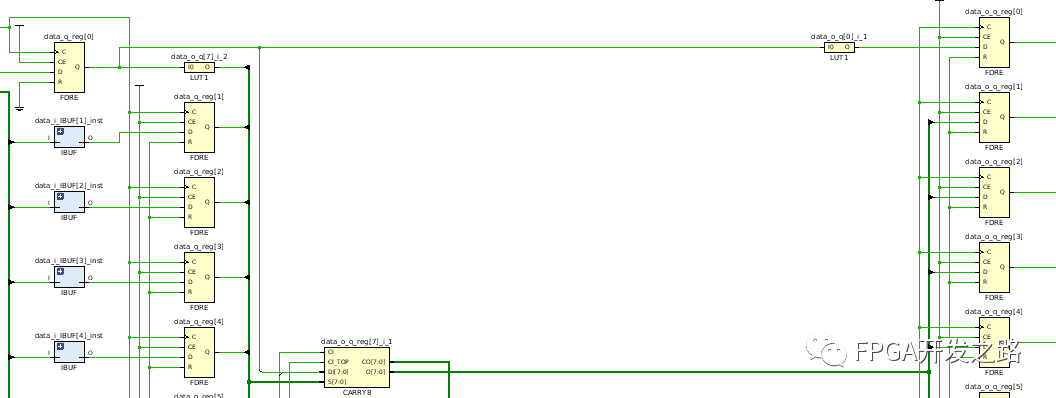

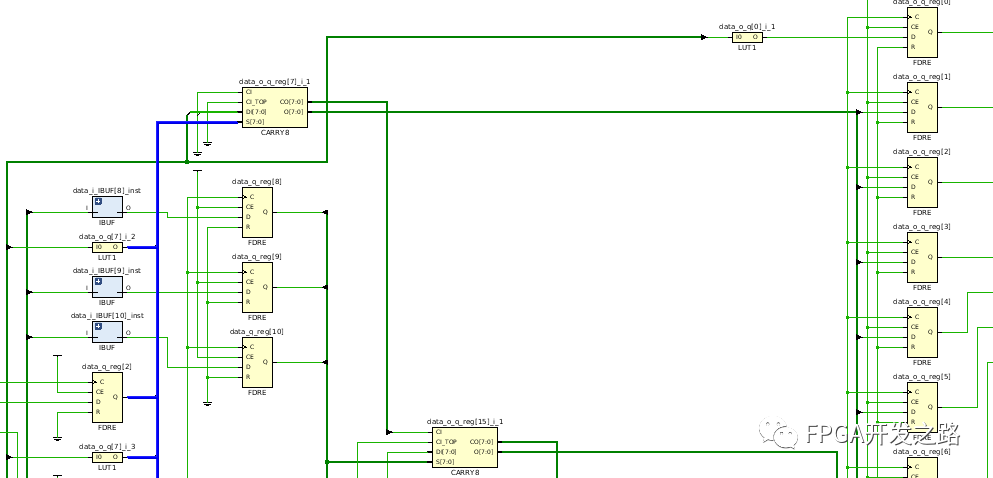

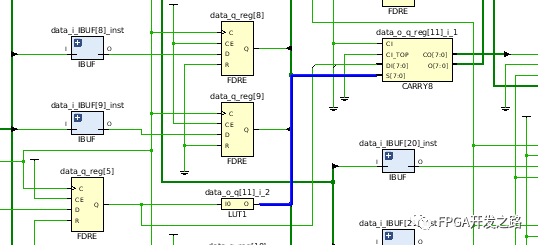

查看综合结果(如下图所示):

X+1 2个LUT1+4个Carry8 (LUT1实现的是取反的功能)

X+3 3个LUT1+4个Carry8 (bit0消耗2个LUT1,bit1消耗一个LUT1)

X+32 1个LUT1+4个Carry8 (bit5消耗1个LUT1)

因此从综合结果看仍然是 X+1消耗的资源更多。当然这仅仅考虑单个加法的结果,如果实际代码中,加法器前面还有组合逻辑,这个LUT1应该是会合并在前面的LUT中实现,因而X+1和X+32会得到相同的资源消耗,即4个Carry8。

感兴趣的读者可以思考下 X-32会消耗多少LUT。

图2 - X+1

图3 - X+3

图4 - X+32

审核编辑:汤梓红

-

FPGA

+关注

关注

1664文章

22509浏览量

639559 -

Xilinx

+关注

关注

73文章

2208浏览量

131979 -

LUT

+关注

关注

0文章

52浏览量

13205 -

运算

+关注

关注

0文章

132浏览量

26837 -

Vivado

+关注

关注

19文章

860浏览量

71428

原文标题:X+32 vs X+1 谁消耗的FPGA资源多

文章出处:【微信号:FPGA开发之路,微信公众号:FPGA开发之路】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

X+32和X+1谁消耗的FPGA资源多

X+32和X+1谁消耗的FPGA资源多

评论