声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

Xilinx

+关注

关注

73文章

2208浏览量

131976 -

Vivado

+关注

关注

19文章

860浏览量

71425

发布评论请先 登录

相关推荐

热点推荐

【RA-Eco-RA4M2开发板评测】+ 16*64点阵屏显示驱动

;IOPORT_CFG_CTRL, BSP_IO_PORT_01_PIN_14, BSP_IO_LEVEL_HIGH)

#define LR1_low R_IOPORT_PinWrite(&

发表于 04-20 21:07

Vivado时序约束中invert参数的作用和应用场景

在Vivado的时序约束中,-invert是用于控制信号极性的特殊参数,应用于时钟约束(Clock Constraints)和延迟约束(Delay Constraints)中,用于指定信号的有效边沿或逻辑极性。

AMD Vivado Design Suite 2025.2版本现已发布

AMD Vivado Design Suite 2025.2 版本现已发布,新增对 AMD Versal 自适应 SoC 的设计支持,包含新器件支持、QoR 功能及易用性增强。

vivado时序分析相关经验

vivado综合后时序为例主要是有两种原因导致:

1,太多的逻辑级

2,太高的扇出

分析时序违例的具体位置以及原因可以使用一些tcl命令方便快速得到路径信息

发表于 10-30 06:58

vcs和vivado联合仿真

我们在做参赛课题的过程中发现,上FPGA开发板跑系统时,有时需要添加vivado的ip核。但是vivado仿真比较慢,vcs也不能直接对添加了vivado ip核的soc系统进行仿真。在这种情况下

发表于 10-24 07:28

FPGA开发板vivado综合、下载程序问题汇总

在做vivado综合时和FPGA下载程序时,我们碰到以下问题,并找出了对应的解决方案。

1.could not open include file”e203_defines.v”问题

在做

发表于 10-24 07:12

Vivado中向FPGA的Flash烧录e203的方法

首先导入、并配置好项目,完成项目的综合(SYNTHESIS)与实现(IMPLEMENTATION),查看有无错误与或警告信息,调整完成后,右键比特流生成(Generate Bitstream),选择

发表于 10-23 08:28

【RA4M2-SENSOR】+手机控制RGB_LED彩灯变换

)

{

R_IOPORT_PinWrite(&g_ioport_ctrl, BSP_IO_PORT_00_PIN_02, BSP_IO_LEVEL_HIGH);

R_IOPORT_PinWrite

发表于 09-19 20:02

Vivado无法选中开发板的常见原因及解决方法

在使用 AMD Vivado Design Suite 对开发板(Evaluation Board)进行 FPGA 开发时,我们通常希望在创建工程时直接选择开发板,这样 Vivado 能够自动配置

如何使用One Spin检查AMD Vivado Design Suite Synth的结果

本文讲述了如何使用 One Spin 检查 AMD Vivado Design Suite Synth 的结果(以 Vivado 2024.2 为例)。

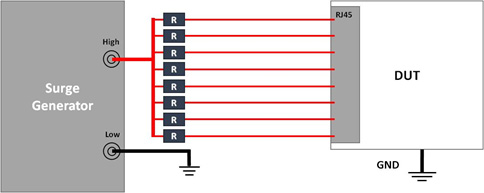

“System Level EOS Testing Method”可以翻译为: “系统级电性过应力测试方法”

“System Level EOS Testing Method”可以翻译为:

“系统级电性过应力测试方法”

Getting Started with Vivado High-Level Synthesis

Getting Started with Vivado High-Level Synthesis

评论