在需要多个FPGA芯片的应用中,如果JTAG链上所有FPGA采用相同配置,可以通过“成组”加载方式同时加载;

2023-02-20 10:18:27 8049

8049

通过FPGA的多重配置可以有效地精简控制结构的设计,同时可以用逻辑资源较少的FPGA器件实现需要很大资源才能实现的程序。以Virtex5系列开发板和配置存储器SPI FLASH为基础,从硬件电路

2014-01-24 14:17:22 16046

16046

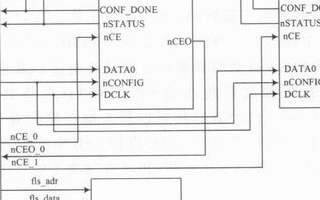

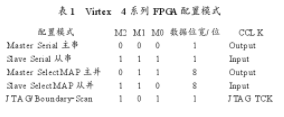

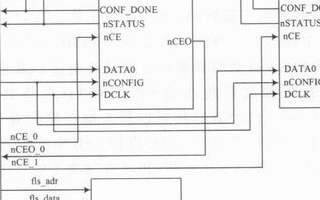

现场可编程门阵列(FPGA)作为专用集成电路(ASIC)领域的一种半定制电路,可以根据设计的需要灵活实现各种接口或者总线的输出,在设备端的通信产品中已得到越来越广泛的使用。##在设备端通信产品中,基于CPLD 的FPGA 从并加载框如图2 所示。

2015-01-30 16:54:39 3717

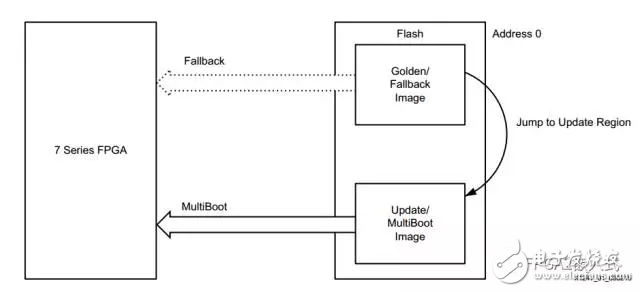

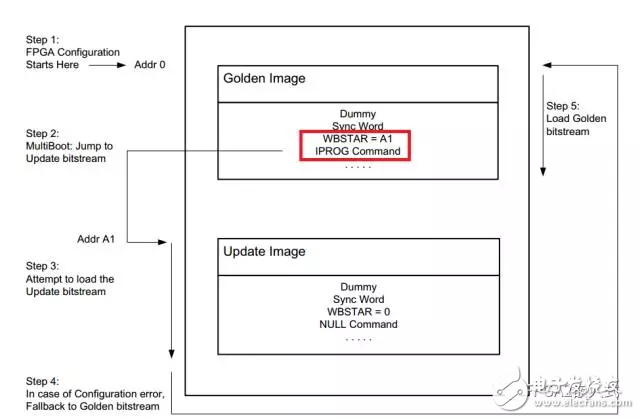

3717 当FPGA 完成上电自动加载初始化的比特流后,可以通过触发FPGA 内部的多重启动事件使得FPGA 从外部配置存储器(SPI FLASH)指定的地址自动下载一个新的比特流来重新配置。

2015-02-02 11:09:51 1629

1629

大多数FPGA芯片是基于 SRAM 的结构的, 而 SRAM 单元中的数据掉电就会丢失,因此系统上电后,必须要由配置电路将正确的配置数据加载到 SRAM 中,此后 FPGA 才能够正常的运行。

2019-07-01 17:16:45 17573

17573 目前,大多数FPGA芯片是基于 SRAM 的结构的, 而 SRAM 单元中的数据掉电就会丢失,因此系统上电后,必须要由配置电路将正确的配置数据加载到 SRAM 中,此后 FPGA 才能够正常的运行。

2022-10-24 14:52:00 1224

1224 目前,大多数 FPGA 芯片是基于 SRAM 的结构的, 而 SRAM 单元中的数据掉电就会丢失,因此系统上电后,必须要由配置电路将正确的配置数据加载到 SRAM 中,此后 FPGA 才能够正常

2022-12-26 18:10:00 3584

3584 在 FPGA 设计中,一个常见但略显繁琐的环节是:如何方便地将新的比特流加载到 FPGA。尤其是在没有专用 USB-JTAG/编程芯片或者在低成本板卡中,传统的编程方式可能需要额外硬件或较复杂流程。

2025-12-19 15:20:20 4388

4388

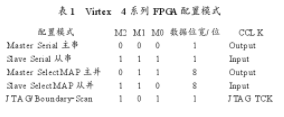

使用的FLASH](4)从并方式。即文章中探讨的FPGA 加载方案。2]以Xilinx 公司Spartan - 6 系列FPGA 为例,与从并加载相关的管脚如表1 所示。表1 从并加载管脚名称由表1

2019-07-12 07:00:09

是基于静态随机存储器(SRAM) 结构的,断电后程序丢失后的每次上电都需要重新加载程序。且随着FPGA 规模的升级,加载程序的容量也越来越大,如Xilinx 公司的Spartan - 6 系列中的6SLX150T,其

2019-06-14 06:00:00

使用Platform USB cable II通过JTAG加载程序。接口如下所示(我们还通过USB连接器为电路板供电)我们使用影响软件来刷新FPGA。JTAG初始化是正确的,如下图所示,但FPGA未检测到加载.bit文件。可能导致上述问题的原因是什么?问候HPC

2019-09-26 10:07:29

高电平状态。接我们单板的GPIO后,我们的FPGA无法正常加载,GPIO管脚从FPGA直连至板间连接器,断开连接器恢复正常。经过测试发现由于GPIO链接对端的高电平,导致我们的GPIO对应BANK

2020-06-12 13:54:15

前言操作环境:Windows 7 64bitISE 14.7 FPGA程序加载与固化将开发板通过Xilinx FPGA JTAG下载器连接到PC机,打开Windows的设备管理器查看下载器是否已正常

2020-09-25 09:57:45

1. 如何实现FPGA局部动态加载。2. pcie部分不变,实现部分程序加载。3. 目前是通过JTAG线,通过PCIE加载的FPGA程序。4. 现在是想通过更改bin文件,不通过JTAG的方式加载。

2021-03-08 09:32:33

请问FPGA逻辑加载方式有哪些?例如flash等

2024-01-26 10:05:13

多重通讯的挑战是什么?

2021-05-13 06:09:40

目前,大多数FPGA芯片是基于 SRAM 的结构的, 而 SRAM 单元中的数据掉电就会丢失,因此系统上电后,必须要由配置电路将正确的配置数据加载到 SRAM 中,此后 FPGA 才能够正常的运行

2019-07-18 08:10:11

本帖最后由 qwerasdzkk 于 2012-3-10 16:00 编辑

[hide]详解电容在实际电路中应用[/hide]

2012-03-08 09:47:24

学的知识怎样才能运用到实际中啊

2015-03-13 18:32:49

`1、引言在系统上电时,需要从外部载入所要运行的程序,此过程被称为程序加载。多数情况下,从外部专用的 读入程序。这种方式速度慢,而且只能加载固定的程序。显然,当系统需要容量大而且 FPGA要加载

2019-12-10 17:42:18

DAC3484输出的直流偏置每次FPGA加载时都会变化,为什么呢??当调好的offset的值后把它写死到DAC中后每次FPGA加载本振泄漏都会变,换句话说就是没次FPGA加载后都要调offset,不应该出现这种现象啊

希望大牛们给小弟解答,谢谢啊

2025-01-24 08:12:32

安路 EG4X FPGA 器件支持多种程序加载模式。本手册主要介绍从动串行(SS)加载模式以及从动串行级联加载模式的使用。内容包括使用从动串行加载模式的软件配置,使用从动串行加载模式和从动串行级联加载模式的硬件电路连接,另外包括 MCU 作为控制 FPGA 从动串行加载的主控器件时的软件工作流程。

2022-10-27 08:03:06

安路 EG4X FPGA 器件支持多种程序加载模式。本手册主要介绍从动并行(SP)加载模式以及从动并行级联加载模式的使用。内容包括使用从动并行加载模式的软件配置,使用从动并行加载模式和从动并行级联加载模式的硬件电路连接,另外包括 MCU 作为控制 FPGA 从动并行加载的主控器件时的软件工作流程。

2022-10-27 07:31:16

Verilog语言在FPGA中运用的简单实例有什么,求举例?

2016-03-16 00:59:00

用的FPGA是Sparten6系列的XC6SLX100T的FPGA,选用的FLASH是W25Q128的SPI模式FLASH,烧写程序大小大概25M,烧写完后上电启动,FPGA加载时长大概12秒,启动比较慢,烦请大佬看看什么原因造成的,有什么解决措施能提高启动时间?谢谢

2020-06-10 13:55:50

`Xilinx系列FPGA芯片IP核详解(完整高清书签版)`

2017-06-06 13:15:16

发现labview并不是想象中的那么容易,当然,也不会放弃,具体的不知道 labview 到底在现实中是怎么运用?现在自己也没机会接触这方面的工作,望前辈给些实例看看,自己也下载了很多的例子,但在实际中是怎么运用的就不是很清楚了。

2013-01-28 16:47:38

为什么采用FPGA去加载TigerSHARC DSP?如何去设计加载状态机?加载状态机有哪几个典型的加载过程?

2021-04-28 06:30:11

Altera系列FPGA芯片IP核详解

2016-08-19 17:24:48

卡尔曼滤波在四轴飞行器上的实际运用

2017-04-02 12:39:08

反熔丝FPGA在密码芯片设计中的运用

2012-08-17 10:37:41

大疆华为等企业fpga面试题详解视频。附件是网盘

2018-07-10 10:49:02

使用ICAP-spartan6发送比特流。任务是当我按下按钮1时,spartan6 FPGA加载黄金比特流,由LED指示灯闪烁表示。类似地,当我按下按钮2时,FPGA使用ICAP重新配置多引导比特流。请帮我解决这个问题。我有

2019-07-19 12:31:58

目前实现加载的方法通常有两种:一种是用专用Cable通过JTAG口进行数据加载,另一种是外挂与该FPGA厂商配套的PROM芯片。前者需要在PC机上运行专用的加载软件,直接下载到FPGA片内,所以掉电

2019-09-05 07:50:03

我正试图在a7 fpga中实现回退多重启动。以下是黄金图像的ise工具中的设置:当我完成将黄金图像位文件加载到fpga中时,完成的led可以点亮。但当我完成将黄金映像mcs文件加载到fpga中,并在

2020-06-01 06:17:37

目前实现加载的方法通常有两种:一种是用专用Cable通过JTAG口进行数据加载,另一种是外挂与该FPGA厂商配套的PROM芯片。前者需要在PC机上运行专用的加载软件,直接下载到FPGA片内,所以掉电

2019-10-11 06:15:28

请问一下有没有采用EEPROM对大容量FPGA芯片数据实现串行加载的实际方案?

2021-04-08 06:01:39

你好我正在使用ZC706板传输调制信号。我们以文本和mat格式的形式提供这些调制信号。我想将这些调制信号加载到FPGA中,所以有没有办法直接将数据加载到FPGA中,当我们生成.bit文件时,这些数据

2019-05-06 07:25:49

Altium designer在FPGA及嵌入式智能方面有哪些优势?怎样运用Altium Designer平台实现FPGA的嵌入式系统设计?

2021-04-28 07:05:33

需要将FPGA程序通过I2C或者RS232加载到FPGA内部,然后通过FPGA存储到SPI FLASH中,再次上电后从SPI FLASH加载。 这个过程中,有以下几个问题:1.怎样将.v文件转换成

2016-04-29 14:46:21

的闪存系列,但内存大小更大。我第一次使用MCS文件加载Flash时工作正常。然而,从那以后,我无法加载FPGA。空白检查表示设备不是空白,但擦除功能不起作用。此外,只是尝试通过IMPACT重新编程闪存也

2019-03-19 06:25:56

嗨,我正在使用斯巴达3e入门套件和ise 10.2软件。我无法将.bit文件加载到fpga中,因为iMPACT显示错误:写cmdbuffer失败20000015.write cmdbuffer失败20000015.Loopback测试失败。发送字符= 00,接收字符= 00.Cable连接失败。请帮忙。问候,阿希什

2019-08-29 10:47:39

嗨,我想用许多位文件对FPGA进行编程,即加载一个运行它的位文件并将其结果存储在一个文件中,然后加载下一个文件,依此类推N位文件。我遇到了多重启动,看起来像是我问题的解决方案。但在引用网络时,我发现

2020-04-06 13:23:51

如何用EEPROM对大容量FPGA芯片数据实现串行加载?如何设计并-串转换时序?

2021-04-29 07:13:12

各位前辈,FPGA采用并行加载方式,现CPLD外挂一片FLASH,要求用CPLD控制加载时序,从FLASH读取代码,送入FPGA,应该怎么用CPLD控制加载时序,程序应该怎么写,有可以参考的资料吗,谢谢各位了!

2013-02-21 12:07:34

多片fpga组成jtag链的时候如何加载?

2023-08-11 09:10:26

红芯FPGA开发板例程详解

2013-07-28 20:25:33

新手,求基于fpga的spi接口运用实例,小弟感激不尽

2016-01-12 11:06:13

的形状,serpitine shpae,经过了多少转。是的,我可以理解寄存器编程位,你只需要编程1和0来编程FPGA的配置但我无法想象程序如何转换,因此编程芯片并使最终的电线看起来像。软件如何控制实际

2019-04-15 14:17:53

实际的FPGA编程

2009-07-23 09:54:22 72

72 本文运用黑盒测试的基本理论,提出了FPGA逻辑设计的测试模型,分析了FPGA逻辑设计的基本方法和步骤,最后结合一个实际项目说明了FPGA逻辑设计的测试验证过程。关键词:黑盒

2009-08-19 09:12:41 9

9 实际运用中差分信号线的分析和LAYOUT随着近几年对速率的要求快速提高,新的总线协议不断的提出更高的速率。传统的总线协议已经不能够满足要求了。串行总线由于更好的抗干

2009-09-30 13:04:16 0

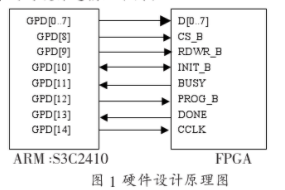

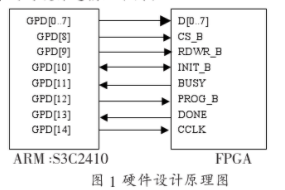

0 本文实现了一种基于ARM-Linux 的FPGA 程序加载方法,详细讨论了加载过程中各个阶段程序对配置管脚的操作,给出了硬件实现,编写了运行于ARM 处理器的嵌入式Linux上的驱动程序。

2009-12-19 16:26:26 31

31 基于ARM+FPGA的可重构控制器设计及其在加载系统中的应用:文章提出了一种基于ARM+FPGA结构的可重构控制嚣的设计方法.并采用此方法开发了用于加载系统的2通道电液伺服控制器

2010-03-02 12:03:21 29

29 汽车电子中的DSP和FPGA运用

1 引言

20世纪末,全球范围内兴起的信息革命浪潮,为汽车工业的突破性发展提供了千载难逢的机遇,信息

2010-03-03 11:10:28 564

564 介绍了一种基于SRAM技术的FPGA可编程逻辑器件的编程方法,能在系统复位或上电时自动对器件编程。有效地解决了基于SRAM的FPGA器件掉电易失性问题,针对当前系统规模的日益增大,本文提出了一种用单片机对多片FPGA自动加载配置的解决方案.

2011-03-15 16:41:22 21

21 根据FPGA芯片加载时序分析,本文提出了采用通过市面上常见的Flash ROM芯片替代专用PROM的方式,通过DSP的外部高速总线进行FPGA加载;既节约了系统成本,也能达到FPGA上电迅速加载的目的

2011-08-16 16:26:14 2130

2130

3 FPGA设计流程 完整的FPGA 设计流程包括逻辑电路设计输入、功能仿真、综合及时序分析、实现、加载配置、调试。FPGA 配置就是将特定的应用程序设计按FPGA设计流程转化为数据位流加载

2013-01-16 11:52:22 16

16 异步FIFO在FPGA与DSP通信中的运用

2016-05-19 11:17:11 0

0 一、类加载器 类加载器(ClassLoader),顾名思义,即加载类的东西。在我们使用一个类之前,JVM需要先将该类的字节码文件(.class文件)从磁盘、网络或其他来源加载到内存中,并对字节码进行

2017-09-27 14:27:21 0

0 本文主要介绍如何在浏览器和Node之中加载ES6模块,以及实际开发中经常遇到的一些问题(比如循环加载)。 浏览器加载 传统方法 在HTML网页中,浏览器通过 《!-- 页面内嵌的脚本

2017-09-28 14:26:33 0

0 工作效率。通过FPGA 的多重配置可以有效地精简控制结构的设计,同时可以用逻辑资源较少的FPGA 器件实现需要很大资源才能实现的程序。以Virtex5系列开发板和配置存储器SPIFLASH为基础,从硬件电路和软件设计两个方面对多重配置进行分析,给出了多

2017-10-12 17:57:08 16

16 基于异步FIFO在FPGA与DSP通信中的运用

2017-10-19 10:30:56 10

10 满足设计需求。FPGA的多重加载可以解决可编程资源不足的难题。FPGA多重加载是将设计的多个模式的比特文件存储到Flash,用户可以根据需要选择加载不同模式的比特文件。FPGA的多重加载解决了可编程资源不足的问题,提高了FPGA可编程资源的利用率。

2017-11-18 04:41:50 8770

8770

本文档内容介绍了GD32单片机程序分散加载的方法,图像详解,供参考。

2017-11-22 11:02:01 39

39 多重通讯装置结构设计 (Device’s Architecture),芯片的底层结构设计 (Underlying Chipset Architecture), 软件驱动和编写测试软件的灵考能力;所以

2017-12-08 08:13:24 1734

1734

本文档内容介绍了基于xilinxFPGA选型详解,供参考查阅

2018-03-15 15:58:01 4

4 、ISDN PRI等领域的加密,将会有数兆或数十兆以上的速度要求,所以硬件加密将是今后首选的加密手段。目前运用的硬件加解密,大都采用SRAM型的FPGA实现,必须外挂一EEPROM存储加载FPGA的数据

2018-08-05 10:22:50 10368

10368 29张图详解PLC技术的实际应用,PLC技术的实际案例汇总。

2018-08-25 10:11:18 16919

16919 Xilinx 公司Virtex5 系列的FPGA 具有多重配置的特性,允许用户在不掉电重启的情况下,根据不同时刻的需求,可以从FLASH 中贮存的多个比特文件选择加载其中的一个,实现系统功能的变换。

2018-12-04 08:37:00 6255

6255

FPGA 的配置数据通常存放在系统中的存储器件中,上电后控制器读取存储器中的bit 文件并加载到FPGA 中,配置方式有JTAG、从并、从串、主从4 种,不同厂家叫法不同,但实现方式基本都是一样的。

2018-10-30 08:58:00 9336

9336

FPGA有多种配置/加载方式。粗略可以分为主动和被动两种。主动加载是指由FPGA控制配置流程,被动加载是指FPGA仅仅被动接收配置数据。

2018-10-05 10:12:00 19146

19146 可编程的双重优点,被广泛应用于通信领域中。FPGA在上电后,需要加载配置文件对内部各功能模块进行初始化,而配置文件加载的效率直接影响系统的初始化时间。因此如何设计一种高效的FPGA加载方案,是通信系统设计中的一个重要环节。

2019-02-19 14:49:08 2849

2849

加载系统。该系统通过USB芯片将PC中的配置文件传送给CPLD,CPLD再将其写入FLASH芯片,FLASH芯片可以长久地存储配置文件。这样FPGA每次上电后CPLD将FLASH中的配置文件读出来配置

2019-02-20 15:36:23 3797

3797

在系统上电时,需要从外部载入所要运行的程序,此过程被称为程序加载。多数情况下,从外部专用的 读入程序。这种方式速度慢,而且只能加载固定的程序。显然,当系统需要容量大而且 FPGA要加载的程序可以

2019-03-22 16:20:14 1470

1470 本设计采用FPGA技术,在FPGA中实现8051单片机的软核,将外部SPI Flash中的代码数据加载到FPGA内部ram,然后复位 MC8051,实现外部flash启动MC8051。

2019-06-11 17:47:00 3

3 FPGA是基于SRAM编程的,编程信息在系统掉电时会丢失,每次上电时,都需要从器件外部的FLASH或EEPROM中存储的编程数据重现写入内部的SRAM中。FPGA在线加载需要有CPU的帮助,并且在加载前CPU已经启动并工作。FPGA的加载模式主要有以下几种:

2020-04-07 08:00:00 16

16 FPGA在系统上电时,需要从外部载入所要运行的程序,此过程被称为程序加载。多数情况下,FPGA从外部专用的 EPROM读入程序。这种方式速度慢,而且只能加载固定的程序。显然,当系统需要容量大而且

2020-08-13 17:16:46 2922

2922

基于SRAM结构的FPGA容量大,可重复操作,应用相当广泛;但其结构类似于SRAM,掉电后数据丢失,因此每次上电时都需重新加载。

2021-03-26 13:52:58 6318

6318

(UG332) 即为《Spartan-3 系列配置用户指南》 在此用户指南中,并未涵盖有关从 SPI 闪存启动时,如何使用内部配置访问端口 (ICAP) 来支持在 Spartan-3AN FPGA

2021-06-25 17:25:26 2513

2513 浅谈光伏并网柜的实际运用(实用开关电源技术)-浅谈光伏并网柜的实际运用

2021-09-23 17:38:14 15

15 FPGA-DCM使用详解(通信电源技术期刊编辑部电话)-该文档为FPGA-DCM使用详解文档,是一份还算不错的参考文档,感兴趣的可以下载看看,,,,,,,,,,,,,,,,

2021-09-28 11:22:17 6

6 【正点原子FPGA连载】第三章 硬件资源详解 -摘自【正点原子】新起点之FPGA开发指南_V2.1

2021-11-21 14:06:03 19

19 因为在S6或者其他7系列的FPGA中,是有一套非常成熟的FPGA加载机制(Xilinx有很详细的指导手册),但是来到Zynq时代,这个方式变了。为什么呢?因为现在zynq上有ARM了,所有的加载工作实际上可以借由ARM来实现

2022-05-09 10:53:02 4441

4441 电子发烧友网站提供《安路EG4X FPGA从动串行加载模式.pdf》资料免费下载

2022-09-27 10:55:18 2

2 电子发烧友网站提供《安路EG4X FPGA从动并行加载模式.pdf》资料免费下载

2022-09-27 10:44:27 1

1 在不带内置ARM核的AMD FPGA产品系列中,FPGA的程序加载方式并没有发生大的变化

2023-07-07 14:14:58 4513

4513

前言本指导文档适用的开发环境为Windows764bit和Windows1064bit。本文档的主要内容为基于ISE的FPGA程序加载、固化等说明。进行本文档操作前,请先按照调试工具安装相关文档

2022-08-25 16:26:05 0

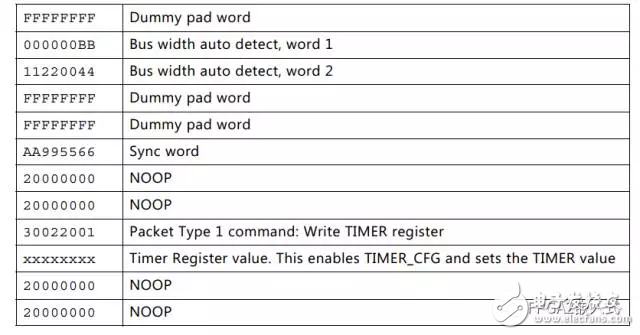

0 AMD FPGA在配置了适当的启动模式后,上电即会按该模式去加载配置文件。以7系列FPGA为例,假设设置模式引脚M[2:0]=3’b001,上电后FPGA会以Master SPI方式尝试从FLASH加载配置文件,其与工程是否含有MicroBlaze IP无关。

2024-04-25 12:49:14 1406

1406

电子发烧友App

电子发烧友App

评论