这些 SoC FPGA 完善了十多年以来的软核 CPU 以及其他软核 IP。各种技术、商业和市场因素相结合推动了这一关键点的出现,Altera、Cypress 半导体、Intel 和 Xilinx 公司等供应商都发布或者开始发售 SoC FPGA 器件

2011-03-12 11:24:50 1196

1196

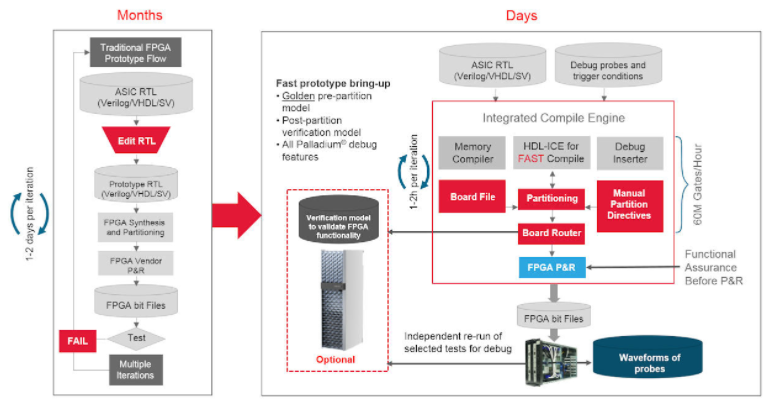

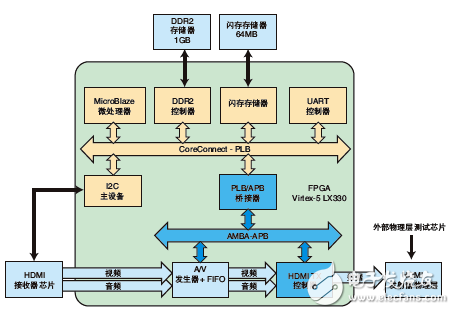

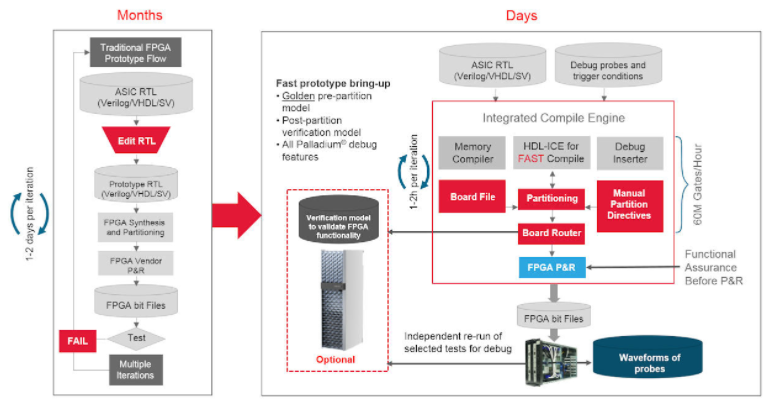

基于 FPGA 的 ASIC 原型可快速、准确地实现 SoC 系统建模和验证并加速软件和固件的开发。Xilinx 推出Virtex®-7 2000T 器件,使基于 FPGA 的原型得到了进一步发展

2013-03-14 14:33:00 2541

2541

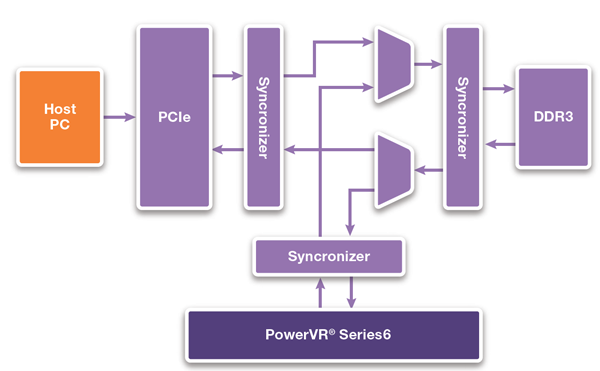

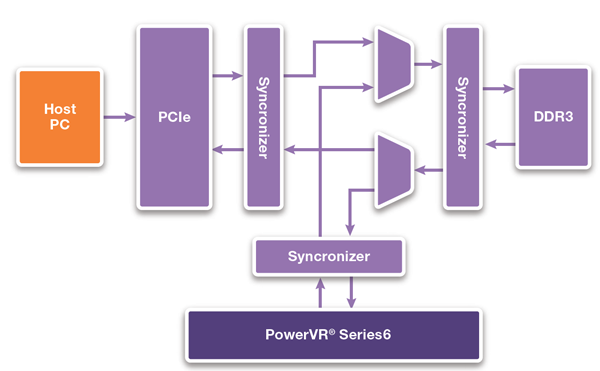

Synopsys所做的第一步是启动一个概念验证项目。这个项目为Imagination的PowerVR Series6 GPU展示了基于FPGA的原型设计。

2015-06-24 09:47:00 2022

2022

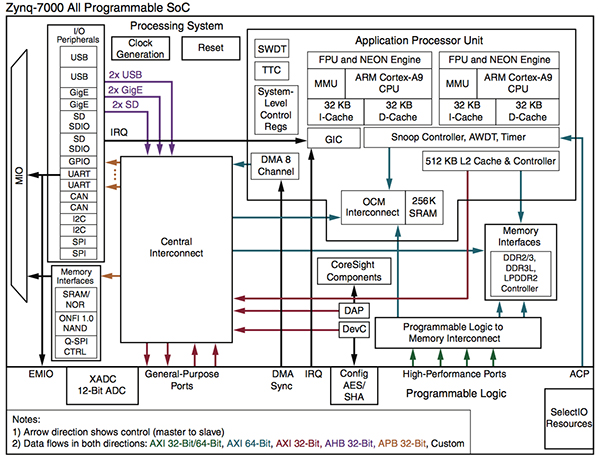

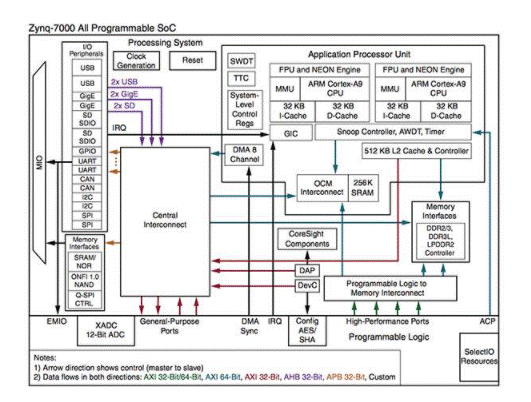

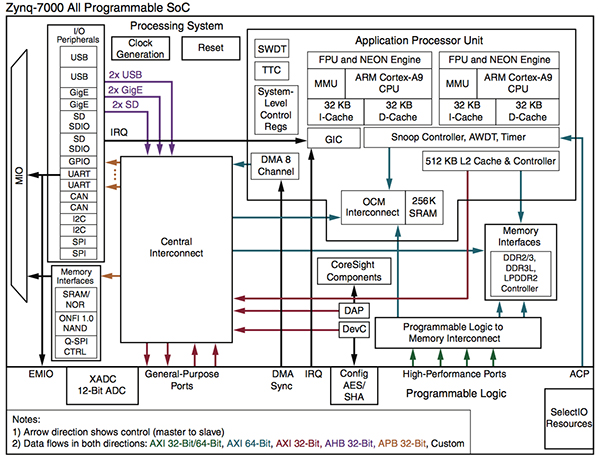

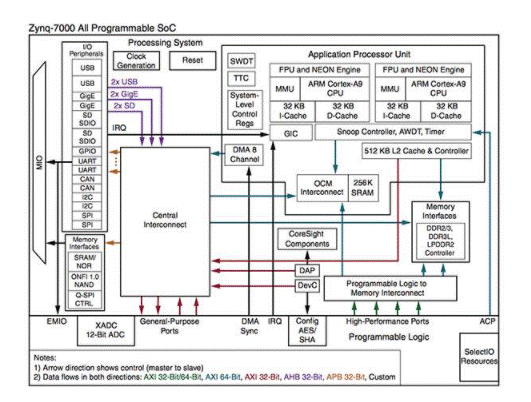

MCU对应用优势的挑战已经开始。具有片上固定功能处理子系统(即片上系统(SoC)FPGA)的现场可编程逻辑器件(FPGA)最近已成为高端处理应用的潜在竞争者。这提出了一个问题:随着应用性能要求

2019-02-19 08:38:00 17500

17500

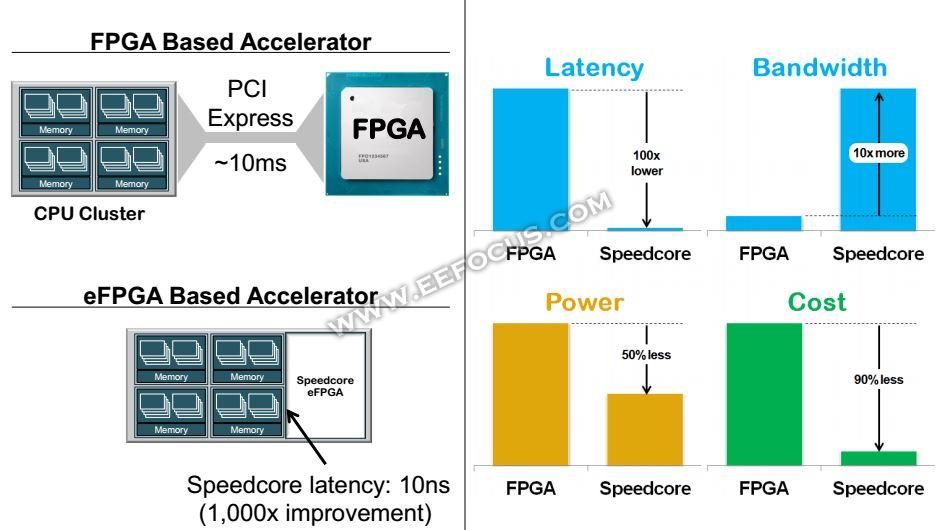

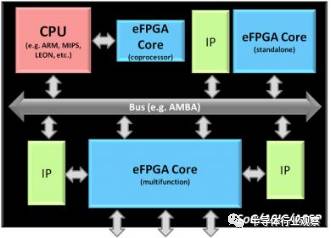

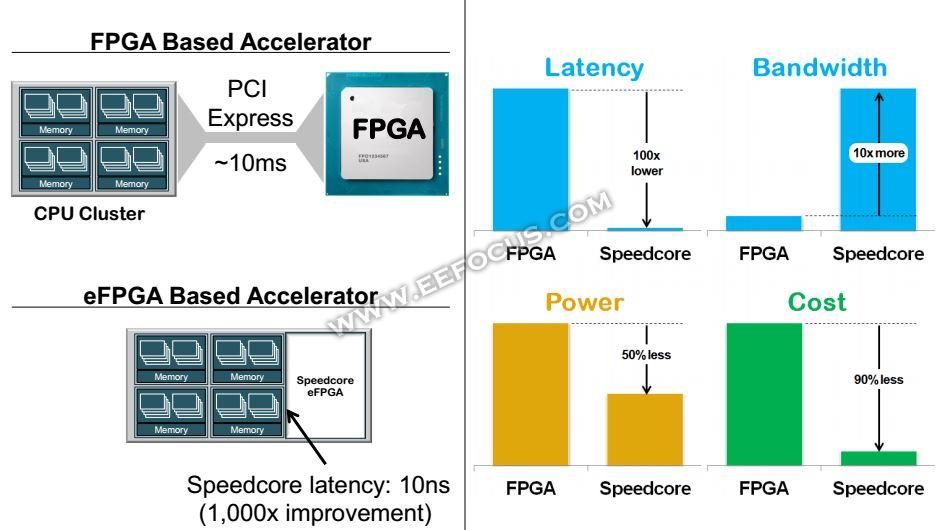

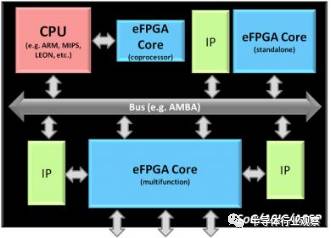

目前流行的两种集成方案分别是embedded FPGA(以下简称eFPGA集成方案)以及FPGA Chiplets(以下简称cFPGA集成方案)1.eFPGA集成方案eFPGA是嵌入到SoC中的FPGA IP核,可以是软核或者是硬核,工艺节点往往需要和SoC保持一致。

2021-08-16 09:53:47 8291

8291

什么是FPGA原型? FPGA原型设计是一种成熟的技术,用于通过将RTL移植到现场可编程门阵列(FPGA)来验证专门应用的集成电路(ASIC),专用标准产品(ASSP)和片上系统(SoC)的功能

2022-07-19 16:27:29 2400

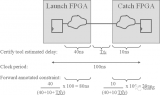

2400 在进行FPGA原型验证的过程中,当要把大型的SoC进行FPGA原型验证时,有时候会遇到一种情况,同样的接口分两组出去到不同的模块,而这两个模块规模较大,又需要分割在两片FPGA中,这时候就会像下图一样:

2023-04-25 11:15:20 2534

2534

FPGA原型在数字芯片设计中非常重要,因为相比用仿真器,或者加速器等来跑仿真,FPGA的运行速度,更接近真实芯片,可以配合软件开发者来进行底层软件的开发。这一流片前的软硬件的协同开发,是其最不可替代的地方。

2023-05-10 10:44:00 11197

11197

FPGA原型验证已是当前原型验证的主流且成熟的芯片验证方法——它通过将RTL移植到现场可编程门阵列(FPGA)来验证ASIC的功能,并在芯片的基本功能验证通过后就可以开始驱动的开发,一直到芯片

2020-08-21 05:00:12

Altera公司意欲通过更先进的制程工艺和更紧密的产业合作,正逐步强化FPGA协同处理器,大幅提升SoC FPGA的整体性能,为抢攻嵌入式系统市场版图创造更大的差异化优势。随着SoC FPGA在

2019-08-26 07:15:50

STM32学习笔记①ARM、MCU、DSP、FPGA、SoC各是什么?区别是什么?(转)ARM、MCU、DSP、FPGA、SoC的比较CMSIS标准ARM、MCU、DSP、FPGA、SoC各

2021-12-09 07:08:05

ASIC设计-FPGA原型验证

2020-03-19 16:15:49

Qt配置Altera SoC FPGA Kit 编译器: GCC(Altera SoC) /home/terasic

2018-07-03 08:41:02

FPGA器件的存储器。因此,HAPS-51系统提供了一种低成本、高性能的原型设计解决方案,能显著缩短当前极具挑战性的SoC设计的开发时间。HAPS系统是Synplicity功能强大的Confirma

2018-11-20 15:49:49

加利福尼亚州,圣何塞— 2014年9月3日– S2C公司今日宣布TAI Player Pro 5.1版本正式发布。此次最新版本将帮助用户加速FPGA原型开发、提高工程师的生产力,以及实现最高的原型

2019-07-02 06:23:44

ArduZynq 和 TE0726-03M ZynqBerry SBC 中的 Zynq Z-7010 SoC 的 FPGA 容量存在显著差异。虽然所有 Zynq-7000 SoC 都采用双核 Arm

2018-08-31 14:43:05

什么是FPGA/AD9371/AD9009/RF SOC?

2021-10-09 06:37:51

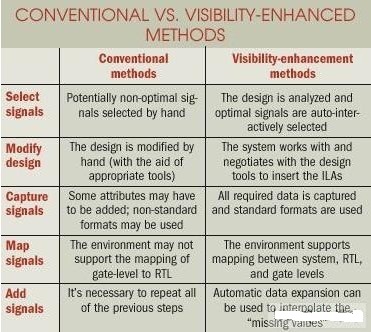

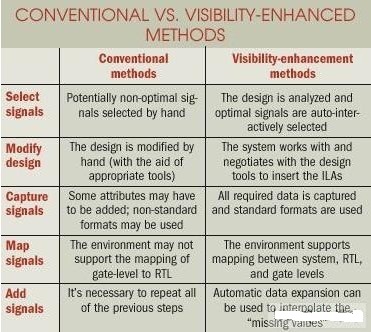

制化FPGA原型板验证效率的创新方法,自动化现有的电路仿真(in-circuit emulation)侦错功能,并提供更高的FPGA能见度。这个以FPGA为基础的SoC验证平台对工研院而言是前景看好

2011-07-24 09:47:50

SoC原型的Handel-C描述及其实现流程是怎样的?利用RC1000和SoC设计展示评估平台RC200搭建一个原型验证系统的样机?

2021-05-28 06:15:18

采用基于现场可编程门阵列(FPGA)的原型的验证团队面临的最大挑战之一在于当原型系统未能发挥期望的性能时了解原型系统的内部行为。分析和调试这些设计的一个关键因素是难以观察内部信号。 目前的顶级

2019-07-12 06:38:15

FPGA在嵌入式系统中的优势有哪些?如何通过LabVIEW FPGA加速嵌入式系统原型化?

2021-05-06 07:42:56

迫使设计团队不得不重新思考其发展策略。再加消费类物联网设备对产品上市时间的压力,很显然工程师需要适当的解 决方案来解决这些问题。让你在设计初期信心倍增基于FPGA 的原型系统是专门针对物联网设备

2018-08-07 09:41:23

用基于现场可编程门阵列(FPGA)的原型的验证团队面临的最大挑战之一在于当原型系统未能发挥期望的性能时了解原型系统的内部行为。分析和调试这些设计的一个关键因素是难以观察内部信号。 目前的顶级

2020-07-07 09:08:34

采用基于现场可编程门阵列(FPGA)的原型的验证团队面临的最大挑战之一在于当原型系统未能发挥期望的性能时了解原型系统的内部行为。分析和调试这些设计的一个关键因素是难以观察内部信号。

2019-10-14 07:07:06

为什么不能采用基于现场可编程门阵列(FPGA)的原型?验证团队面临的最大挑战之一在于当原型系统未能发挥期望的性能时了解原型系统的内部行为。分析和调试这些设计的一个关键因素是难以观察内部信号。

2019-08-13 07:45:06

扩大软件使用这一趋势对ASIC与SoC原型设计技术和总设计过程有何影响呢?

2021-04-08 06:14:35

。基于FPGA的原型验证方法凭借其速度快、易修改、真实性的特点,已经成为ASIC芯片设计中重要的验证方法。本文主要描述高频RFID芯片的FPGA原型验证平台的设计,并给出验证结果。1、RFID芯片的FPGA

2019-05-29 08:03:31

FPGA 原型设计人员艰苦努力所得的明显回报就是 ASIC* 设计可以及时而毫无问题地完成产品定案(tape-out)。不过,原型设计还有一点日益重要的优势,即 ASIC 或 SoC 中嵌入的软件在项目

2010-01-18 08:35:09 18

18 基于FPGA 的SOC 系统中的串口设计

作者:葛锐 欧钢摘要:本文在XILINX FPGA 中采用嵌入式处理器Picoblaze 进行SOC 设计,以较少的

2010-02-08 09:48:37 21

21 随着SoC设计复杂度的提高,验证已成为集成电路设计过程中的瓶颈,而FPGA技术的快速发展以及良好的可编程特性使基于FPGA的原型验证越来越多地被用于SoC系统的设计过程。本文讨论

2010-11-11 16:00:07 35

35 基于FPGA的可层叠组合式SoC原型系统设计

在复杂片上系统SoC的设计过程中,验证仿真是影响项目进度的关键因素。随着芯片生产和制造工艺的提高,SoC设计的规模、复杂

2010-01-08 11:18:42 1204

1204

《 FPGA的原型开发方法手册》(FPMM),这是一本介绍如何使用 FPGA 作为平台进行片上系统(SoC)开发的实用指南。FPMM 收录了众多公司的设计团队在设计和验证方面的宝贵经验,

2011-03-14 09:06:50 1099

1099 Synopsys和Xilinx合作出版业界首本基于FPGA的SoC设计原型方法手册。

2011-03-21 10:26:23 1139

1139 台湾工业技术研究院提出一种能够显著提升客制化FPGA原型板验证效率的创新方法,自动化现有的 电路仿真 (in-circuit emulation)侦错功能,并提供更高的FPGA能见度。这个以FPGA为基础的SoC验

2011-09-09 11:35:24 1404

1404

Altera公司(Nasdaq: ALTR)今天宣布可以提供FPGA业界的第一个虚拟目标平台,支持面向Altera最新发布的SoC FPGA器件立即开始器件专用嵌入式软件的开发。在Synopsys有限公司成熟的虚拟原型开发解

2011-10-13 09:15:28 938

938 本文是关于Altera公司SoC FPGA 的用户手册(英文版) 。文中主要介绍了什么是SoC FPGA、SoC FPGA相关知识介绍、为什么要使用SoC FPGA以及SoC FPGA都应用到哪些方面。

2012-09-05 14:03:08 153

153 新思科技公司日前宣布:该公司推出其Synopsys HAPS®-70系列基于FPGA的原型验证系统,从而扩展了其HAPS产品线以应对系统级芯片(SoC)设计的不断增加的规模及复杂度。

2012-11-27 21:51:39 1766

1766 我经常收到关于各类设备之间的差异的问题,诸如ASIC、ASSP、SoC和FPGA之间的区别问题。例如是SoC是ASIC吗?或ASIC是SoC吗?ASIC和ASSP之间的区别是什么?以及高端FPGA应该归类为SoC吗?

2014-07-17 09:42:39 44877

44877 新增的8种模块使设计者更专注于产品差异化, 并加快产品上市时间 S2C 公司,业内领先的 FPGA 快速原型验证系统供应商, 今日发布8种新的 FPGA 原型验证接口子卡和配件,其旨在加快发展片上

2017-02-08 06:50:11 1106

1106

Hitech Global是一家美国的电子产品以及方案设计公司,总部坐落在加利福尼亚州圣何塞市。Hitech Global的产品包括IP核,基于评估/原型板的Xilinx和Altera FPGA

2017-02-08 09:09:11 1002

1002

如今,设计人员使用两种相对独立的方法进行 SoC 原型验证:以事务级模型为基础的虚拟原型验证和基于 FPGA 的原型验证。 虚拟原型验证执行快速的 TLM,并可提供更高效的调试和分析方案,非常适合

2017-02-08 14:32:11 572

572 运行真正SoC固件的FPGA仿真要快得多。这就是你需要为软件开发、硬件验证、硬件/软件集成和复杂SoC的回归测试所做的。Cadence刚介绍了它们的第二代基于FPGA的Protium快速原型平台

2017-02-08 15:49:11 572

572

设计了一种基于FPGA的验证平台及有效的SoC验证方法,介绍了此FPGA验证软硬件平台及软硬件协同验证架构,讨论和分析了利用FPGA软硬件协同系统验证SoC系统的过程和方法。利用此软硬件协同验证

2017-11-17 03:06:01 21449

21449

门阵列(FPGA)做为安谋国际核心测试芯片,进而建构SoC原型制作平台。 验证SoC设计 FPGA原型最稳当 FPGA原型制作是在FPGA上实作SoC或特定应用集成电路(ASIC)设计的方法,并进行硬件验证和早期软件开发。

2018-05-11 09:07:00 3069

3069

Fujisoft公司在Altera SoC合作伙伴研讨会上演讲的主题:Fujisoft Android SoC FPGA解决方案

2018-06-26 11:57:00 3370

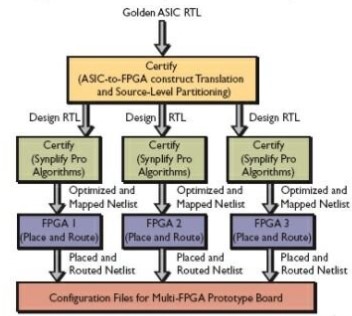

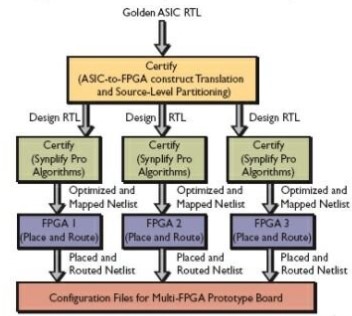

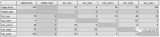

3370 近年来,ASIC设计规模的增大带来了前所未有的芯片原型验证问题,单颗大容量的FPGA通常已不足以容下千万门级、甚至上亿门级的逻辑设计。现今,将整个验证设计分割到多个采用最新工艺大容量FPGA中,FPGA通过高速总线互联,成为大规模ASIC或SOC原型验证的极佳选择。

2018-07-02 08:20:00 2166

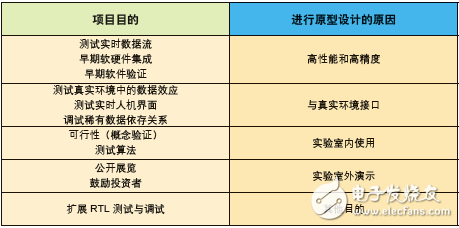

2166 原型设计不是一个按几个按钮就能完成的过程,在它不同的阶段需要仔细的关注和思考。除说明这个过程需要完成的工作和涉及到的专业知识外,我们还应解释在 SoC 项目中该进行(或者不该进行)原型设计的原因。

2018-07-09 15:11:00 2560

2560 FPGA 原型设计人员艰苦努力所得的明显回报就是 ASIC 设计可以及时而毫无问题地完成产品定案(tape-out)。

2018-07-19 11:33:00 2818

2818 在不太遥远的过去,对ASIC设计团队而言,在这类情况下主要的解决方案就是在内部建立他们自己的定制多个FPGA的原型开发板。然而,今天,使用现成的多个FPGA原型开发板——例如,由Synplicity

2019-05-16 08:07:00 3784

3784

采用基于现场可编程门阵列(FPGA)的原型的验证团队面临的最大挑战之一在于当原型系统未能发挥期望的性能时了解原型系统的内部行为。分析和调试这些设计的一个关键因素是难以观察内部信号。

2019-01-08 08:16:00 2517

2517

虽然系统级芯片( SoC )的架构师们已了解嵌入式FPGA( eFPGA )内核能如何为他们的ASIC/ SoC 设计增加价值,甚至是在规划出一个具体应用之前就了解,但可能还不清楚如何开始进行一次

2018-09-20 09:51:00 4717

4717 美高森美公司(Microsemi),宣布提供SmartFusion 2入门者工具套件,为设计人员提供用于其SmartFusion2系统级芯片(SoC)现场可编程门阵列(FPGA)的基础原型构建平台。

2018-09-25 16:34:00 2284

2284 很低,这也是为何独孤的PowerPC和FPGA要结合ARM 弄SoC的原因之一。可以不夸张地说,FPGA SoC是对ARM架构的MPU一场赤裸裸的打劫! eFPGA即嵌入式FPGA(embedded

2019-01-17 17:18:08 7100

7100

小梅哥最新款FPGA_SOC

2019-05-28 06:09:34 4929

4929 小梅哥最新款FPGA_SOC

2019-09-02 06:02:00 2976

2976

小梅哥最新款FPGA_SOC

2019-08-30 06:10:00 4418

4418

小梅哥最新款FPGA_SOC

2019-08-30 06:08:00 2617

2617

随着新型SoC(片上系统)设计的成本和复杂性的不断提高,现场可编程门阵列(FPGA)原型技术正日益成为SoC新项目的重要组成部分,甚至是至关重要的组成部分。通过提供一种更快到达硬件的方法,FPGA

2019-06-25 08:00:00 2

2 如果说eFPGA是往SoC里面加入FPGA的话,那么FPGA SoC的概念就是在FPGA里面加上了处理器。FPGA经过这么多年的发展,已经不只是验证设计的平台,而变成了一种独立的设计实现方式。FPGA可快速重配置的特点使它在许多对灵活性有要求的平台如鱼得水。

2019-09-04 16:12:32 4805

4805

FACE-VUP:大规模FPGA原型验证平台 FACE-VUP大规模FPGA原型验证平台是FACE系列的最新产品。FACE-VUP同时搭载16nm工艺的Virtex UltraScale+系列主器件

2020-05-19 10:50:05 3371

3371 Virtex UltraScale+ VU19P是赛灵思密度最高的FPGA,是ASIC和SOC原型验证的最佳选择。

2020-10-22 14:23:13 2078

2078 作为还包括形式验证、仿真和仿真的 Cadence 验证套件的一部分,基于 FPGA 的原型设计刚刚通过自动化进行了重新发明,并可供更广泛的物联网设计开发人员使用。

2022-06-09 16:39:01 2366

2366

在现代SoC芯片验证过程中,不可避免的都会使用FPGA原型验证,或许原型验证一词对你而言非常新鲜,但是FPGA上板验证应该是非常熟悉的场景了。

2023-03-28 09:33:16 2001

2001 我们当然希望在项目中尽快准备好基于FPGA原型验证的代码,以便最大限度地为软件团队和RTL验证人员带来更客观的收益。

2023-03-28 14:11:15 1690

1690 开始SoC FPGA的学习路程还是蛮难的,不仅要熟悉整个的设计流程,而且还要掌握FPGA以及软件方面的知识,尤其大概看了一下后面的整体设计部分,操作起来还是较为繁琐的,以至于让人晕头转向。尽管如此

2023-03-30 10:13:35 12444

12444 FPGA原型验证在数字SoC系统项目当中已经非常普遍且非常重要,但对于一个SoC的项目而言,选择合适的FPGA原型验证系统显的格外重要

2023-04-03 09:46:45 2074

2074 FPGA原型平台的性能估计与应用过程的资源利用率以及FPGA性能参数密切相关,甚至FPGA的制程也是一个因素。

2023-04-04 09:49:04 3145

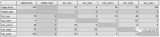

3145 当SoC系统的规模很大的时候,单片FPGA验证平台已经无法容纳这么多容量,我们将采取将SoC设计划分为多个FPGA的映射。

2023-04-06 11:20:48 1400

1400 如果SoC设计规模小,在单个FPGA内可以容纳,那么只要系统中的FPGA具有所SoC所设计需要时钟的数量

2023-04-07 09:42:57 1705

1705 FPGA原型设计是一种成熟的技术,用于通过将RTL移植到现场可编程门阵列(FPGA)来验证专门应用的集成电路(ASIC),专用标准产品(ASSP)和片上系统(SoC)的功能和性能。

2023-04-10 09:23:29 2664

2664 FPGA原型验证平台系统灵活性主要体现在其外部连接表现形式,由单片FPGA平台或者2片的FPGA,抑或是4片的FPGA组成一个子系统。

2023-04-11 09:50:03 1543

1543 FPGA原型验证平台系统灵活性主要体现在其外部连接表现形式,由单片FPGA平台或者2片的FPGA,抑或是4片的FPGA组成一个子系统。

2023-04-11 09:50:37 936

936 FPGA原型验证系统要尽可能多的复用SoC相关的模块,这样才是复刻SoC原型的意义所在。

2023-04-19 09:08:15 1953

1953 尽管对于工程师而言目标始终是以原始形式对SoC源RTL进行原型化,但在原型化工作的早期,SoC设计必须进行必要的修改,以适应FPGA原型系统。

2023-04-26 09:48:13 1689

1689 对SoC芯片要进行FPGA原型验证,假如设计较大,要将SoC中不同功能模块或者逻辑模块分别分配到特定的FPGA,那么对SoC的分割策略尤为重要

2023-04-27 15:17:06 1699

1699

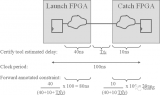

在进行FPGA原型验证的过程中,当要把大型的SoC进行FPGA原型验证时,有时候会遇到一种情况,同样的接口分两组出去到不同的模块,而这两个模块规模较大,又需要分割在两片FPGA中,这时候就会像下图一样。

2023-05-04 16:21:34 1331

1331

多片FPGA原型验证系统的拓扑连接方式各不相同,理想的多片FPGA原型验证系统应该可以灵活配置,可以使用其相应的EDA工具

2023-05-08 11:51:40 891

891

当SoC的规模在一片FPGA中装不下的时候,我们通常选择多片FPGA原型验证的平台来承载整个SoC系统。

2023-05-10 10:15:16 689

689 SoC的顶层的约束适用于FPGA到其各自时钟域中的各个Flip_Flop,如果定义了跨时钟域,也适用于FPGA之间。当我们可以确保每个FPGA边界都有一个IOFF,它与SoC中相应的元素对齐时,这一点对于性能而言非常重要。

2023-05-13 09:38:09 2408

2408

当SoC的规模在一片FPGA中装不下的时候,我们通常选择多片FPGA原型验证的平台来承载整个SoC系统。

2023-05-23 15:31:10 1015

1015 如果SoC设计规模小,在单个FPGA内可以容纳,那么只要系统中的FPGA具有所SoC所设计需要时钟的数量

2023-05-23 15:46:24 1420

1420

FPGA原型验证系统要尽可能多的复用SoC相关的模块,这样才是复刻SoC原型的意义所在。

2023-05-23 16:50:34 1109

1109

多片FPGA的原型验证系统的性能和容量通常受到FPGA间连接的限制。FPGA中有大量的资源,但IO引脚的数量受封装技术的限制,通常只有1000个左右的用户IO引脚。

2023-05-23 17:12:35 2189

2189

我们当然希望在项目中尽快准备好基于FPGA原型验证的代码,以便最大限度地为软件团队和RTL验证人员带来更客观的收益。

2023-05-30 11:10:27 1358

1358

在现代SoC芯片验证过程中,不可避免的都会使用FPGA原型验证,或许原型验证一词对你而言非常新鲜,但是FPGA上板验证应该是非常熟悉的场景了。

2023-05-30 15:04:06 2103

2103

)要求一个基于多个FPGA的原型开发板。 在不太遥远的过去,对ASIC设计团队而言,在这类情况下主要的解决方案就是在内部建立他们自己的定制多个FPGA的原型开发板。然而,今天,使用现成的多个FPGA原型开发板——例如,由Synplicity公司的原型开发伙伴生产的开发板——与合适

2023-06-04 16:50:01 2194

2194 综合工具的任务是将SoC设计映射到可用的FPGA资源中。自动化程度越高,构建基于FPGA的原型的过程就越容易、越快。

2023-06-13 09:27:06 879

879

当SoC系统的规模很大的时候,单片FPGA验证平台已经无法容纳这么多容量,我们将采取将SoC设计划分为多个FPGA的映射。

2023-06-19 15:42:08 1081

1081 LiteX 框架为创建 FPGA 内核/SoC、探索各种数字设计架构和创建完整的基于 FPGA 的系统提供了方便高效的基础架构。

2023-06-28 09:08:05 1323

1323

MCU 对应用主导地位的挑战已经开始。具有片上固定功能处理子系统的现场可编程逻辑器件 (FPGA),也就是片上系统 (SoC) FPGA,最近已成为高端处理应用的潜在竞争者。这就提出了一个问题:随着

2023-08-26 10:45:02 3717

3717

所有形式的原型都为验证硬件设计和验证软件提供了强大的方法,模型或多或少地模仿了目标环境。基于FPGA的原型设计在项目的关键后期阶段尤其有益。用户有几个原型设计选项根据他们的主要需求,可以选择各种基于软件和硬件的技术来原型他们的设计。

2023-10-11 12:39:41 1808

1808

FPGA原型设计是一种成熟的技术,用于通过将RTL移植到现场可编程门阵列(FPGA)来验证专门应用的集成电路(ASIC),专用标准产品(ASSP)和片上系统(SoC)的功能和性能。

2024-01-12 16:13:01 2194

2194 proFPGA是mentor的FPGA原型验证平台,当然mentor被西门子收购之后,现在叫西门子EDA。

2024-01-22 09:21:01 3230

3230

FPGA芯片和SoC芯片在多个方面存在显著的区别。

2024-03-14 17:28:11 5060

5060 FPGA原型验证流程是确保FPGA(现场可编程门阵列)设计正确性和功能性的关键步骤。它涵盖了从设计实现到功能验证的整个过程,是FPGA开发流程中不可或缺的一环。

2024-03-15 15:05:33 3058

3058 子,工程师可以从 proFPGA Uno 系统开始进行 IP 或子片上系统 (SoC) 的开发,然后将其重复用于完整的 SoC 和专用集成电路 (ASIC)原型设计。这只需要将 Uno 中的相同

2025-06-30 13:53:59 1694

1694

电子发烧友App

电子发烧友App

评论