对SoC芯片要进行FPGA原型验证,假如设计较大,要将SoC中不同功能模块或者逻辑模块分别分配到特定的FPGA,那么对SoC的分割策略尤为重要。这一点和大规模的多片FPGA设计有所不同,在设计一个大规模的FPGA产品之前,你可能在一开始就会考虑到如何将不同的功能模块以及连接方式分别合理的放到不同的FPGA中,各个FPGA之间的连接在设计之初就有考虑。

但是,对于大规模SoC设计要分割到多片的FPGA中,对于出database的逻辑原型工程师而言,显得有点“措手不及”,因为整体的RTL架构代码并未考虑在多片FPGA上的实现架构,前端SoC架构以及前端的RTL设计工程师更多考虑的是SoC的实现流程。所以,这一点给原型验证工程师带来挑战,但是我们可以顺着以下思路运用相关软件进行手动分割。

分配高度连接的模块

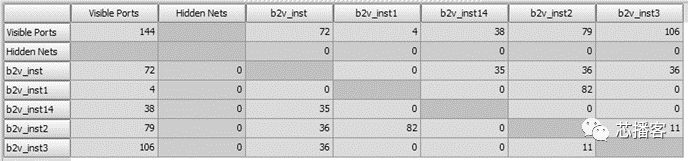

我们期望分割工具可以显示模块级互连信息,比如我们在工具中可以选择设计的层次结构的模块列表(层次结构之所以非常重要,就是因为在SoC的设计过程中,本身就会遵循以功能为大方向去写RTL级别的代码,然后“高内聚,低耦”的思路划分模块与层次关系的),然后列表会展示相应的模块与模块之间的连接关系。例如以下工具展示的模块之间的互连:

这里,我们可以立即看到块b2v_inst1和b2v_inst2共享82个相互连接,但b2v_ints3与块的顶级IO的连接最多(106)。当用大量相互连接的信号划分多个块时,重要的任务是确保这些块放置在同一FPGA中。如果高度连接的块被放置在不同的FPGA中,那么我们将需要大量的FPGAIO引脚来重新连接它们。

例如,当使用64位和更大的总线时,分配到不同FPGA中的两个块很可能需要数百个额外的FPGA IO。因此,在上面的示例中,我们可能会尝试先将b2v_inst3分配到一个FPGA中,而b2v_inst1和b2v_ins2可以一起分配到不同的FPGA中,因为它们是相互连接的,但与b2v_ins3几乎没有连接。

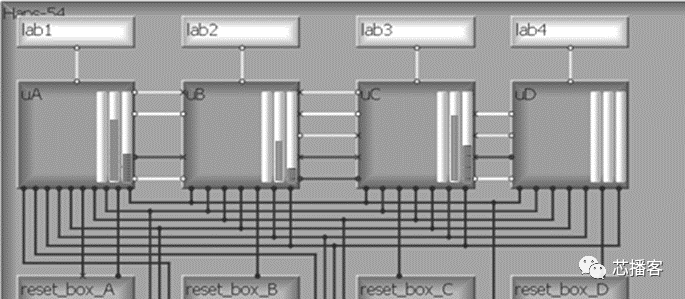

其次,我们期望工具能够展示大致的FPGA分区信息,当我们手动选择相关模块到各FPGA块的时候,分割软件可以及时的反馈相关分区FPGA的资源使用情况,以便我们做出最优的手动分割选择。

如果不可能将高度互连的块放在一起,因为它们溢出了一个FPGA的资源,那么我们将需要降低层次结构级别,并在下一级查找连接较少的块,并提取要分配到不同FPGA中的块。通过这种方式,我们仍然可以增加所需的FPGA的IO的数量,但比将更高级别的块分配到其他地方的情况要少。

如果在此较低级别上没有这样的分区,则我们可能会走得更低,但在越来越细的逻辑粒度上指定分区会使分区更可能受到设计迭代的影响,因为这些更细的粒度被不同地优化或重命名。如果我们发现自己必须深入层次结构以找到解决方案,那么最好返回并使用不同的粗略分区在顶层重新启动。

分配各种设计功能模块

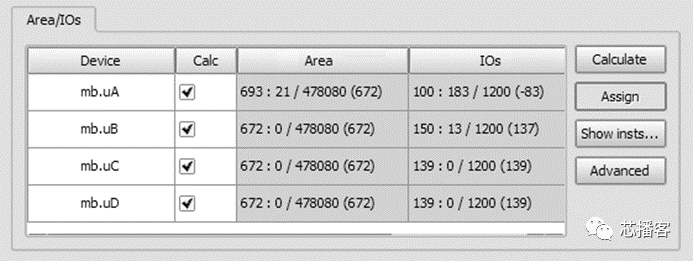

使用我们对每个块的面积的估计,我们可以将剩余的设计块分配给FPGA资源,从最大的块开始。我们从较大的块开始,因为这自然会将较小的块留给稍后的分区过程。然后,随着FPGA资源可能变得过满(请记住,50%到70%的利用率是一个很好的目标),我们可以更自由地放置粒度更细、输入和输出数量更少的较小块。

当我们进行分区时,我们希望平衡FPGA的资源使用,同时将利用率保持在可容忍的范围内,即低于70%的建议值。这将有助于避免长时间的运行时间,并使其更容易达到所需的时间。

选择了分区的候选块后,我们可能会进行尝试分配,直到找到最佳解决方案,然而,在具有许多FPGA的原型中,这是低效的。我们已经看到,对我们的任务决定进行即时反馈是多么有用。事实上,在分配任务之前获得反馈更为有用。这使我们能够提前了解如果将选定块放置在这样或那样的FPGA中,对IO和资源的影响。这种预警称为影响分析。

这里我们可以看到,我们选择的块具有672个逻辑元素的区域,从先前的资源估计中提取。如果我们选择将块分配给mb.uB,我们将使FPGA的面积增加672个逻辑元件(总共478080个),并将IO计数增加137个,使其总数达到150个。

我们还可以看到,如果我们将块分配给mb.uA,那么面积仍将增加相同的数量,但IO需求将减少83个引脚,这可能是因为我们的块连接到已经分配给mb.uA的一些逻辑。我们可以根据此快速分析选择mb.uA然后单击分配。与所有由交互式用户界面驱动的工具一样,一旦我们熟悉该方法,就可以使用脚本和命令行。

在放置了主要的分层块之后,我们可以使用相同的方法用较小的块来填补空白。对于较小的块,顺序并不那么重要,我们可以通过连接和资源使用等信息来指导。一些工具还提供屏幕上的指导,如基于所需连接的各种权重的“老鼠窝”线,这些线似乎将所选块拉向最佳FPGA选择。

在手动完成关键任务后,一些团队将在这个阶段改用自动分区。如果这可以在与手动分区器相同的环境中运行,则效率更高。我们只是到达了一个让我们感到满意的地步,我们已经控制了我们的关键任务,并按下按钮完成剩下的任务。

审核编辑:刘清

-

FPGA

+关注

关注

1655文章

22282浏览量

630071 -

SoC芯片

+关注

关注

2文章

662浏览量

36807 -

RTL

+关注

关注

1文章

393浏览量

62379

原文标题:对SoC进行手动FPGA分区

文章出处:【微信号:于博士Jacky,微信公众号:于博士Jacky】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

SoC FPGA有哪些作用?

基于FPGA的SOC系统中的串口设计

Altera公司SoC FPGA 简介

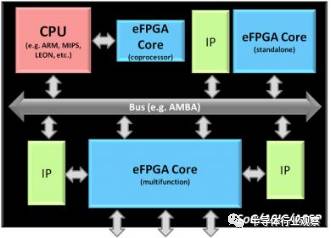

SoC设计中嵌入FPGA(eFPGA)内核实用评估方法

新硬盘进行重新分区的简单技巧

什么是SoC、SOPC、SoC FPGA?用在什么场景?

基于FPGA的SoC创建方案

如何对SoC进行手动FPGA分区

如何对SoC进行手动FPGA分区

评论