Silicon Labs(亦称“芯科科技”)近日推出“Clock Talk”时钟线上系列研讨会的第二场随选即播中文演讲主题“为56G/112GSerDes选择XO/VCXO时钟参考时的设计考量”,提供了中文及英文演说版本供用户选择。 为56G/112G SerDes选择XO/VCXO时钟参考时的设计考量

电信、无线基础设施、光学模块、广播视频、医学成像和其他工业市场的下一代参考时钟要求大量采用FPGA、ASIC和SoC,它们使用56G 或112G SerDes 来支持更高的数据速率和带宽功能。SerDes 带宽增加和相关参考时钟的RMS 相位抖动要求之间存在直接的相关性。

随着SerDes 速度的增加,参考时钟所需的 RMS 相位抖动性能随之减少。在本次网络研讨会上,我们概述最新一代FPGA、光学DSP、相干DSP 和网络处理器的参考时钟要求,并重点介绍Si54x Ultra Series XO 和 VCXO 产品家族的关键功能,这些功能可确保参考时钟RMS 相位抖动性能保持在最大限度内;从而为系统设计者在其系统抖动预算中增加了更多馀欲。

责任编辑:lq

-

FPGA

+关注

关注

1664文章

22503浏览量

639274 -

时钟

+关注

关注

11文章

1999浏览量

135236 -

网络处理器

+关注

关注

1文章

52浏览量

14502

原文标题:Clock Talk中文随选即播新单元上线-选择XO/VCXO时钟参考的设计考量

文章出处:【微信号:SiliconLabs,微信公众号:Silicon Labs】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

RL78/G1G微控制器:特性、规格与应用考量

RL78/G11微控制器:特性、电气规格与应用考量

TE Connectivity推出全新56G MezzaWave连接器

深入解析RL78/G1G单片机:特性、规格与应用考量

全球首款4×112G 算力中心模拟CDR电芯片由上海米硅突破!

基于TE Connectivity QSFP-DD 112G连接器数据手册的技术解析

TE Connectivity QSFP 112G SMT连接器与屏蔽罩技术解析

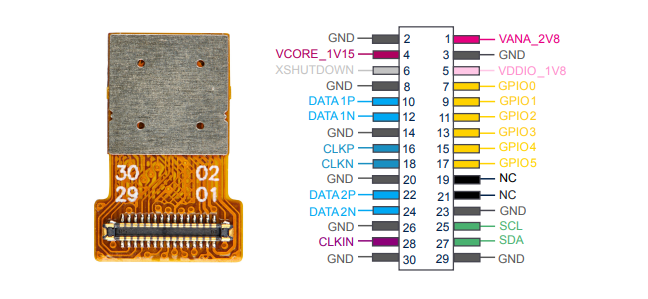

STMicroelectronics CAM-56G3相机模块技术解析与应用指南

WLAN/WiMAX 时钟选型:TCXO/VCXO/OCXO 如何影响 EVM/CFO(含两张对比图)

Electronica现场演示 | 严苛环境下的56G互连

贸泽即日起开售适用于数据中心和网络应用的 全新TE Connectivity QSFP 112G SMT连接器

差分输出VCXO:低抖动时钟源助力光通信系统精密同步

为56G/112G SerDes选择XO/VCXO时钟参考时的设计考量

为56G/112G SerDes选择XO/VCXO时钟参考时的设计考量

评论