借助于DDR3实现大型矩阵90°的转置

- FPGA(591969)

- DDR3(41693)

- RAM(113632)

相关推荐

华邦将持续扩产 DDR3 SDRAM

和 x16 配置中均可提供高达 2133Mbps 的数据传输速率,并可与1.5V DDR3实现100%兼容。目前,华邦的 DRAM 产品布局包括1Gb-4Gb DDR3、128Mb-2Gb DDR

2022-04-20 16:04:03 2554

2554

2554

2554

6657的DDR3初始化不成功

最近我在调试自制6657板子的DDR3初始化,发现一个很奇怪的现象,百思不得其解,我分别用GEL和KEYSTONE DDR3 INIT 在6657EVM开发板上做DDR3初始化,是没有问题的,我用

2019-01-08 10:19:00

665x的DDR3配置

的命令重排和调度使得数据在最大吞吐量时也能有效的传输。通过打开和关闭DDR3 SDRAM的行来实现最大效率的使用数据,地址和命令总线。命令的重排顺序在命令FIFO中。DDR3内存控制器检查在命令FIFO中

2018-01-18 22:04:33

6678中的EDMA3操作 (DDR3 DSP EDMA)

请教各位大虾:

怎样实现6678和DDR3间的EDMA操作,哪位高手有相关的代码可以共享哈

还有就是当从DDR3中将数据一维搬至DSP中,处理完后再将DSP中的数据二维放至DDR3中时需要配置哪些寄存器,具体怎样配置 谢谢!!~

2018-06-21 16:49:06

DDR3 SDRAM的简单代码如何编写

嗨,我是FPGA领域的新手。现在我正在使用Genesys2。我必须控制DDR3内存。我在Digilent网站上找到了一些使用micrlaze处理器的DDR3示例。但是,在我的情况下,我不必

2019-05-05 15:29:38

DDR3 ZQ校准简单介绍

为了实现更强大的系统操作,DDR3 SDRAM驱动器设计通过降低电容得到了增强,动态片上端接(ODT)和新的校准方案。电容减少来自于使用新的合并驱动器。使用新驱动程序,组成输出驱动程序的电路共享用于ODT。DDR2上使用单独的结构作为输出驱动器和终端阻抗。

2019-05-23 08:20:56

DDR3 的驱动问题

在调试335x的DDR3时,用的是CCS,非操作系统调试。

按TI给的AM335x——StarterKit.gel,这个文件导入到CCS,debug的时候,DDR3可以驱动,读写正常。按

2018-06-21 10:59:20

DDR3仿真,读数据时候,只有readdatavalid信号,没有readdata,请教大神

最近在做DDR3的仿真测试,写一个自定义的总线转换成avalon总线,和DDR3的控制器(EMIF)互联,传输数据,但是出现了有readdatavalid信号,而readdata一直是不定态的状况

2016-05-25 20:20:21

DDR3内存的PCB仿真与设计

1概述 当今计算机系统DDR3存储器技术已得到广泛应用,数据传输率一再被提升,现已高达1866Mbps.在这种高速总线条件下,要保证数据传输质量的可靠性和满足并行总线的时序要求,对设计实现提出

2014-12-15 14:17:46

DDR3内存详解

转载DDR3内存详解,存储器结构+时序+初始化过程2017-06-17 16:10:33a_chinese_man阅读数 23423更多分类专栏:硬件开发基础转自:首先,我们先了解一下内存的大体结构工作流程,这样会比较容量理解这些参数在其...

2021-07-27 07:10:34

DDR3基本知识

DDR3(double-data-rate three synchronous dynamic random accessmemory)是应用在计算机及电子产品领域的一种高带宽并行数据总线。DDR3 在 DDR2

2019-05-22 08:36:26

DDR3基础详解 精选资料推荐

DDR3基础详解最近在IMX6平台下做DDR3的测试接口开发,以前在学习嵌入式时,用的是官方源码,没有做过多的研究。此时需要仔细研究DDR3的引脚与时序,此篇是我在学习DDR3做的归纳与总结,其中有

2021-07-28 09:02:52

DDR3的CS信号接地问题

CPU的DDR3总线只连了一片DDR3,也没有复用总线将DDR3的CS直接拉到地的话,DDR3初始化不成功所以说DDR3的CS信号是通过沿采样的吗,电平采样不行?无法理解啊还是有其他方面原因

2016-11-25 09:41:36

DDR3设计与调试小结

本帖最后由 一只耳朵怪 于 2018-6-21 15:24 编辑

各位好!关于DDR3,之前有小结过如果进行DDR3的SW leveling和进行EMIF4寄存器的配置。但是调试时,如果进行DDR3的问题定位,现小结一下,附上相关文档。如有相关问题,可在楼下跟帖讨论。谢谢!

2018-06-21 04:01:01

ddr3模拟警告消息

你好,ISE版本为13.3,modelsim版本为10.1c 64bit.MIG工具为ddr3生成mcb。modelsim的transcript窗口中的消息如下

2019-07-08 08:44:42

矩阵转置中的问题

先生/女士 我已经编写了用于矩阵转置的vhdl代码但是我得到结果的问题意味着当我插入输入,时钟的值时,它没有显示任何东西。为什么它发生我无法理解...这里我我附上我的代码结果......matrix.docx 11 KB

2020-03-11 09:33:36

AM335x的DDR3设计和7寸屏设计

BeagleBone的参考设计中,DDR3设计是DDR3 Device without VTT Termination。而其他的AM335X的参考设计都是有VTT Termination

2018-06-21 03:05:42

Altera DDR3读取数据异常

因为工作的需要,最近做了下DDR3 IP核的读写仿真,仿真过程中DDR写数据正常,但在对DDR读取数据时出现以下的情况:1.MEM_DQ、MEM_DQS、MEM_DQSN始终为高阻态

2019-12-26 23:11:56

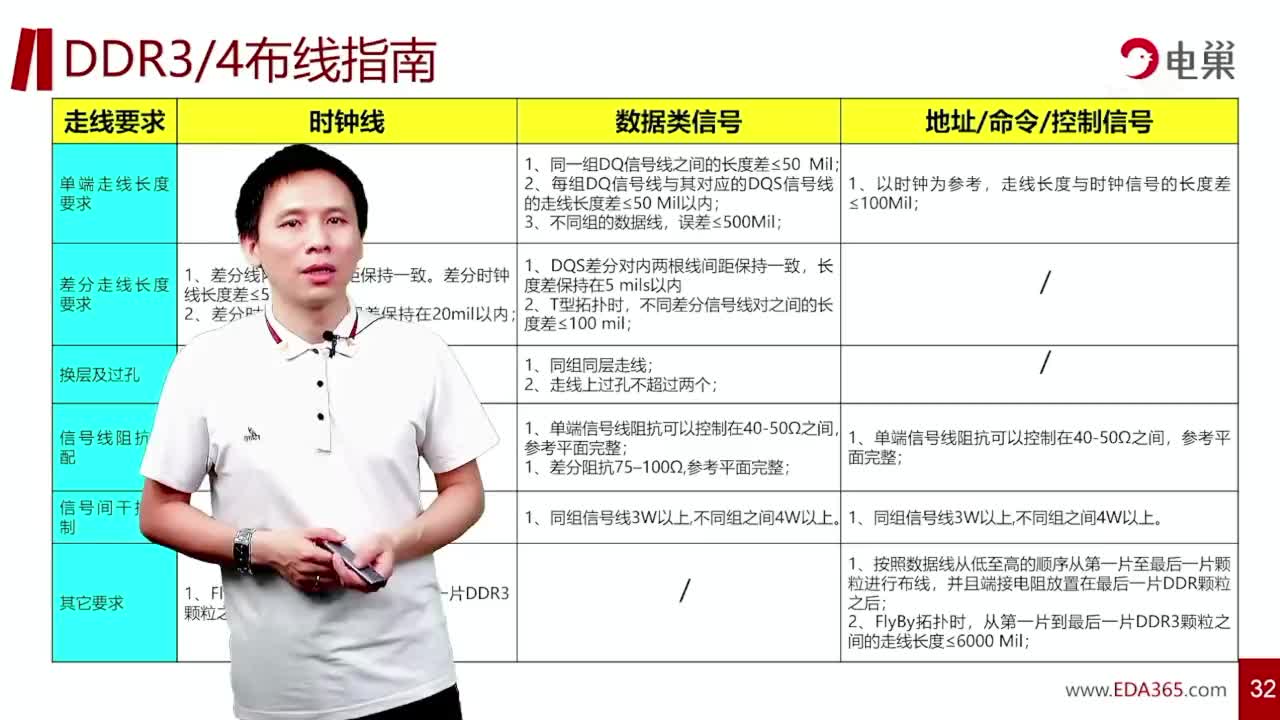

Cadence 6层板DDR3 PCB layout设计视频下载链接:

://pan.baidu.com/s/1s402 密码: 9362 播放密碼:QQ521122524以上为其中一节课程完整版视频内容:4顆DDR3拓撲講解4顆DDR3布局方法DDR3電氣規則設置等长设置DDR3信號分組等長原理DDR3等長設置DDR3电源处理DDR3布線繞線`

2014-12-17 21:16:37

Cadence 平板电脑6层板DDR3 PCB layout设计视频教程

视频内容:4顆DDR3拓撲講解4顆DDR3布局方法DDR3電氣規則設置等长设置DDR3信號分組等長原理DDR3等長設置DDR3电源处理DDR3布線繞線

2015-07-30 21:34:09

FPGA和DDR3 SDRAM DIMM条的接口设计实现

DDR3 SDRAM内存的总线速率达到600 Mbps to 1.6 Gbps (300 to 800 MHz),1.5V的低功耗工作电压,采用90nm制程达到2Gbits的高密度。这个架构毫无疑问

2019-04-22 07:00:08

Gowin DDR3参考设计

本次发布 Gowin DDR3参考设计。Gowin DDR3 参考设计可在高云官网下载,参考设计可用于仿真,实例化加插用户设计后的总综合,总布局布线。

2022-10-08 08:00:34

Xilinx DDR3 资料

Achieving High Performance DDR3 Data Rates in Virtex-7 and Kintex-7 FPGAs。Xilinx官方DDR3资料。

2016-05-27 16:39:58

cyclone V控制DDR3的读写,quartusII配置DDR3 ip核后,如何调用实现DDR3的读写呢,谢谢

DDR3的IP核配置完毕后,产生了好多文件,请问如何调用这些文件实现DDR3的读写呢?看了一些文章,说是要等到local_init_done为高电平后,才能进行读写操作。请问DDR3的控制命令如

2016-01-14 18:15:19

vc707 ddr3接口在某些情况下读取数据与写入数据不匹配

他vc707上运行我们的测试SW,那将是很棒的。这肯定有助于追查问题。该应用程序扩展了hello world示例,缓冲区放置在DDR3中。 heloworld.c和lscript.ld是附加的。提前致谢lscript.ld 5 KBhelloworld.c 3 KB

2019-09-09 10:20:26

【创龙TMS320C6748开发板试用】事件触发EDMA传输,实现矩阵转置

StringSrc变量和StringDst变量放在DDR2中固定位置。1)在cmd中给变量安排地址2)给变量赋初值以及分配地址空间3、为了实现矩阵的转置,用AB类传输,关键在与对PaRam参数的设置,其他的按键触发

2015-10-16 09:45:34

【小知识分享】SDR/DDR1/DDR2/DDR3的接口区别

DDR3的频率就是外频的8倍 133=1066DDR2和DDR3的区别内存相对于DDR2内存,其实只是规格上的提高,并没有真正的全面换代的新架构。DDR3接触针脚数目同。DDR2皆为240pin。但是

2014-12-30 14:35:58

与Kintex 7的DDR3内存接口

1.5V。所以我必须使用bank 15而不是bank 14来实现DDR3内存接口。这意味着现在我要使用12,13和12号银行。 15用于DDR3内存接口。可以使用这3个银行进行DDR3内存接口吗?使用不相邻的银行是一个问题吗?请帮帮我。问候,Iroshana。

2020-04-17 07:54:29

主要讲解矩阵运算中的放缩,乘法和转置

第22章 DSP矩阵运算-放缩,乘法和转置矩阵本期教程主要讲解矩阵运算中的放缩,乘法和转置。目录第22章 DSP矩阵运算-放缩,乘法和转置矩阵22.1 初学者重要提示22.2 DSP基础运算指令

2021-08-11 08:41:19

从DDR3升级到DDR4,到底升级了哪些变化,ICMAX告诉你

,也无法安装DDR3的内存。ICMAX DDR型号总的来说,DDR4和DDR3相比,在各个方面都有着明显的提升,出色的功耗和更加强劲稳定的性能给多任务处理和运行大型游戏提供了坚实的硬件基础,在PC领域大多

2019-07-25 14:08:13

你知道DDR2和DDR3的区别吗?

并不会注意一些数字上的差异,如DDR3和DDr2,或许大多数人都会追求时髦选择DDR3,但是你真的了解DDR2与DDR3的区别吗?作为消费者,其实我们可主宰自己的命运,用知识的武器捍卫自己的选择。下面

2011-12-13 11:29:47

关于c6657 DDR3的问题

自己画的6657的板,发现DDR3初始化有问题,初始化参数是按照芯片手册来设置的,写数据进去会出错。初步怀疑是DDR3布线问题,请问TI的大神们,6657对DDR3的布线有什么具体的要求吗?或者是

2018-06-21 05:42:03

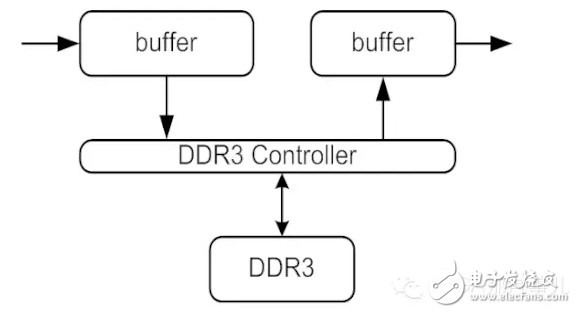

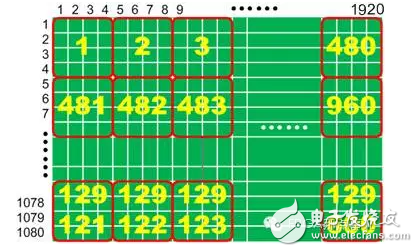

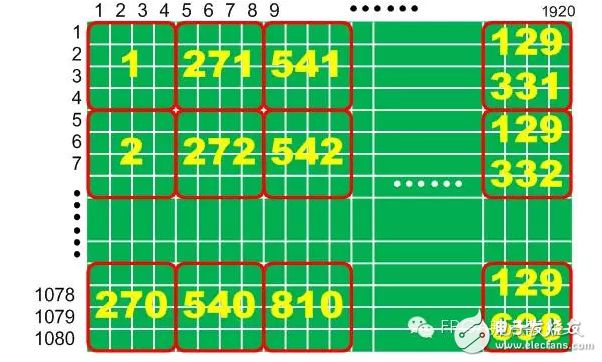

基于DDR3存储器的数据处理应用

了设计的一大挑战。FPGA可通过在单个FPGA中实现多个视频处理器来提供强大的处理能力。那么现在的挑战就变成了要使数据尽快且高效地从FPGA进出。DDR3存储器系统在大多数情况下可以为这些基于FPGA的系统

2019-05-27 05:00:02

基于FPGA的DDR3 SDRAM控制器的设计与优化

进行了DDR3 SDRAM控制器的编写,分析并提出了提高带宽利用率的方法。最终将其进行类FIFO接口的封装,屏蔽掉了DDR3 IP核复杂的用户接口,为DDR3数据流缓存的实现提供便利。系统测试表明,该

2018-08-02 09:34:58

基于FPGA的DDR3六通道读写防冲突设计

作者:张凤麒,张延彬,王忠勇;2018年电子技术应用第7期摘要: 为了解决期货行情数据加速处理中多个通道同时访问DDR3时出现的数据读写冲突问题,实现了一种基于FPGA的DDR3六通道读写防冲突

2018-08-02 09:32:45

基于FPGA的DDR3多端口读写存储管理的设计与实现

作者:吴连慧,周建江,夏伟杰摘要:为了解决视频图形显示系统中多个端口访问DDR3的数据存储冲突,设计并实现了基于FPGA的DDR3存储管理系统。DDR3存储器控制模块使用MIG生成DDR3控制器

2018-08-02 11:23:24

基于FPGA的DDR3用户接口设计

Xilinx Virtex-6系列FPGA中使用MIG3.7 IP核实现高速率DDR3芯片控制的设计思想和设计方案。针对高速实时数字信号处理中大容量采样数据通过DDR3存储和读取的应用背景,设计和实现了

2018-08-30 09:59:01

大量收购现代DDR3

大量收购现代DDR3长期回收现代ddr3,高价收购现代DDR3.大量求购现代DDR3.深圳帝欧专业电子回收,帝欧赵生***QQ1816233102/879821252邮箱dealic@163.com

2021-10-13 19:12:25

大量收购现代DDR3 长期回收现代ddr3

大量收购现代DDR3长期回收现代ddr3,高价收购现代DDR3.大量求购现代DDR3.深圳帝欧专业电子回收,帝欧赵生***QQ1816233102/879821252邮箱dealic@163.com

2021-10-13 19:18:05

如何提高DDR3的效率

现在因为项目需要,要用DDR3来实现一个4入4出的vedio frame buffer。因为片子使用的是lattice的,参考设计什么的非常少。需要自己调用DDR3控制器来实现这个vedio

2015-08-27 14:47:57

如何测量DDR3的VOH(DC)参数

大家好,我在DDR3规格中发现JEDEC79-3E定义VOH(DC)是DC输出高测量级别(用于IV曲线线性)。但是没有关于如何测量高输出直流输出的指南,特别是当信号在高电压时有环时,请参见附图。谁能

2019-04-17 13:59:13

如何用中档FPGA实现高速DDR3存储器控制器?

的工作时钟频率。然而,设计至DDR3的接口也变得更具挑战性。在FPGA中实现高速、高效率的DDR3控制器是一项艰巨的任务。直到最近,只有少数高端(昂贵)的FPGA有支持与高速的DDR3存储器可靠接口的块

2019-08-09 07:42:01

求助,实现一下矩阵的转置函数

本帖最后由 sugarr 于 2012-3-7 10:14 编辑

求助,实现一下矩阵的转置函数function r=rafun(y,M,N)y=reshape(y,M,N);f=@(x

2012-03-07 10:10:04

讲解矩阵运算中的放缩,乘法和转置

第22章 DSP矩阵运算-放缩,乘法和转置矩阵本期教程主要讲解矩阵运算中的放缩,乘法和转置。目录第22章 DSP矩阵运算-放缩,乘法和转置矩阵22.1 初学者重要提示22.2 DSP基础运算指令

2021-08-11 06:05:03

请问为什么DSP需要外接DDR3? DDR3和外接Flash有什么区别和联系?

本帖最后由 一只耳朵怪 于 2018-6-20 11:34 编辑

各位专家好!刚刚学习DSP,还没有入门。实验室购买了TMS320C6678开发板。请问:1、为什么DSP需要外接DDR3?2

2018-06-20 00:40:57

请问如何修改GEL文件中DDR3 PLL配置?

背景:由于使用的是自己做的6678的板子,因此DDR3布线与EVM略有出入,DDR3无法运行在1333速率,只能运行在1066速率。现在想要在板子上实现Nor flash boot,因此尝试

2018-08-06 07:33:54

请问如何在FPGA中实现DDR3 SDRAM功能?

我需要在V7中实现与DDR3 SDRAM相同的功能和接口。这意味着命令/地址,读取数据和写入数据流的方向与MIG的方向不同。这可以实现吗?

2020-07-14 16:18:04

ddr3的读写分离方法有哪些?

DDR3是目前DDR的主流产品,DDR3的读写分离作为DDR最基本也是最常用的部分,本文主要阐述DDR3读写分离的方法。最开始的DDR, 芯片采用的是TSOP封装,管脚露在芯片两侧的,测试起来相当方便;但是,DDRII和III就不一样了,

2017-11-06 13:44:10 8454

8454

8454

8454

ddr4和ddr3内存的区别,可以通用吗

虽然新一代电脑/智能手机用上了DDR4内存,但以往的产品大多还是用的DDR3内存,因此DDR3依旧是主流,DDR4今后将逐渐取代DDR3,成为新的主流,下面我们再来看看DDR4和DDR3内存都有哪些区别。相比上一代DDR3,新一代DDR4内存主要有以下几项核心改变:

2017-11-08 15:42:23 30896

30896

30896

30896基于FPGA的DDR3多端口读写存储管理的设计与实现

为了解决视频图形显示系统中多个端口访问DDR3的数据存储冲突,设计并实现了基于FPGA的DDR3存储管理系统。DDR3存储器控制模块使用MIG生成DDR3控制器,只需通过用户接口信号就能完成DDR3

2017-11-18 18:51:25 6412

6412

6412

6412

基于Digilent介绍DDR3和mig

我们通过Configuration,Package,Speed...等DDR3的命名可知道DDR3的容量,封装,速度等级等信息。

2019-03-03 11:04:15 1909

1909

1909

1909

DDR和DDR2与DDR3的设计资料总结

本文档的主要内容详细介绍的是DDR和DDR2与DDR3的设计资料总结包括了:一、DDR的布线分析与设计,二、DDR电路的信号完整性,三、DDR Layout Guide,四、DDR设计建议,六、DDR design checklist,七、DDR信号完整性

2020-05-29 08:00:00 0

0

0

0DDR4相比DDR3的变更点

DDR4相比DDR3的相关变更点相比DDR3,DDR4存在诸多变更点,其中与硬件设计直接相关的变更点主要有: 增加Vpp电源; VREFDQ删除; CMD、ADD、CTRL命令的端接变更为

2021-11-06 20:36:00 28

28

28

28Virtex7上DDR3的测试例程

这篇文章我们讲一下Virtex7上DDR3的测试例程,Vivado也提供了一个DDR的example,但却是纯Verilog代码,比较复杂,这里我们把DDR3的MIG的IP Core挂在Microblaze下,用很简单的程序就可以进行DDR3的测试。

2022-08-16 10:28:58 1241

1241

1241

1241FPGA学习-DDR3

一、DDR3简介 DDR3全称double-data-rate 3 synchronous dynamic RAM,即第三代双倍速率同步动态随机存储器。所谓同步,是指DDR3数据

2022-12-21 18:30:05 1915

1915

1915

1915阐述DDR3读写分离的方法

DDR3是2007年推出的,预计2022年DDR3的市场份额将降至8%或以下。但原理都是一样的,DDR3的读写分离作为DDR最基本也是最常用的部分,本文主要阐述DDR3读写分离的方法。

2023-10-18 16:03:56 518

518

518

518

DDR4和DDR3内存都有哪些区别?

DDR4和DDR3内存都有哪些区别? 随着计算机的日益发展,内存也越来越重要。DDR3和DDR4是两种用于计算机内存的标准。随着DDR4内存的逐渐普及,更多的人开始对两者有了更多的关注。 DDR3

2023-10-30 09:22:00 3905

3905

3905

3905 电子发烧友App

电子发烧友App

评论