前几天看到有人讨论如何实现分频时钟÷2,÷4,÷8,÷16之间的切换。

其实这个分频时钟切换很简单,根本不需要额外的切换电路。一个共用的计数器,加一点控制逻辑,就可以了,而且可以实现2到16任意整数分频率之间的无缝切换。

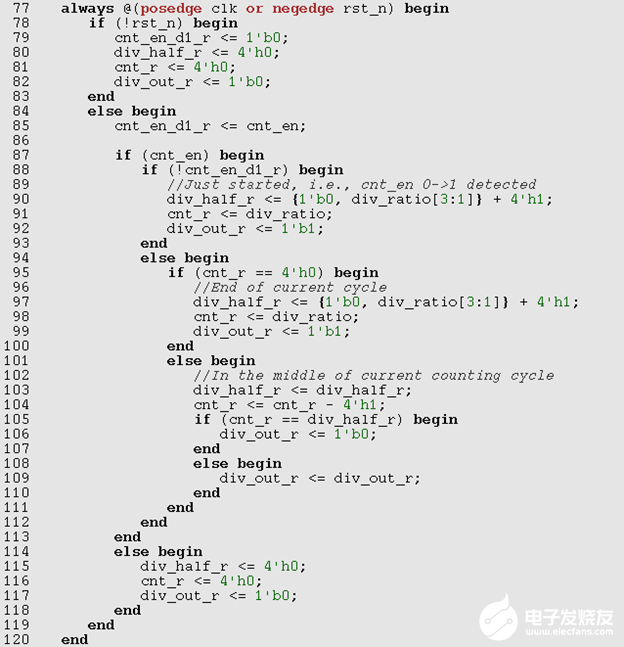

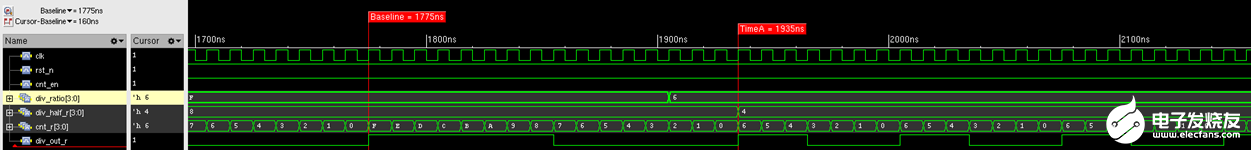

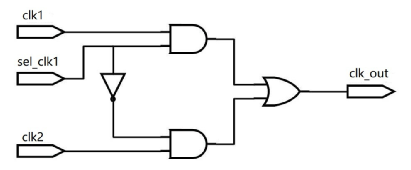

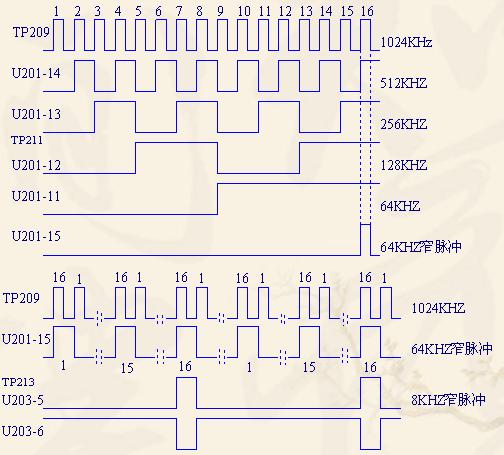

RTL示意如下。这里的关键是要等当前周期跑到最后才切换到新的分频率。这样才能保障输出总是一个完整的周期,不会出现不规则的周期。

这里没有加奇数分频占空比调整。如果希望奇数分频后占空比是50-50,要再加一个negedge DFF,再加一个OR,很简单的,就不赘述了。

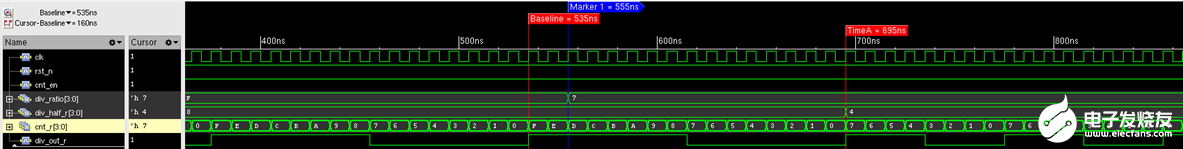

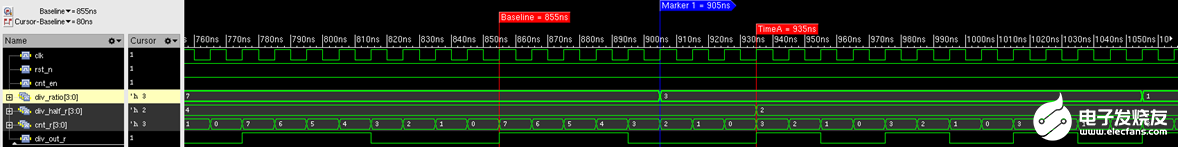

Divide 16 to divide 8

Divide 8 to divide 4

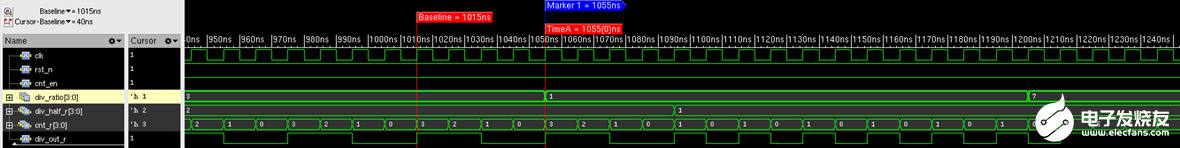

Divide 4 to divide 2

Divide 2 to divide 8

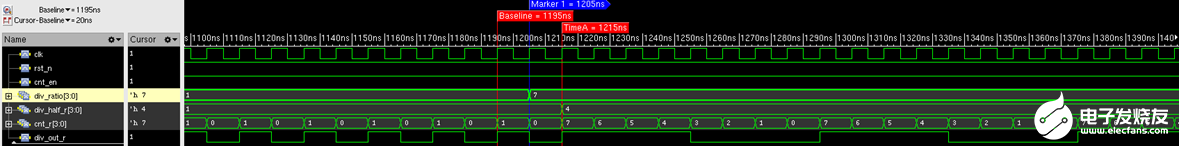

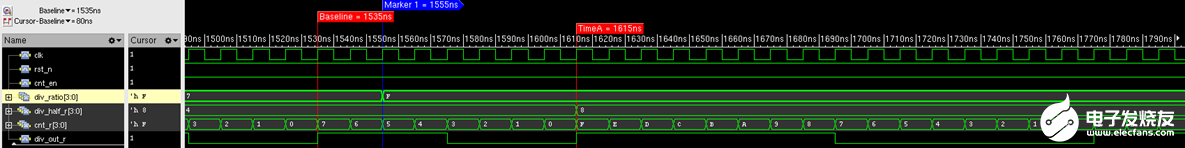

Divide 8 to divide 16

Divide 16 to divide 7

审核编辑:黄飞

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

计数器

+关注

关注

32文章

2321浏览量

98580 -

时钟设计

+关注

关注

0文章

29浏览量

11199 -

控制逻辑

+关注

关注

0文章

14浏览量

2607

发布评论请先 登录

相关推荐

热点推荐

SPARTAN 3E上的时钟分频怎么实现?

你好,我需要在SPARTAN 3E上实现运行时,用户可切换的时钟分频。它适用于用户可以在VGA(25MHz像素时钟)或SVGA(50MHz)

发表于 06-20 11:56

时钟切换模式是如何工作的?

嗨,伙计,我使用PIC18F97 J94。目前,我的问题是动态切换时钟(振荡器)。我在切换前的设置是:OSCCONbits.COSC0=1;//快速RC振荡器(FRC)除以N个

发表于 11-01 07:49

基于FPGA的高频时钟的分频和分配设计

摘要:介绍了为PET(正电子发射断层扫描仪)的前端电子学模块提供时间基准而设计的一种新型高频时钟扇出电路。该电路利用FPGA芯片来实现对高频时钟的分频

发表于 06-20 12:41

•1580次阅读

如何理解STM32系统时钟和分频

STM32中有一个全速功能的USB模块,其串行接口引擎需要一个频率为48MHz的时钟源。该时钟源只能从PLL输出端获取,可以选择为1.5分频或者1分频,也就是,当需要使用USB模块时,

发表于 11-30 09:14

•8838次阅读

verilog的时钟分频与时钟使能

时钟使能电路是同步设计的基本电路,在很多设计中,虽然内部不同模块的处理速度不同,但由于这些时钟是同源的,可以将它们转化为单一时钟处理;在ASIC中可以通过STA约束让分频始终和源

时钟切换电路设计方案

随着各种应用场景的限制,芯片在运行时往往需要在不同的应用下切换不同的时钟源,例如低功耗和高性能模式就分别需要低频率和高频率的时钟。两个时钟源有可能是同源且频率比呈倍数关系,也有可能是不

如何实现分频时钟的切换

如何实现分频时钟的切换

评论