如何具体实现输出信号的分频和倍频?

在现代电子系统中,信号分频和倍频是非常常见的技术。它们可以帮助电子设备在处理信号时具有更高的精度和准确性。下面我将详细介绍如何实现输出信号的分频和倍频。

一、分频

1. 什么是分频?

分频是一种将一个信号分成多个周期的技术。简单来说,就是使输出信号的周期数变为输入信号的周期数的整数倍。当信号进行分频后,频率就会降低,而信号却保持原来的形态(波形)。

2. 如何实现分频?

实现分频的方案有很多,其中常用的有如下几种:

(1)分频器

分频器是最常见的分频方案之一。它通常采用计数器/定时器来实现。在分频器的输出中,一个周期包含的时钟脉冲数量是输入的周期数的整数倍。例如,如果输入信号的频率为1kHz,要将其分成1/10,则分频器每10个输入周期输出1个时钟脉冲,就像下面这样:

(2)PLL

PLL(Phase-Locked Loop)是一种以输入信号为参考信号,在输出信号中保持相位,同时放大和分频信号的技术。在使用PLL实现分频时,输入的参考信号在PLL内部被倍频或分频。背后的基本原理是相位检测环路,这是一个闭环反馈系统,它将参考信号与PLL内部产生的信号进行比较并调整输出信号的相位和频率,使得输出信号的频率是参考信号的整数分频倍数。

二、倍频

1. 什么是倍频?

倍频是一种将输入信号的频率乘以整数的技术。换句话说,在输出信号中,每个周期包含的时钟脉冲数量是输入的周期数的整数倍。倍频技术通常用于高频率信号的产生,例如,将本来的低频信号经过倍频后,可以得到更高的频率信号。

2. 如何实现倍频?

实现倍频的方案也有很多,其中常用的有如下几种:

(1)倍频器

倍频器可以将输入信号的频率提高一个整数倍。它通常是由一个振荡器和一个频率加倍电路组成。在输出中,时钟脉冲的数量比输入的周期数多。例如,将输入信号频率倍增成2MHz,输出的时钟脉冲的数量是输入信号的周期数的两倍。

(2)锁相环倍频器

锁相环倍频器(PLL)是一种基于相位锁定环路的技术,它可以将输入信号的频率倍增。PLL系统由几个重要的组件组成,如分频器、相位检测器、VCO(Voltage Controlled Oscillator)等。

输入信号经过分频器后,变成PLL系统的参考频率,反馈给相位检测器。相位检测器输出的信号会驱动VCO发生变动。当经过一段时间后,VCO输出信号的频率和输入信号的频率趋于一致和稳定,PLL系统达到相位锁定的效果。此时输出信号的频率为输入信号的频率的整数倍。例如,输入信号的频率为1MHz,通过PLL技术倍增10倍后,输出的信号频率为10MHz。

以上是分频和倍频技术的实现方案。在实际应用中,可以根据具体的需求来选择适合的技术方案。同时,设计者也应注意到不同技术方案的优缺点,从而合理利用,提高电子系统的性能。

-

分频器

+关注

关注

43文章

537浏览量

53727 -

pll

+关注

关注

6文章

988浏览量

138356 -

倍频器

+关注

关注

8文章

124浏览量

37457

发布评论请先 登录

CDC5801A:低抖动时钟倍频器与分频器的卓越之选

晶振倍频率干扰的解决方法

音响中软件分频和硬件分频区别解析以及对音质和成本的影响

数据滤波算法的具体实现步骤是怎样的?

CDC5801A低抖动时钟倍频/分频器技术文档总结

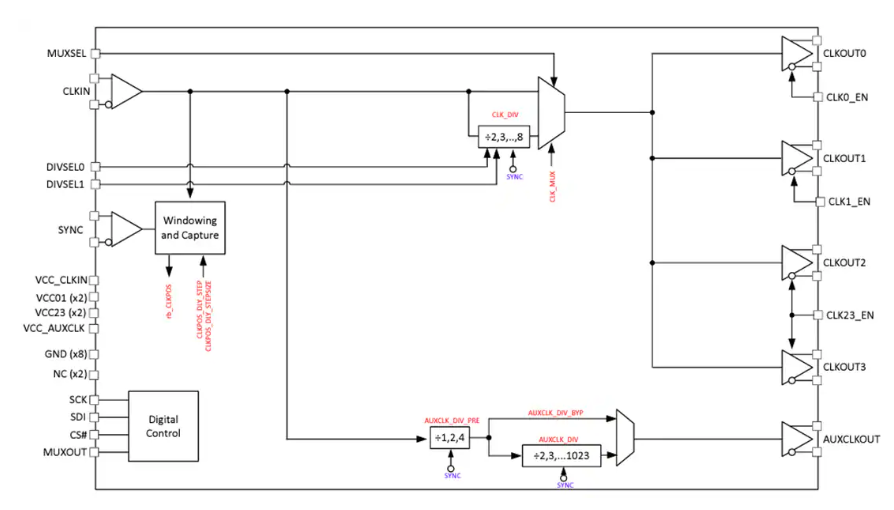

CDCLVD1213 1:4低附加抖动LVDS缓冲器带分频器 技术文档摘要

LMX1204低噪声高频JESD缓冲器/倍频器/分频器技术解析

德州仪器LMX1214射频缓冲器与分频器技术解析

24V、1000MHz 高输出功率倍频器线路放大器 MMIC skyworksinc

Analog Devices Inc. ADF4382x小数N分频锁相环 (PLL)数据手册

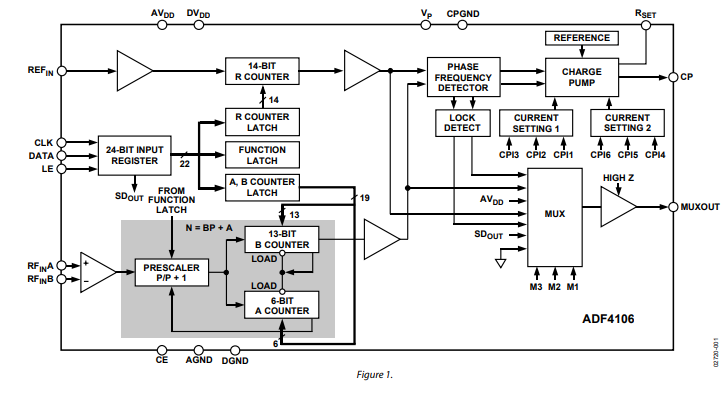

ADF4106 6GHz整数N分频PLL技术手册

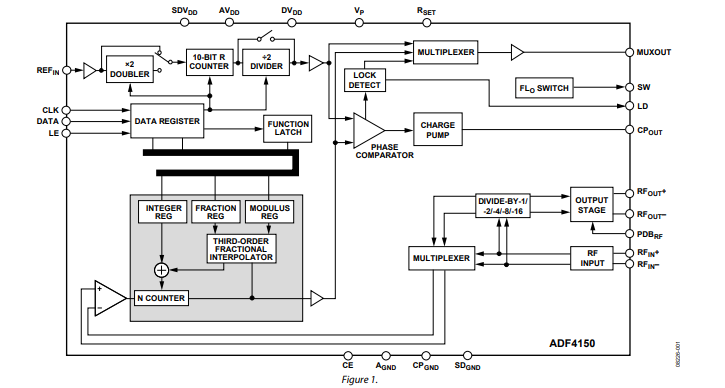

ADF4150小数N/整数N分频PLL频率合成器技术手册

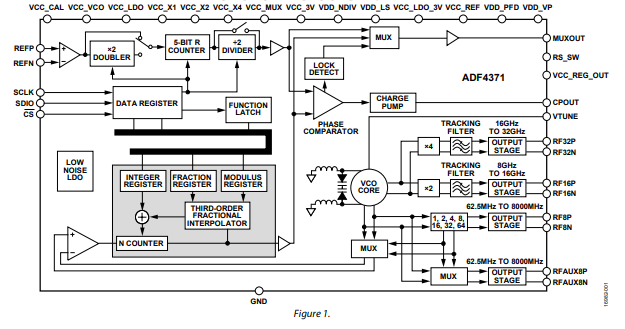

ADF4371带集成VCO的微波宽带合成器技术手册

如何具体实现输出信号的分频和倍频?

如何具体实现输出信号的分频和倍频?

评论