编程语言及工具

电子发烧友网编程语言及工具栏目提供嵌入式设计所需的嵌入式编程语言技术和开发工具以及最新设计相关内容,是嵌入式工程师喜欢的网站。UDT是什么?关于PLC中UDT和FB的问题

UDT是什么?用户自定义数据类型。所以,它更应该和系统已经内置的简单数据类型和复杂数据类型(如DTL,LTD等)功能一样,能实现同样的功能。...

2023-09-22 2433

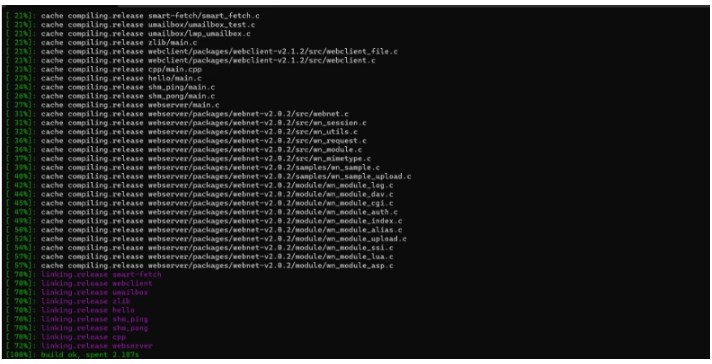

镜像体积从1000M到10M的优化技巧

分阶段构建(multi-stage builds)和从零构建(build from scratch)是优化镜像体积的基本手段和必备技巧。该技巧将镜像构建过程区分为构建和运行环境,在构建环境安装编译器等依赖并编译所需的二...

2023-09-21 1046

可定制RISC-V ISA的优势

多样性与兼容性的统一 处理器供应商一直试图在其产品周围创建一个庞大的软件生态系统,因为这可以产生黏性,自然而然地 "锁定 "大量投资于创建专用软件的客户。随着时间的推移,这种效...

2023-09-21 1719

什么是DFX技术?DFX设计一定要执行设计规则检查吗?

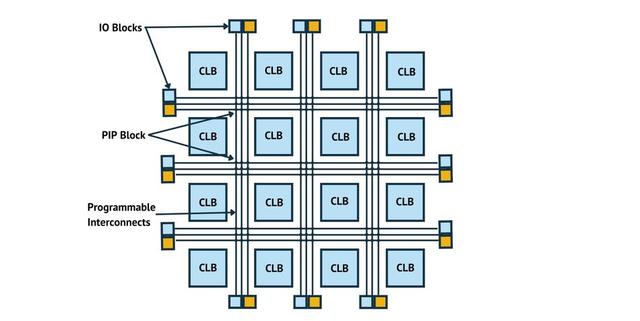

DFX(Dynamic Function eXchange)的前身是PR(部分可重配置,Partial Reconfiguration)。...

2023-09-21 9342

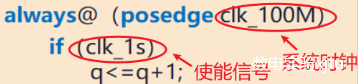

如何在开始码代码的时候就考虑时序收敛的问题?

硬件描述语言(verilog,systemVerilog,VHDL等)不同于软件语言(C,C++等)的一点就是,代码对应于硬件实现,不同的代码风格影响硬件的实现效果。...

2023-09-21 2319

mysql分页问题和优化的思路是什么

server层会调用innodb的接口,在innodb里的非主键索引中获取到第0条数据对应的主键id后,回表到主键索引中找到对应的完整行数据,然后返回给server层,server层将其放到结果集中,返回给客户端。...

2023-09-20 855

嵌入式C语言中的结构是什么?

在介绍结构之后,将看一下这个强大数据对象的一些重要应用。然后将检查C语言语法以声明结构。最后将简要介绍数据对齐要求。可以通过简单地重新排列其成员的顺序来减小结构的大小。...

2023-09-20 961

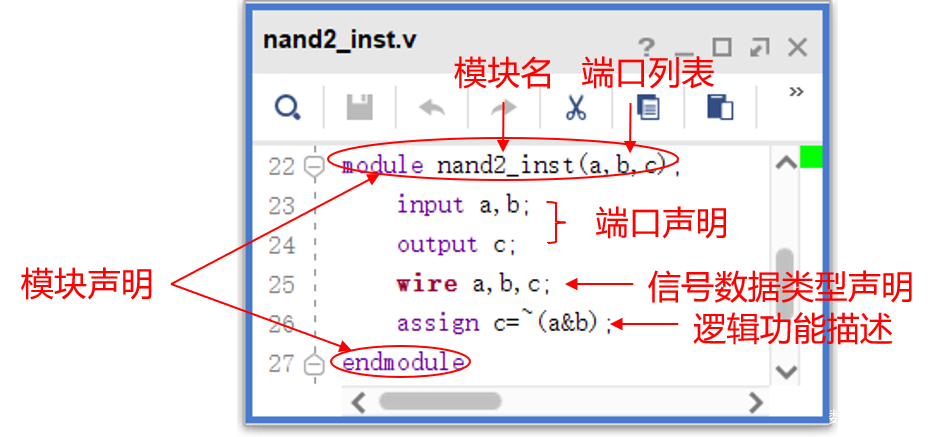

Mojo v3 FPGA板与16x2 LCD模块是如何进行连接的呢?

在本教程中,我们将使用Verilog HDL设计一个数字电路,该电路与基于HD44780 LCD控制器/驱动芯片的通用LCD模块连接。Mojo V3 FPGA板将用于实现设计。本文中使用的LCD模块是1602A显示器。...

2023-09-20 1548

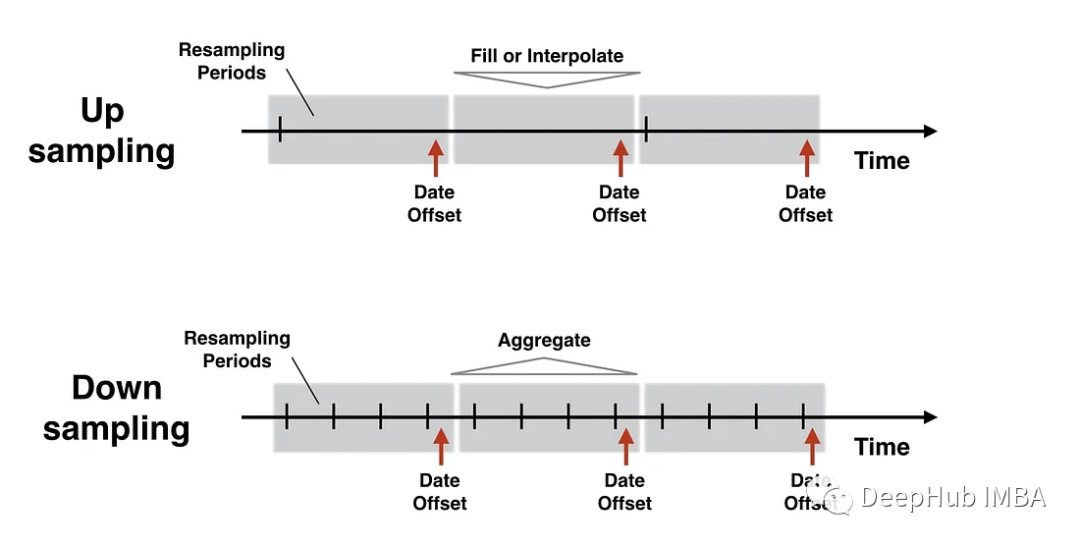

为什么重采样很重要?Pandas中重新采样的关键问题解析

重采样是时间序列分析中处理时序数据的一项基本技术。它是关于将时间序列数据从一个频率转换到另一个频率,它可以更改数据的时间间隔,通过上采样增加粒度,或通过下采样减少粒度。...

2023-09-19 3686

如何在Rust中高效地操作文件

Rust语言是一种系统级、高性能的编程语言,其设计目标是确保安全和并发性。 Rust语言以C和C++为基础,但是对于安全性和并发性做出了很大的改进。 在Rust语言中,操作文件是非常重要的一个功...

2023-09-19 3386

在QEMU/aarch64上完成smart用户态应用的运行并使用VSCode进行调试

这里注意如果是linux平台下需要先安装解压缩工具,下面为7zip的下载方式...

2023-09-18 2923

为什么说Vivado是基于IP的设计?

Vivado是Xilinx公司2012年推出的新一代集成开发环境,它强调系统级的设计思想及以IP为核心的设计理念,突出IP核在数字系统设计中的作用。...

2023-09-17 3063

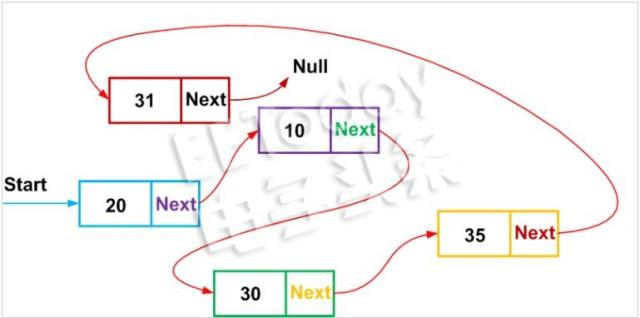

free在释放内存的时候,为什么不需要指定内存的大小?

malloc在申请内存的时候,需要指定内存的大小,申请成功则返回这块内存的地址,但是free的时候,只需要指定释放的内存的起始地址,系统就知道从这个地址开始需要释放多少个字节。...

2023-09-15 2229

什么是逻辑综合?逻辑综合的流程有哪些?

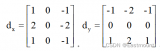

逻辑综合是将RTL描述的电路转换成门级描述的电路,将HDL语言描述的电路转换为性能、面积和时序等因素约束下的门级电路网表。...

2023-09-15 7193

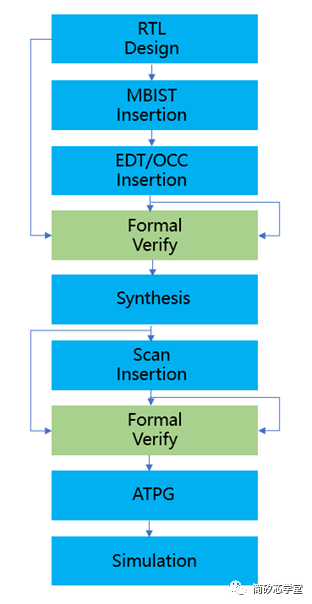

Formal Verify形式验证的流程概述

Formal Verify,即形式验证,主要思想是通过使用数学证明的方式来验证一个修改后的设计和它原始的设计,在功能上是否等价。...

2023-09-15 2214

vscode+pyocd+daplink调试瑞萨ra6m3步骤

拿到了瑞萨的ra6m3的板子,发现使用RT-Thread Stduio下载速度很慢,就想着搭建一个vscode的环境试试。...

2023-09-14 2806

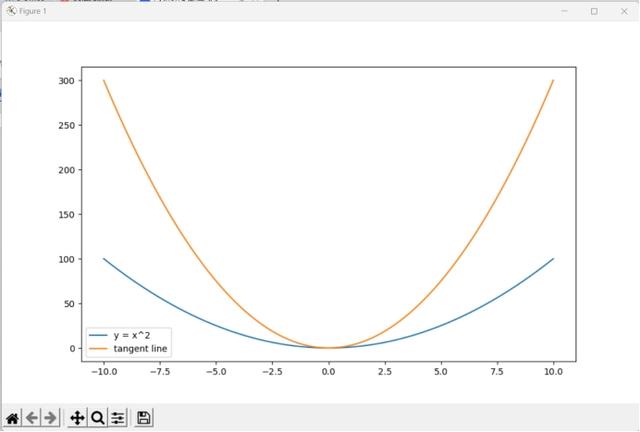

如何用Python实现Vivado和ModelSim仿真自动化?

我们在Windows系统下使用Vivado的默认设置调用第三方仿真器比如ModelSim进行仿真时,一开始仿真软件都会默认在波形界面中加载testbench顶层的信号波形...

2023-09-13 2533

编辑推荐厂商产品技术软件/工具OS/语言教程专题

| 电机控制 | DSP | 氮化镓 | 功率放大器 | ChatGPT | 自动驾驶 | TI | 瑞萨电子 |

| BLDC | PLC | 碳化硅 | 二极管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 无刷电机 | FOC | IGBT | 逆变器 | 文心一言 | 5G | 英飞凌 | 罗姆 |

| 直流电机 | PID | MOSFET | 传感器 | 人工智能 | 物联网 | NXP | 赛灵思 |

| 步进电机 | SPWM | 充电桩 | IPM | 机器视觉 | 无人机 | 三菱电机 | ST |

| 伺服电机 | SVPWM | 光伏发电 | UPS | AR | 智能电网 | 国民技术 | Microchip |

| 开关电源 | 步进电机 | 无线充电 | LabVIEW | EMC | PLC | OLED | 单片机 |

| 5G | m2m | DSP | MCU | ASIC | CPU | ROM | DRAM |

| NB-IoT | LoRa | Zigbee | NFC | 蓝牙 | RFID | Wi-Fi | SIGFOX |

| Type-C | USB | 以太网 | 仿真器 | RISC | RAM | 寄存器 | GPU |

| 语音识别 | 万用表 | CPLD | 耦合 | 电路仿真 | 电容滤波 | 保护电路 | 看门狗 |

| CAN | CSI | DSI | DVI | Ethernet | HDMI | I2C | RS-485 |

| SDI | nas | DMA | HomeKit | 阈值电压 | UART | 机器学习 | TensorFlow |

| Arduino | BeagleBone | 树莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 华秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |