什么是DFX技术?

DFX(Dynamic Function eXchange)的前身是PR(部分可重配置,Partial Reconfiguration)。使用DFX这个名字更能准确描述其功能,即在线切换设计中某个模块的功能。我们把这个模块对应的FPGA物理区域称之为一个可重配置分区(RP,ReconfigurablePartition)。同一个RP下可动态切换的模块称之为可重配置模块(RM,Reconfigurable Module)。一个RP下可以有一个或多个RM。每个RP要通过手工布局(画Pblock)的方式指定其在FPGA中的具体位置和大小(位置约束+面积约束)。

DFX对RM有什么要求?

首先,同一个RP下的所有RM必须保证端口一致,即输入/输出方向一致、位宽一致。即使某个RM中使用的端口在另一个RM中未被使用,也要在该RM中进行端口声明。其次,本身DFX设计对设计的层次化要求更高,对RM必须采用OOC综合方式,因此,要避免在RM中使用Parameter(Verilog)或Generic(VHDL)。最后,RM的顶层必须是RTL代码(可以是BD的wrapper文件),不能是IP或着网表文件,同时RM下不能包含EDIF或DCP等网表文件,但可以包含IP(.xci)文件。

需要对RP进行手工布局吗?

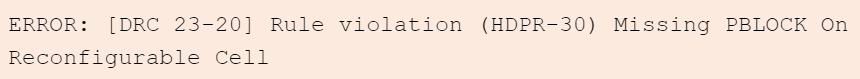

DFX设计要求必须对动态区也就是RP进行手工布局,即通过Pblock来约束RP的位置和大小,同时Pblock的形状尽可能为规则的矩形,避免出现奇形怪状,这会对布局布线带来较大压力。对于静态区,则可以不用手工布局。如果对动态区没有做Pblock约束,那么会报如下错误:

DFX设计一定要执行设计规则检查吗?

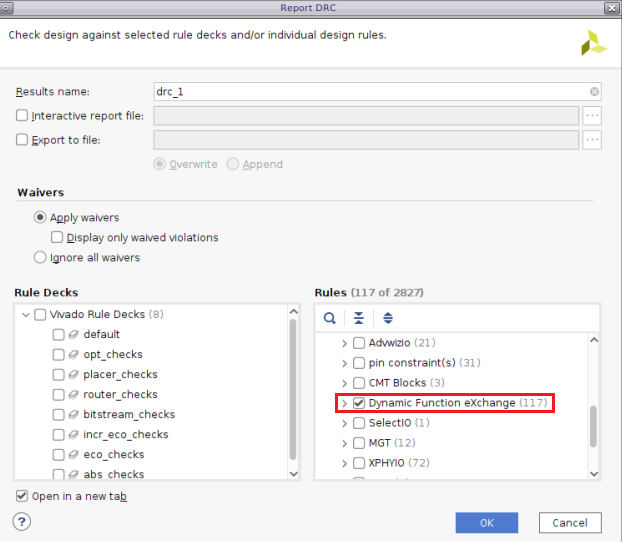

相比于传统设计,DFX设计较为复杂,无论是从设计本身(RTL代码的层次化、约束)的角度看还是工具的使用角度看,都是如此。因此,在综合后,一定要执行设计规则检查,如下图所示。这样能尽早发现设计可能存在的问题。这里并不需要对所有规则都做检查,只需要检查DFX相关的规则即可。这样可以节省时间。

可以对同一RP下不同的RM添加不同的约束吗?

假定RP1下有两个RM,分别为RM1和RM2,由于RM1和RM2本身功能并不相同,因此可能就存在一些约束层面的差异。例如:在RM1里需要对某些路径添加set_max_delay约束,在RM2里则需要对一些路径添加set_false_path约束。这就要求对不同的RM施加不同的约束。对此,Vivado是支持的,无论是Project模式还是Non-Project模式。具体操作可阅读这篇文章。

如何给每个RM添加约束?

BD可以用作动态区的顶层吗?

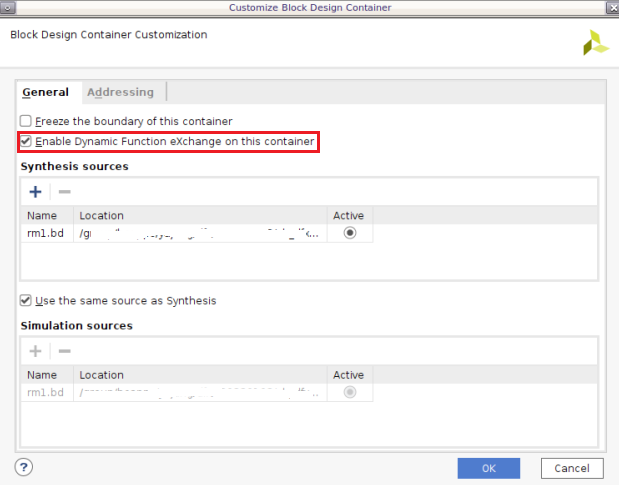

这个问题的本质是RM是否可以用BD创建。答案是肯定的。只是这时需要将BD设计转换为BDC(Block Design Container),勾选下图中的红色方框所示内容即表明该模块是一个RM。

除了上述几个问题之外,我们还需要从以下角度来看待DFX设计。

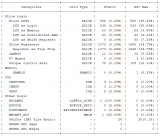

DFX设计本质上是FPGA内嵌入了FPGA,也就是说RP可视为一个内嵌的FPGA,那么这个RP的可用逻辑资源、布线资源和IO也就固定了。正因此,RP的Pblock的大小和形状对设计性能有较大影响,同时,RM的输出/输出端口个数应尽可能少,过多的IO个数大概率会导致布线拥塞。因此,同样的设计,使用DFX和不使用DFX可能会有不同的时序结果。层次化设计在DFX设计中也非常重要,将直接影响合动态区和静态区的分割。

审核编辑:刘清

-

FPGA

+关注

关注

1664文章

22502浏览量

639237 -

VHDL语言

+关注

关注

1文章

113浏览量

19462 -

RTL

+关注

关注

1文章

395浏览量

62883 -

DCP

+关注

关注

0文章

30浏览量

17909 -

dfx设计

+关注

关注

0文章

6浏览量

268

原文标题:DFX设计中的常见问题

文章出处:【微信号:Lauren_FPGA,微信公众号:FPGA技术驿站】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

DFX设计如何分析

招兼职dfx、dfm培训讲师

硬件电路设计中常见的DFX

硬件电路常见的DFX设计环节详解

简述DFX理念与产品研发(一)

简要分析DFX实施流程

DFX极大地提高了Xilinx FPGA芯片的灵活性

2021华为开发者大会亮点 HarmonyOS架构演进与关键技术-HarmonyOS对DFX能力的要求是什么

HarmonyOS对DFX能力的要求

如何在AMD Vivado™ Design Tool中用工程模式使用DFX流程?

什么是DFX技术?DFX设计一定要执行设计规则检查吗?

什么是DFX技术?DFX设计一定要执行设计规则检查吗?

评论