今天分享蒸汽发生器原理、蒸汽发生器的工作原理、蒸汽发生器的特点、蒸汽发生器的优点、蒸汽发生器的作用以及蒸汽发生器的应用领域。

2012-06-03 00:17:17 24278

24278 和信号处理知识产权(IP)内核供应商The Athena Group, Inc. (Athena)发布具有先进侧通道分析(SCA)和差分功率分析(DPA)对策的全面IP内核产品组合。

2015-12-11 13:56:48 1589

1589 是德科技推出一款双通道微波信号发生器,该产品可在同一台仪器中支持最高 44 GHz 的信号和 2 GHz 的射频(RF)调制带宽。

2019-02-27 09:15:14 1642

1642 系列。Actel的ProASIC Plus车用器件专为要求高度灵活和可靠解决方案的远程信息处理及其它驾驶室内应用而优化,包括导航、语音识别、乘客控制及舒适系统、智能乘客传感器及行驶仪表盘。此外

2008-07-25 12:31:34

大家好我正在尝试进行FFT,但看起来FFT内核的输出存在问题!我正在进行1024点FFT,实时,流水线流I / O,定点和缩放,我的输入是200khz的正弦波,XADC的采样频率约为427 ksps

2020-05-08 09:53:16

嗨我正在制作OFDM,我想从ip core genrator中获取FFT / IFFT块。所以不能这样做,所以我可以在我的设计中添加这个IP,而不是我想将它与我的模块链接???????谢谢以上

2018-10-08 17:42:13

(LVDS工作模式) AD9571ACPZPEC产品详情AD9571具有多路输出时钟发生器功能,内置专用PLL内核,针对以太网线路卡应用进行了优化。整数N PLL设计基于ADI公司成熟的高性能、低抖动

2019-07-09 10:19:09

/nfs-kernel-server RPCNFSDOPTS="--nfs-version 2,3,4 --debug --syslog" //让服务器可以支持我们内核之后将linux内核发

2022-05-26 16:40:48

,2002年中期推出,0.13um工艺,1.5v内核供电。集成硬件乘加器,芯片内部结构比Altera以前的产品有很大变化。 简评:Startix芯片在2002年的推出,改变了Altera在FPGA市场上

2018-08-20 09:52:02

匹配的IP内核。这些免费的IP内核可能涵盖了多种功能模块,如FIFO、RAM、FIR滤波器、SDRAM控制器、PCIE接口等。例如,如果需要处理数据队列,那么FIFO IP内核可能是一个很好的选择

2024-04-28 09:41:04

大家好,FPGA设计中的IP内核寄存器在哪里?我正在进行模拟,并希望使用软件复位寄存器发出软件复位,但不知道如何访问该寄存器空间。谢谢,山姆

2020-05-21 07:01:56

一种基于SOPC的MVB总线访问IP内核和网卡的设计

2021-05-27 06:29:20

为什么每次运行模拟时,Vivado内置模拟器都需要重新分析项目中的所有IP内核?即使没有对任何设计文件进行任何更改,也会发生这种情况。是否有一个我缺少的设置来禁用此功能,或者编译时间长是Vivado设计环境的一个非常糟糕的方面?

2020-03-19 07:59:48

s5pv210是三星公司推出的32位RISC微处理器,其CPU采用的是ARM Cortex-A8内核,基于ARMv7架构,这里的内核和架构是什么意思???

2015-03-25 12:09:45

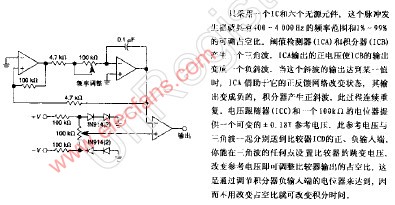

、衰减网络、功率输出。图一 iBoard 任意波发生器硬件框图CPU电路:通过高性能Cortex-M3内核的微处理器 STM32F103VC,完成任意波发生器的主控、人机界面、接口等功能...

2021-08-09 07:53:05

在波特率发生器的提示信号驱动下进行计数。UART 内核在计数器到达计数上阈后便进入发送完成模式,并且输出发送完成信号。

2018-10-24 10:06:14

信号发生器与波束赋形算法的配合优化是无线通信系统(如5G毫米波、卫星通信、雷达系统)中提升信号质量、覆盖范围和抗干扰能力的关键环节。其核心在于通过信号发生器生成高精度、动态可调的测试信号,模拟真实

2025-08-08 14:41:35

SiFive推出的SiFive U8系列核心IP是一种面向现代SoC设计具有可扩展性、高性能的微架构。SiFive U8系列是当今商用化基于RISC-V指令集架构中性能最高的内核IP,它具有超标

2020-08-13 15:14:50

很久不见了再次见到小编是不是很开心和激动呢接下来就跟着小编一起学习吧PART 1引言STM32是ST(意法半导体)公司推出的基于ARM内核Cortex-M3的32位微控制器系列。Cortex-M3

2021-08-18 06:28:37

ARM920T内核中实现基 4 时间抽取的快速傅里叶变换算法(fastFouriertransform,FFT)。实验结果表明,该雷达测速仪的测速精度可达±1km/h,其优化后的 FFT 算法具有很高的精度和运行效率。

2014-07-24 14:14:20

我毕业设计要做一个基于FPGA的IP核的DDS信号发生器,但是我不会用DDS的IP核,有没有好人能发我一份资料如何用IP核的呀。我的浏览器下载不了网站上的资料,所以只能发帖求帮忙了。

2015-03-10 11:46:40

嗨,我目前正在使用Virtex-5 110T(1136)Rocket IP内核来控制发射器。有没有办法让我用外部引脚复位IP内核?这样我可以使用外部信号来启用或禁用IP内核?非常感谢 !

2020-06-02 16:32:24

系列,该系列由Arm开发,采取IP授权的形式,Cortex-M系列具有短流水线、超低功耗的设计特点。2004年,Arm推出了其第一款Cortex-M系列处理器M3,发展至今,不论是国内,还是国外

2022-07-29 11:35:58

怎么实现基于IP内核的PCI总线接口设计?

2021-05-27 06:34:05

概述:AD9577是一款既提供一个多路输出时钟发生器功能,又带有两个片上锁相环内核PLL1和PLL2,专门针对网络时钟应用而优化。PLL设计基于ADI公司成熟的高性能、低抖动频率合成器产品系列,确保实现最高的网

2021-04-06 06:49:57

嗨,是否有Xilinx提供的视频LVDS serdes发送器/接收器IP内核?如果是这样请分享详细信息。

2020-05-22 14:34:10

AD9576 / PCBZ,AD9576评估板提供多输出时钟发生器功能,包括两个专用锁相环(PLL)内核,具有灵活的频率转换功能,经过优化,可作为整个系统的强大异步时钟源,提供扩展功能通过监控和冗余

2019-02-25 09:40:01

对蜂鸟E203内核进行优化可以考虑以下几个方面:

编译器优化:使用适合蜂鸟E203的编译器选项和指令集,优化编译器的选项和参数,开启对硬件的特定支持,比如使用-O2等优化选项,以提高代码执行效率

2025-10-21 07:55:16

ACTEL公司的FPGA如何使用SDRAM内核工具去控制一个SDRAM芯片的读写操作,刚刚接触不是很懂,请大家多多指教,谢谢了

2019-04-19 03:08:28

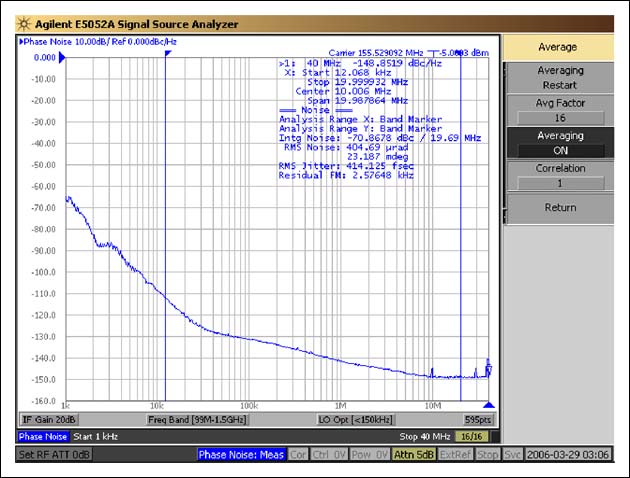

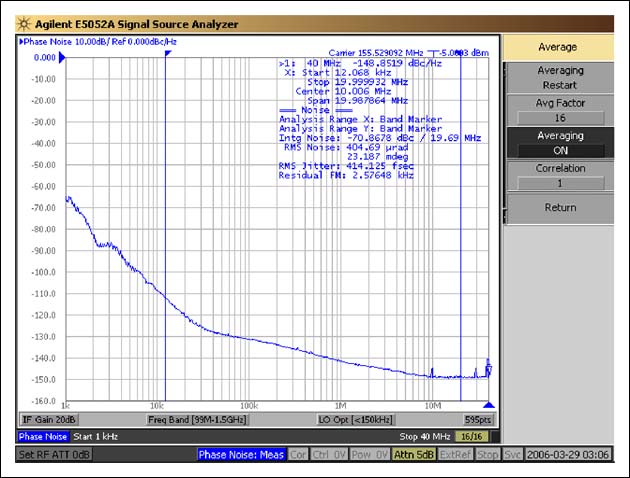

*信号发生器基础知识和新应用的问题与解答* 2013年1月30日的网络直播问题:您是否可以调整信号发生器的PLL BW以优化相位噪声? 以上来自于谷歌翻译 以下为原文Questions

2019-07-19 08:25:02

鸿蒙虚拟内存全景图图来自 鸿蒙内核源码注释中文版 【Gitee仓 】再看鸿蒙用户空间全景图图来自 鸿蒙内核源码注释中文版 【Gitee仓 || Github仓 | Coding仓 】 以上两图

2020-11-19 10:14:53

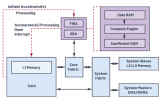

CoreFFT 是Actel 公司提供的基于Actel FPGA 结构优化的微秒级FFT 运算软核,为客户提供功能强大和高效的DSP 解决方案。CoreFFT 应用于Actel 以Flash 和反熔丝技术为基础的现场可编程门

2010-11-15 17:39:28 46

46 Actel公司推出专为Actel FPGA应用而优化的软ARM7系列处理器CoreMP7,将可编程逻辑的设计灵活性和快速上市优势带到这个行业标准的处理器技术中。 &

2006-03-13 13:04:25 1113

1113 Actel公司宣布推出90项知识产权 (IP) 内核,支持其崭新的ProASIC3和ProASIC3E系列器件,进一步实现该公司的承诺,成功发展全新的现场可编程门阵列 (FPGA) 。这些IP

2006-03-24 13:32:36 1310

1310 利用FFT IP Core实现FFT算法

摘要:结合工程实践,介绍了一种利用FFT IP Core实现FFT的方法,设计能同时对两路实数序列进行256点FFT运算,并对转换结果进行求

2008-01-16 10:04:58 8045

8045

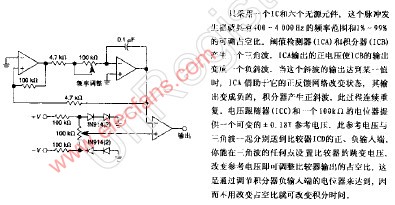

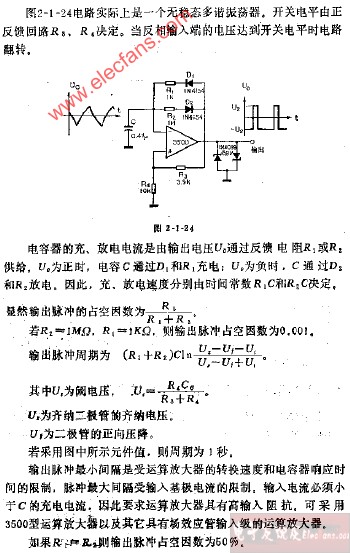

具有对称输出的钟脉冲发生器

2009-03-21 09:15:15 397

397

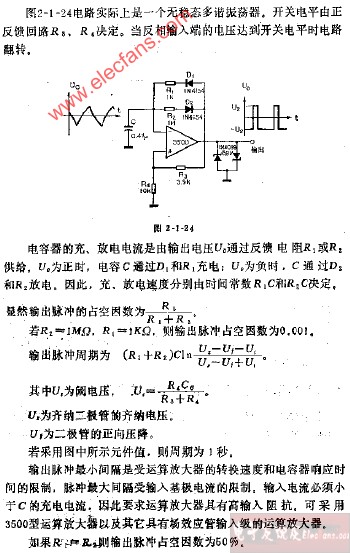

具有低占空因数的脉冲发生器

2009-03-23 10:02:29 415

415

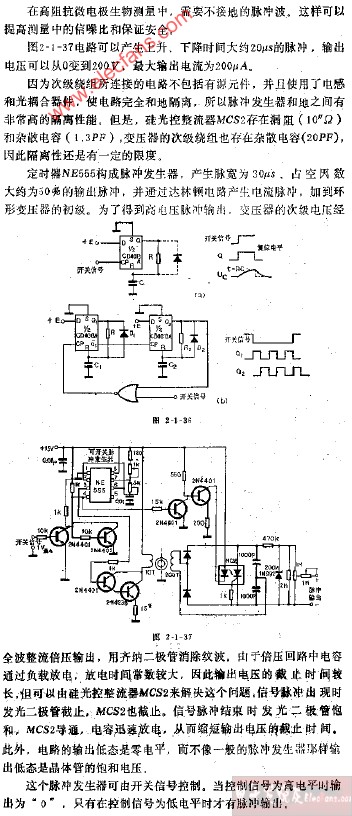

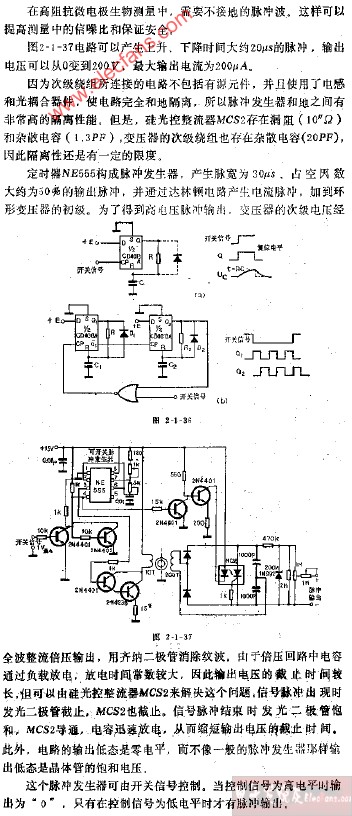

具有高隔离性的脉冲发生器

2009-03-23 10:03:06 491

491

具有抑制噪声能力的选通脉冲发生器

2009-04-03 09:42:39 382

382

摘要:MAX9450/MAX9451/MAX9452是集成了VCXO,具有相同PLL内核和三种不同输出(LVPECL, HSTL,LVDS)的高精度时钟发生器。MAX945x时钟发生器具有四个主要的特点:集成VCXO,工作频率范围宽,PLL

2009-04-22 09:42:01 1345

1345

具有可变占空比的脉冲发生器

2009-10-05 15:49:38 663

663

Actel增强Fusion混合信号FPGA IP产品系列

爱特公司(Actel Corporation)宣布推出与其子公司Pigeon Point Systems携手开发的硬件平台管理应用的IP内核增强组件。全新的增强内核

2009-11-25 09:41:01 1132

1132 Actel增强用于xTCA平台管理应用的Fusion混合信号FPGA IP产品系列

特公司(Actel Corporation)宣布推出与其子公司Pigeon Point Systems携手开发的硬件平台管理应用的IP内核增强组件。

2009-11-26 08:35:28 907

907 MOXAIR推出PowerPure Hardware逻辑内核

Moxair公司日前宣布正式推出全新的Moxair PowerPure Hardware逻辑内核,这一创新性的产品可节省高达70%的显示屏能耗,从

2009-12-08 09:43:08 999

999 LSI推出PowerPC 476 MCU内核和高速嵌入式DRAM内存模块

LSI公司日前宣布推出具有多核功能的 PowerPC 476 微处理器内核和高速嵌入式 DRAM 内存模块,进一步丰富了其业界领先的

2010-02-03 08:56:44 996

996 德州仪器推出12导轨定序发生器与系统安全管理器

德州仪器 (TI) 宣布推出业界首款具有风扇控制和多相脉宽时钟发生器功能的 12 导轨定序发生器与系统安全管理器。

2010-03-05 11:50:41 1063

1063 TI推出12导轨定序发生器与系统安全管理器UCD90124

德州仪器 (TI) 宣布推出业界首款具有风扇控制和多相脉宽时钟发生器功能的12导轨定序发生器与系统安全管理器。该款UC

2010-03-08 10:01:39 824

824 Altera公司日前宣布,开始提供业界第一款集成增强前向纠错(EFEC) IP内核,该内核针对高性能Stratix IV和Stratix V系列FPGA进行了优化。

2011-03-09 09:42:31 1433

1433 德州仪器(TI)(纽约证券交易所代码:TXN)今天宣布推出一款具有业界最佳抖动性能的高度集成的时钟发生器。LMK03806可以帮助设计人员运用一个低成本晶体合成所需的时钟频率,从而

2011-10-08 11:36:42 1062

1062 IP授权厂商MIPS推出Aptiv系列处理器内核,针对中高低端市场授权处理器内核市场。这让人想起ARM三个系列的Cortex产品在几年前的发布。

2012-05-15 17:04:31 2876

2876 Imagination Technologies,领先的多媒体硅半导体知识产权技术公司日前宣布推出其开创业界先河的PowerVR 6系列图形处理器(GPU)内核系列中最新的知识产权(IP)内核产品。

2012-06-19 14:05:38 2766

2766

日前,Synopsys宣布发布为最优化实现所有系统级芯片处理器内核的标准单元库和存储器套件。新的DesignWare HPC设计套件为CPU、GPU和DSP的内核带来了卓越的性能、功耗和面积。

2013-06-25 11:14:17 1869

1869 的新IP内核包括超高性能和超低延时100G Interlaken、100G以太网、40G以太网和10G以太网IP。内核经过优化,实现了业界最佳性能、最低延时和最少资源占用。数据中心和网络设备开发人员可以

2013-11-20 17:04:25 2709

2709 泰克隆重推出TSG4100A系列RF矢量信号发生器。中档仪器的性能,入门级RF信号发生器的价格。市场上性价比最好的矢量信号发生器。

2015-03-09 10:57:24 4404

4404 具有语音功能的波形发生器,感兴趣的小伙伴们可以瞧一瞧。

2016-11-22 14:04:52 0

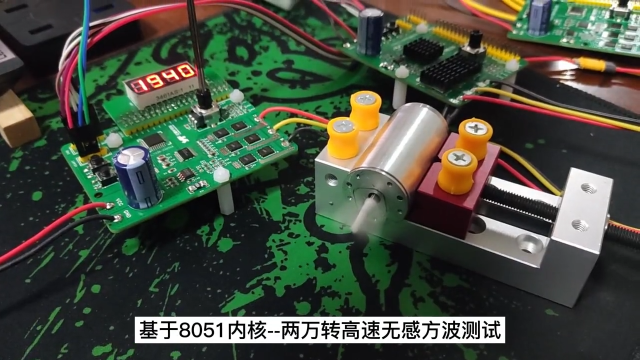

0 基于8051内核IP核的应用,感兴趣的小伙伴们可以瞧一瞧。

2016-11-11 18:18:32 1

1 原版 Arduino 技术内幕,详细介绍了Arduino开发的内核与程序优化方法,最大程度挖掘开发板的设计潜力

2017-05-02 10:55:35 6

6 。 使用Xilinx内核生成器IP函数实现FPGA VI中不同的Xilinx内核生成器IP。LabVIEW使用IP集成节点实现上述函数。函数名称和说明来自于Xilinx数据表。单击Xilinx内核生成器配置对话框的数据表按钮,了解IP内核的详细信息。 选板随终端变化且仅显示FPGA设备系列支持的IP。

2017-11-18 05:54:05 1780

1780 中国,北京-2016年7月26日-Silicon Labs(芯科科技有限公司,NASDAQ:SLAB)日前推出具有成本效益的原型车设计,可轻松连接无线传感器节点到移动设备和云端,从而有效帮助企业做出

2018-04-20 20:24:00 1446

1446 本文主要介绍了什么是直流高压发生器以及直流高压发生器的作用。直流高压发生器简称直高发,又称高压发生器、中频直流高压发生器、高压直流发生器、直流发生器、便携式直流高压发生器、高频直流高压发生器、交直流高压发生器。

2018-01-30 17:28:27 6307

6307

Robert Ioffe描述了一系列一致的优化,可以提高英特尔®上的OpenCL内核性能Iris™图形或英特尔®Iris™Pro图形,使用英特尔®SDKfor OpenCL™应用程序2013。

2018-11-07 06:17:00 4038

4038 即将推出的Xilinx ST 2059 IP内核的早期技术演示展示了将时序和同步功能集成到ST 2022网络中,并将针对KC705Kintex®-7评估平台。

2018-11-28 06:19:00 3671

3671 在内核调试中,会经常出现内核僵死的问题,也就是发生死循环,内核不能产生调度。导致内核失去响应。这种情况下我们可以采用修改系统内核中的系统时钟的中断来定位发生僵死的进程和函数名称。

2019-05-10 10:37:00 791

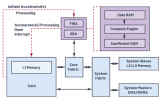

791 寄存器以启动加速器处理。一旦所有通道的配置完成,就会向内核发送一个中断,以便内核将处理后的输出用于后续操作。

2020-07-06 16:10:04 3700

3700

随着RT-Thread Smart微内核发布会的临近,对于开源社区以及国产RTOS比较关注的人或许早有耳闻。

2020-09-01 10:23:43 2556

2556

内核重置应该保持断言状态,直到相关时钟稳定为止。在从重置中取出以太网 IP 核之前,它必须具有稳定的频率而且没有故障。

2020-12-24 16:20:53 2806

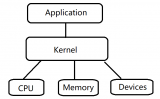

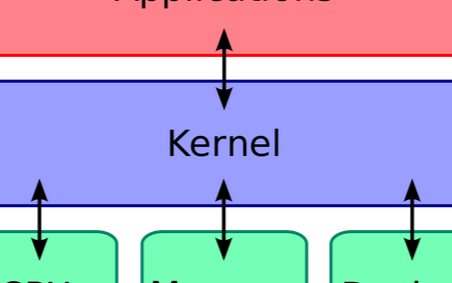

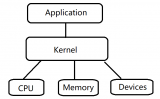

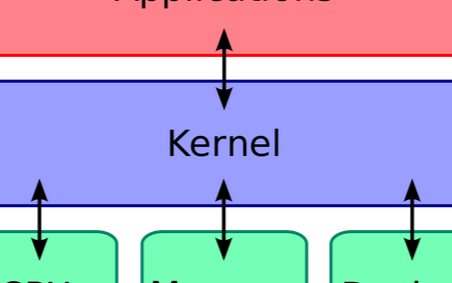

2806 内核是世界上最大的开源项目之一,但是内核是什么,它用于什么? 02 什么是内核 内核是与计算机硬件接口的易替换软件的最低级别。它负责将所有以用户模式运行的应用程序连接到物理硬件,并允许称为服务器的进程使用进程间通信(IPC)彼此获取信息。 03 内核还要分种类? 是的,

2020-10-21 12:02:53 4905

4905

内核(Kernel)是Linux生态的基石,其开源且免费。去年12月13日,Linux 5.10内核发布上线。这是长期支持版本,向下兼容老内核,且带来了大量修复完善。

2021-01-05 09:48:35 2440

2440 混合内核实质上也是微内核,而外内核是一种比较极端的设计方法,目前还处于研究阶段,所以我们就着重讨论宏内核与微内核两种内核。

2021-03-17 16:05:48 11

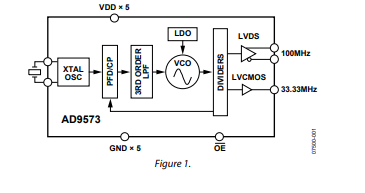

11 AD9573:PCI-Express时钟发生器IC,PLL内核,分频器,双输出数据表

2021-05-08 20:05:05 5

5 ACIS内核和parasolid内核的来龙去脉与比较(深圳市普德新星电源技术有限公司)-ACIS内核和parasolid内核的来龙去脉与比较

2021-08-31 16:52:18 11

11 目录一、51内核二 、ARM内核一、51内核51单片机由一个IP核和片上外设组成,IP核就是上图中的CPU,片上外设就是上图中的:时钟电路、SFR和RAM、ROM、定时/计数器、并行I/O口、串行I

2021-11-15 10:06:02 11

11 信号发生器基础知识Signal Generator BasicsⅠ.优化信号发生器的九大技巧Ⅱ.利用信号发生器了解和测试多通道射频系统Ⅲ.使用新一代信号发生器提高幅度精度优化信号发生器的九大技巧1在

2022-03-23 14:04:46 2385

2385 Xilinx快速傅立叶变换(FFT IP)内核实现了Cooley-Tukey FFT算法,这是一种计算有效的方法,用于计算离散傅立叶变换(DFT)。

2022-03-30 11:01:31 4200

4200 以Xilinx Vivado设计套件中提供的FFT IP为例,简要说明如何进行FFT IP配置和设计。

2022-07-22 10:21:27 3424

3424 MCU出现的历史并不长,但其发展非常迅速。就目前来说,第三方的MCU内核中,占主导地位的是Arm Cortex M系列,该系列由Arm开发,采取IP授权的形式,Cortex-M系列具有短流水线、超低

2022-07-29 11:23:34 1585

1585 脉冲发生器: 顾名思义,脉冲发生器是一种产生脉冲的信号发生器。这些信号发生器通常采用逻辑脉冲发生器的形式,可以产生具有可变延迟的脉冲,有些甚至提供可变上升和下降时间。

2022-08-02 15:48:42 5862

5862 超低抖动时钟发生器如何优化串行链路系统性能

2022-11-04 09:50:15 0

0 处理器内核越复杂,面积和功耗就越大。但是,随着处理器处理数据的方式变得更加复杂,复杂性并不是一个单一的衡量维度。在选择处理器IP内核时,为您的项目选择正确的复杂性很重要。

2023-01-10 10:30:35 1025

1025 STM32F407包含Cortex-M4内核,共有14路TIM资源,其中TIM2和TIM5具有32位计数功能,其他为16位计数功能。本文将以TIM2实现发动机转速/相位发生器的设计,并通过串口屏幕

2023-01-15 16:06:52 3520

3520 RX内核的特性 RX内核发展路线 增加附加值和系统复杂性的需求要求单片机具有更高的性能。同时,还要满足节能和延长电池寿命的需求,因此功耗也要降低。RX内核不断改进来满足这些需求。 RX产品家族特性

2023-02-17 13:45:02 2816

2816 元件组成,如计时器、振荡器和触发器等。使用脉冲发生器可以产生一定频率的脉冲信号,具有重复性,在某些特定情况下可以产生单一脉冲,一些特殊的脉冲发生器还可以产生有特定宽度和延迟的脉冲。 使用脉冲发生器需要遵循一定

2023-08-24 15:18:09 5688

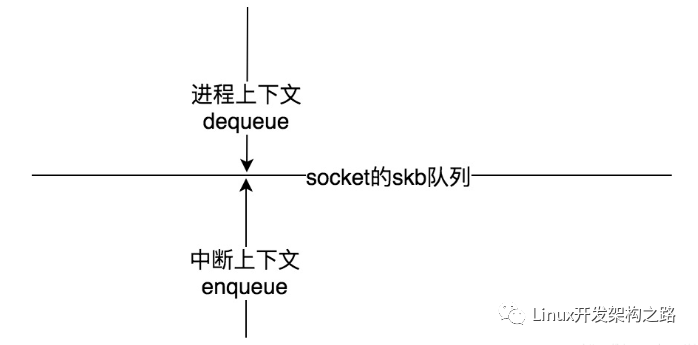

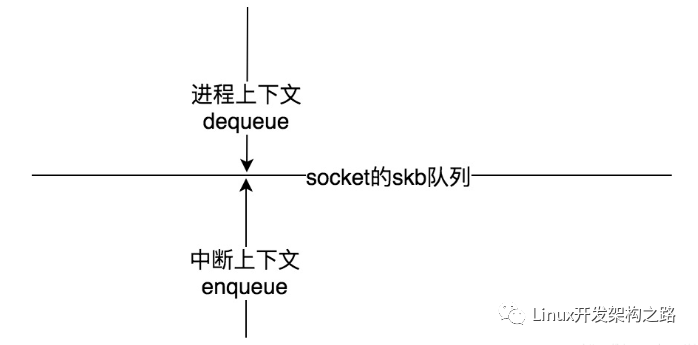

5688 真的很低,这是为什么?有没有办法去尝试着优化?而不是动不动就DPDK。 我们从最开始说起。 Linux内核作为一个通用操作系统内核,脱胎于UNIX那一套现代操作系统理论。 但一开始不知道怎么回事将网络协议栈的实现塞进了内核态,从此它就一直在内核态了。既然

2023-11-10 10:51:55 1085

1085

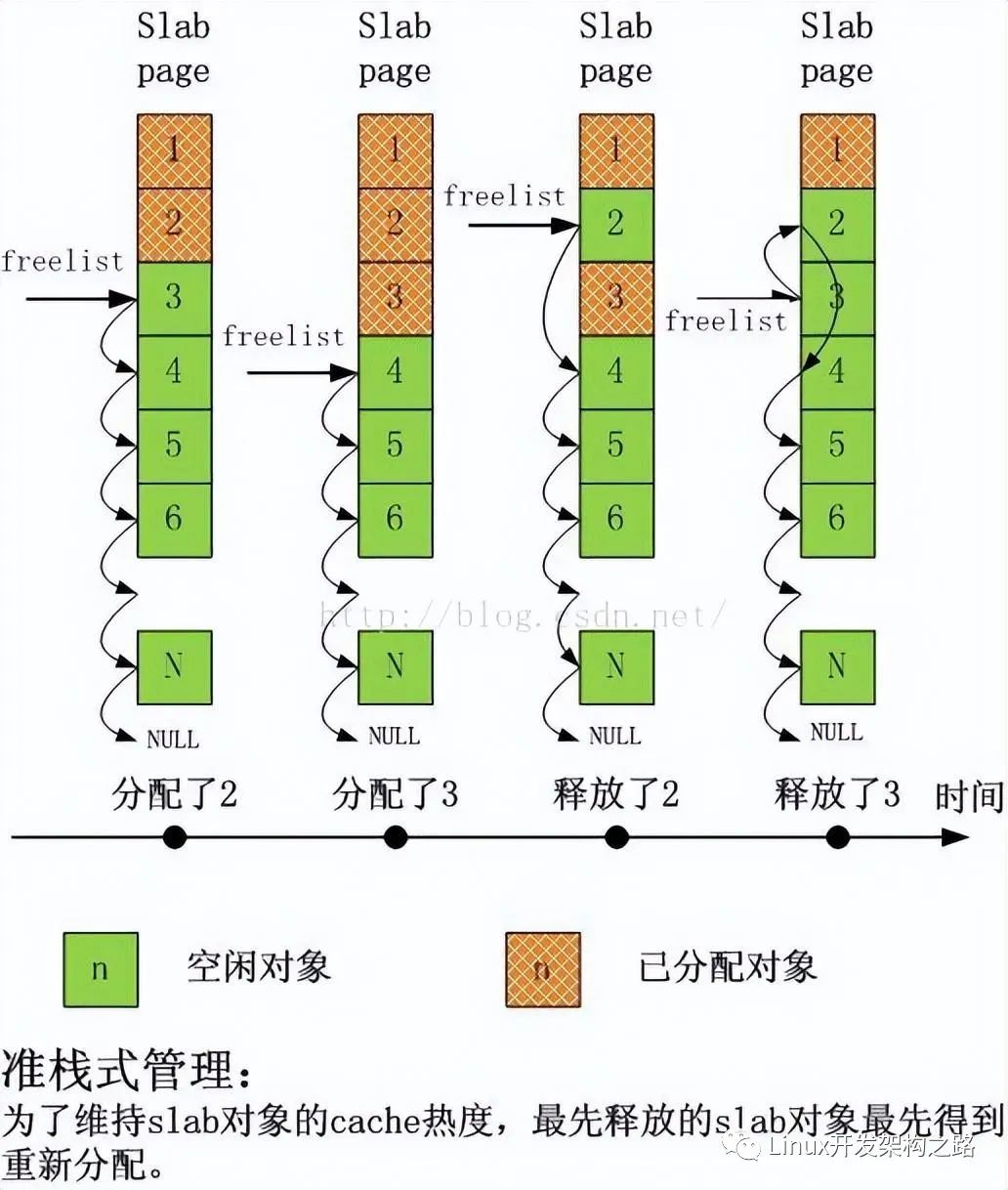

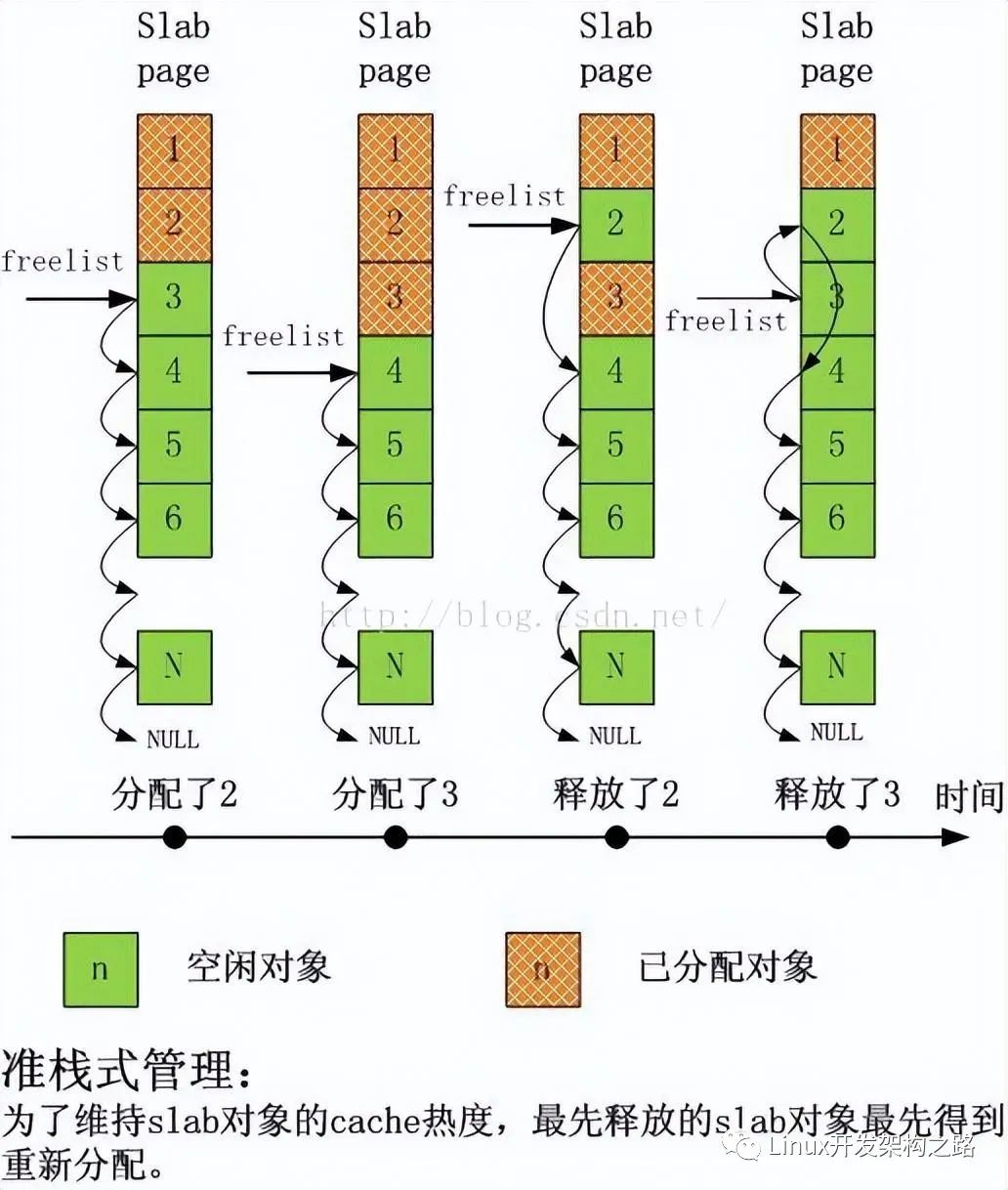

今天分享一篇内存性能优化的文章,文章用了大量精美的图深入浅出地分析了Linux内核slab性能优化的核心思想,slab是Linux内核小对象内存分配最重要的算法,文章分析了内存分配的各种性能问题(在

2023-11-13 11:45:42 1508

1508

电子发烧友网站提供《MCU市场分析:IP内核与产品情况.pdf》资料免费下载

2023-12-12 17:36:02 18

18 的原理、使用方法以及是否具有自动保护功能。 一、直流高压发生器的原理 直流高压发生器的基本原理是将实验电源输出的低压交流电通过整流和倍压电路来产生高压直流输出。具体来说,其原理可分为以下几个步骤: 1. 输入电源:直流高

2023-12-20 15:01:33 3362

3362 脉冲信号,并提供相应的步骤和示例。 1. 确定信号发生器的特性和功能 在使用信号发生器之前,需要先了解信号发生器的特性和功能。常见的信号发生器可以产生多种波形,例如正弦波、方波、三角波等,并具有调节频率、幅度、相位

2023-12-21 15:03:35 4289

4289 在电子测试和测量领域,函数发生器、信号发生器和波形发生器都是重要的测试仪器,它们各自具有独特的功能和应用场景。本文将详细介绍这三种发生器的原理、功能以及它们之间的区别。

2024-05-15 14:49:42 3254

3254 信号发生器是一种电子设备,用于生成具有特定特性的电信号,如正弦波、方波、锯齿波等。信号发生器广泛应用于测试和测量领域,如电子电路设计、通信系统、医疗设备等。本文将详细介绍信号发生器的使用方法、幅值

2024-06-03 10:56:17 6188

6188 电子发烧友网站提供《TI Arm内核三角函数的优化.pdf》资料免费下载

2024-09-11 09:19:18 1

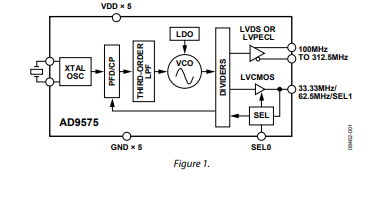

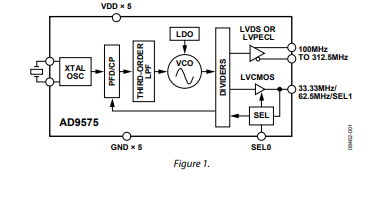

1 AD9575是一款高度集成的双路输出时钟发生器,包括一个针对网络定时而优化的片内PLL内核。整数N分频PLL设计基于ADI公司成熟的高性能、低抖动频率合成器系列,可实现线路卡的较高性能。对相位噪声和抖动要求苛刻的其它应用也能受益于该器件。

2025-04-10 17:00:26 958

958

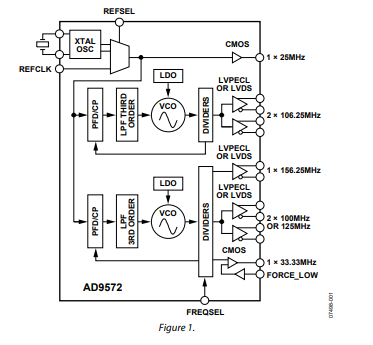

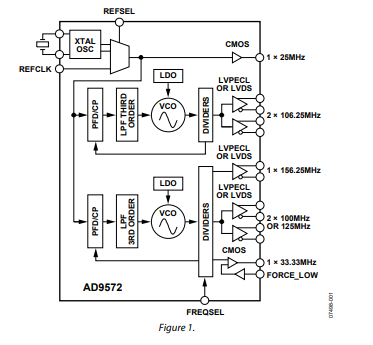

AD9572是一款多输出时钟发生器,具有两个片内PLL内核,针对包括以太网接口的光纤通道线路卡应用进行了优化。整数N分频PLL设计基于ADI公司成熟的高性能、低抖动频率合成器系列,可实现网络的较高性能。这款器件也适合相位噪声和抖动要求严格的其它应用。

2025-04-10 17:38:25 810

810

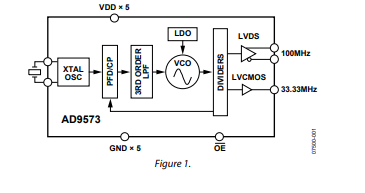

AD9573是一款高度集成的双路输出时钟发生器 , 包括一个针对PCI-e应用而优化的片内PLL内核 。 整数N分频PLL设计基于ADI公司成熟的高性能、低抖动频率合成器系列 , 可实现线路卡的较高性能 。 这款器件也适合相位噪声和抖动要求严格的其它应用。

2025-04-11 09:51:35 812

812

电子发烧友App

电子发烧友App

评论