即将推出的Xilinx ST 2059 IP内核的早期技术演示展示了将时序和同步功能集成到ST 2022网络中,并将针对KC705Kintex®-7评估平台。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

内核

+关注

关注

4文章

1436浏览量

42491 -

赛灵思

+关注

关注

33文章

1797浏览量

133148 -

同步

+关注

关注

0文章

105浏览量

19966

发布评论请先 登录

相关推荐

热点推荐

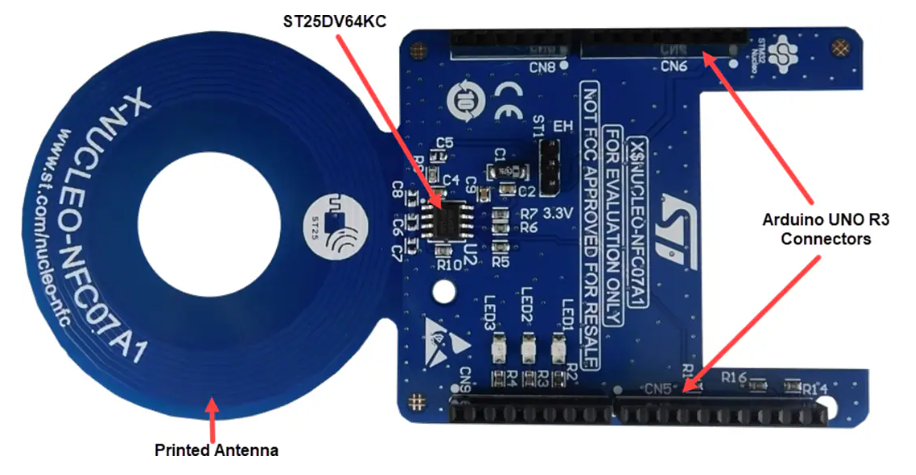

ST25DV64KC动态NFC/RFID标签技术解析与应用指南

STMicroelectronics X-NUCLEO-NFC07A1 NFC/RFID标签扩展板是一款用于ST25DV64KC动态NFC/RFID标签的演示和开发平台。ST25DV64K是一种

如何使用AMD Vitis HLS创建HLS IP

本文逐步演示了如何使用 AMD Vitis HLS 来创建一个 HLS IP,通过 AXI4 接口从存储器读取数据、执行简单的数学运算,然后将数据写回存储器。接着会在 AMD Vivado Design Suite 设计中使用此 HLS

Xilinx Shift RAM IP概述和主要功能

Xilinx Shift RAM IP 是 AMD Xilinx 提供的一个 LogiCORE IP 核,用于在 FPGA 中实现高效的移位寄存器(Shift Register)。该

飒特红外如何用硬核技术重构救援效率

,必须能在人类视觉失效的「盲区」里,让生命信号清晰显现。今天,就以搜救场景为核心,聊聊飒特红外如何用硬核技术重构救援效率。

住宅IP动态化技术应用解析:对比数据中心IP的三大核心优势

在网络安全、数据采集、跨境电商等数字技术领域,IP资源的选择直接影响业务运行效果。本文针对技术开发者与行业用户关注的动态住宅IP特性,对比传统数据中心

详解Xilinx的10G PCS PMA IP

如果要在Xilinx的FPGA上使用万兆以太网通信,大致有三种方法构建协议栈。第一种使用GTX等Serdes作为底层的PHY,上层通过HDL实现构建MAC和IP层,这种方式难度会比较大,底层需要完成PHY层的设计,最终我想通过这种方式实现万兆以太网的搭建。

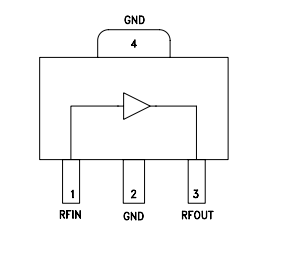

HMC789ST89E InGaP HBT有源偏置MMIC放大器技术手册

工作,其输出IP3可以优化为+45 dBm。 高输出IP3和高增益使HMC789ST89E非常适合蜂窝/4G和固定无线环境下的PA驱动器和前置驱动器应用。

为什么无法使用多个互联网协议 (IP) 摄像头作为多通道人脸检测的输入C++演示?

用于两个 IP 摄像头的命令作为 多通道人脸检测的输入C++演示:-i rtsp://admin:gamma@172.18.70.113:8554/CH001.sdp/ rtsp://admin

发表于 03-05 09:17

Vivado FIR IP核实现

Xilinx的FIR IP核属于收费IP,但是不需要像 Quartus那样通过修改license文件来破解。如果是个人学习,现在网络上流传的license破解文件在破解Vivado的同时也破解

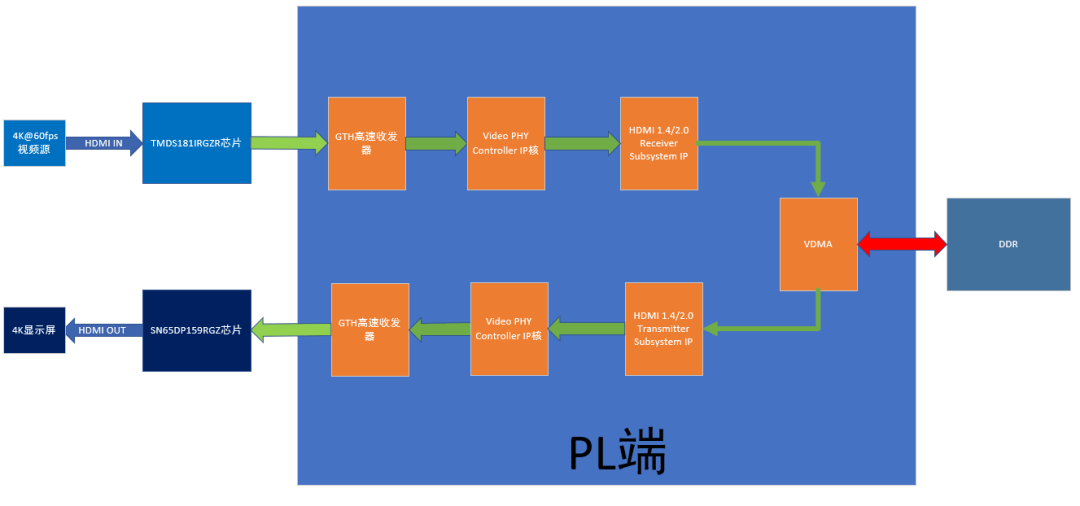

解锁4K,Xilinx MPSoC ARM + FPGA高清视频采集与显示方案!

当下,随着数字化多媒体技术以令人惊叹的速度不断演进,高清视频处理成为众多领域关注的焦点。今天为大家分享4K HDMI 高清视频方案,基于Xilinx UltraScale+ MPSoC

SMEC80ST加密芯片SDK开发包

SMEC80ST 芯片采用 32 位智能卡安全内核处理器,芯片系统时钟15MHz。具有 5KB SRAM、64K 程序存储区域,16K 数据存储区域。

发表于 12-30 14:30

•1次下载

Xilinx ST 2059 IP内核技术的演示

Xilinx ST 2059 IP内核技术的演示

评论