1、概述

智多晶EDA工具HqFpga(简称HQ),是自主研发的一款系统级的设计套件,集成了Hqui主界面、工程界面、以及内嵌的HqInsight调试工具、IP Creator IP生成工具、布局图、热力图、时序分析等。HQ支持Windows、Linux操作系统利用HQ设计套件,设计人员能够实现高效率的FPGA工程开发与调试验证。

HQ在2025年升级迭代新增很多功能,本文将依次介绍HQ整体套件在各个模块的主要重大进展。

2、增强易用性

2.1 AI助手-晶小助支持

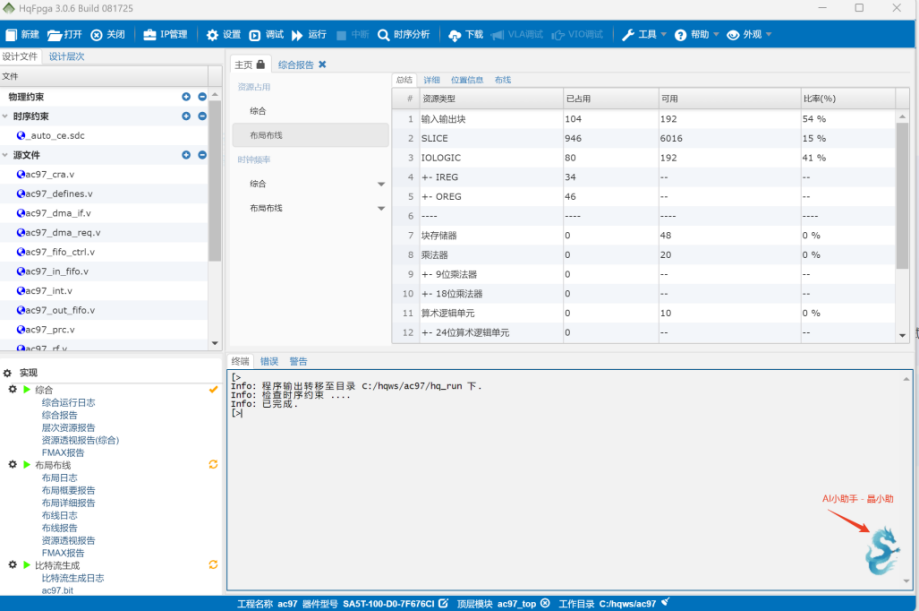

HQ2025接入DeepSeek 大模型,并推出 FPGA 设计专属 AI 助手——晶小助,如下图中的右下角。这是 FPGA 领域首次引入大模型 AI 助手,为 FPGA 工程师提供前所未有的智能交互体验,让开发更便捷、高效。

晶小助是基于 DeepSeek 大模型构建的智能助手,深度融合了智多晶多年积累的用户文档与技术知识。无论是用户手册查阅、工具使用、调试建议,还是约束配置与综合优化,晶小助都能为用户提供快速、准确的回答。

晶小助支持自然语言提问,内置智多晶知识库,答案专业可靠,一键唤起,随时随地解疑答惑,可以避免翻阅手册,节省查阅时间。

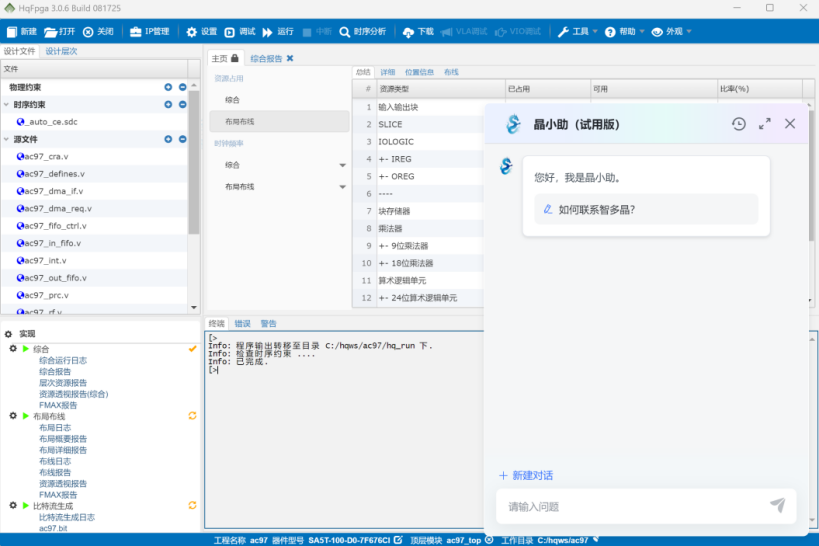

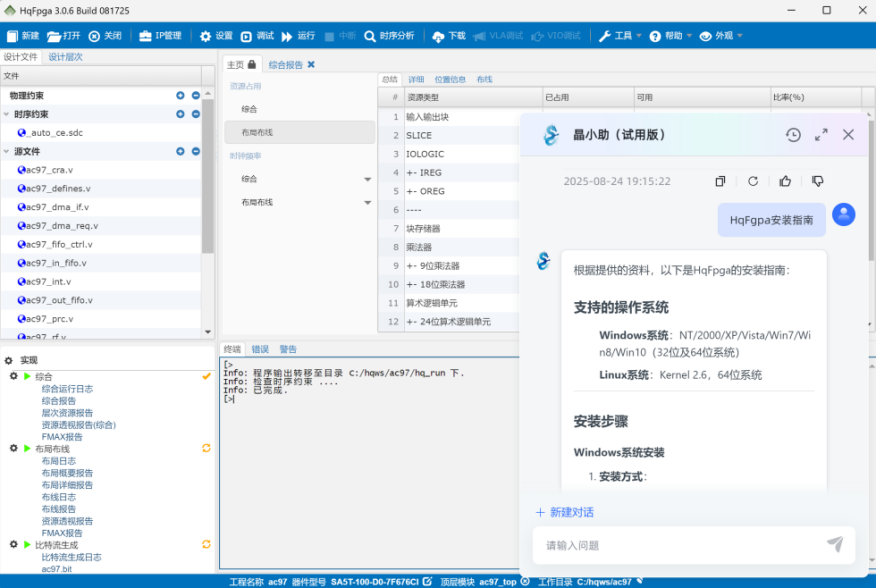

使用示例

点击晶小助图标,弹出下面左图的对话框,在编辑框输入问题。比如输入“HqFpga安装指南”,晶小助会给出如下面右图所示的安装说明。

2.2设计报告

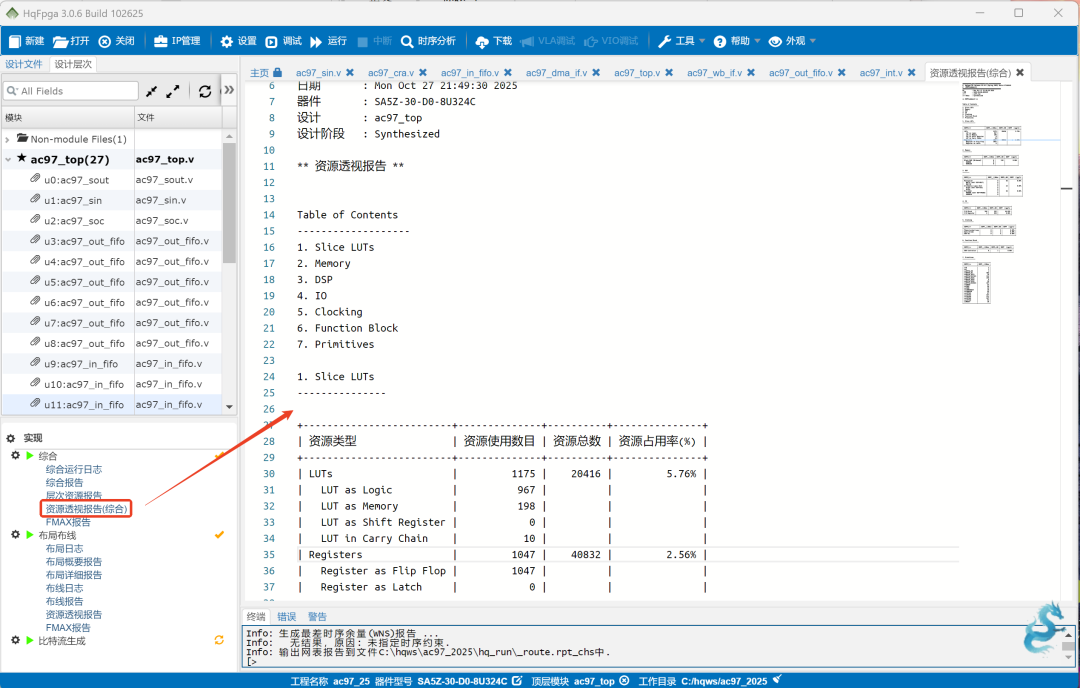

2.2.1资源透视报告

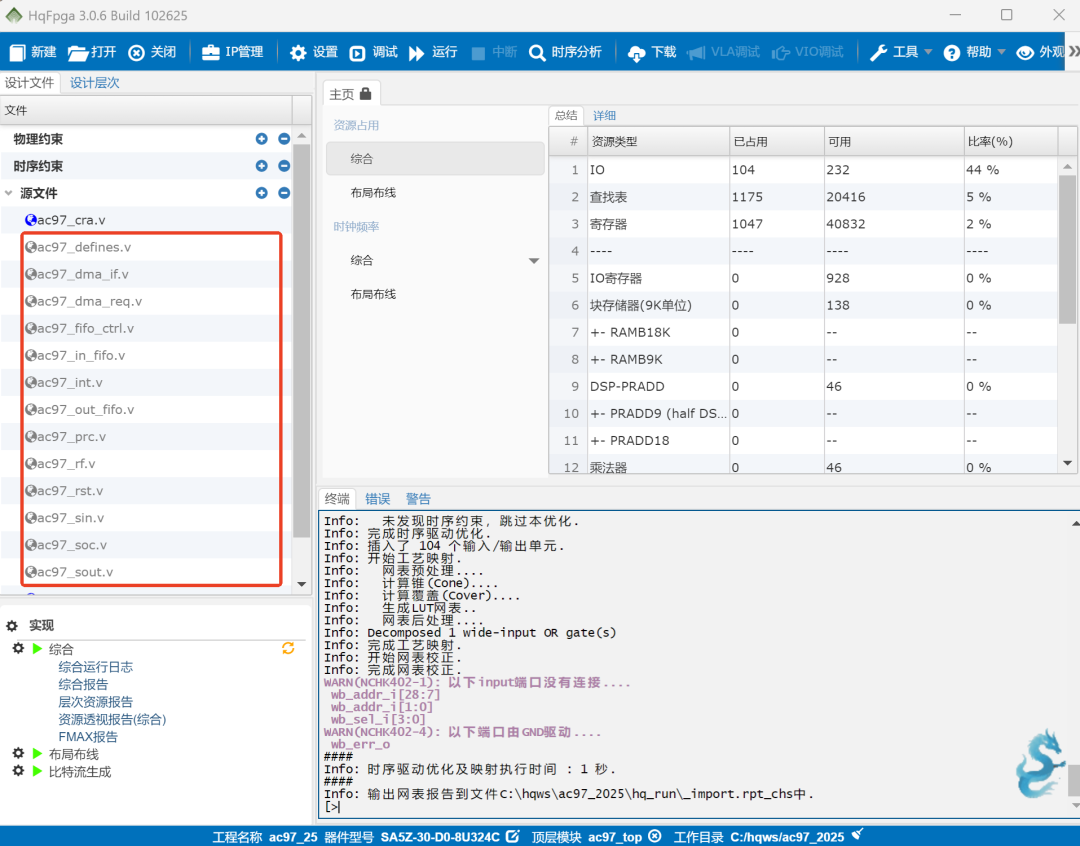

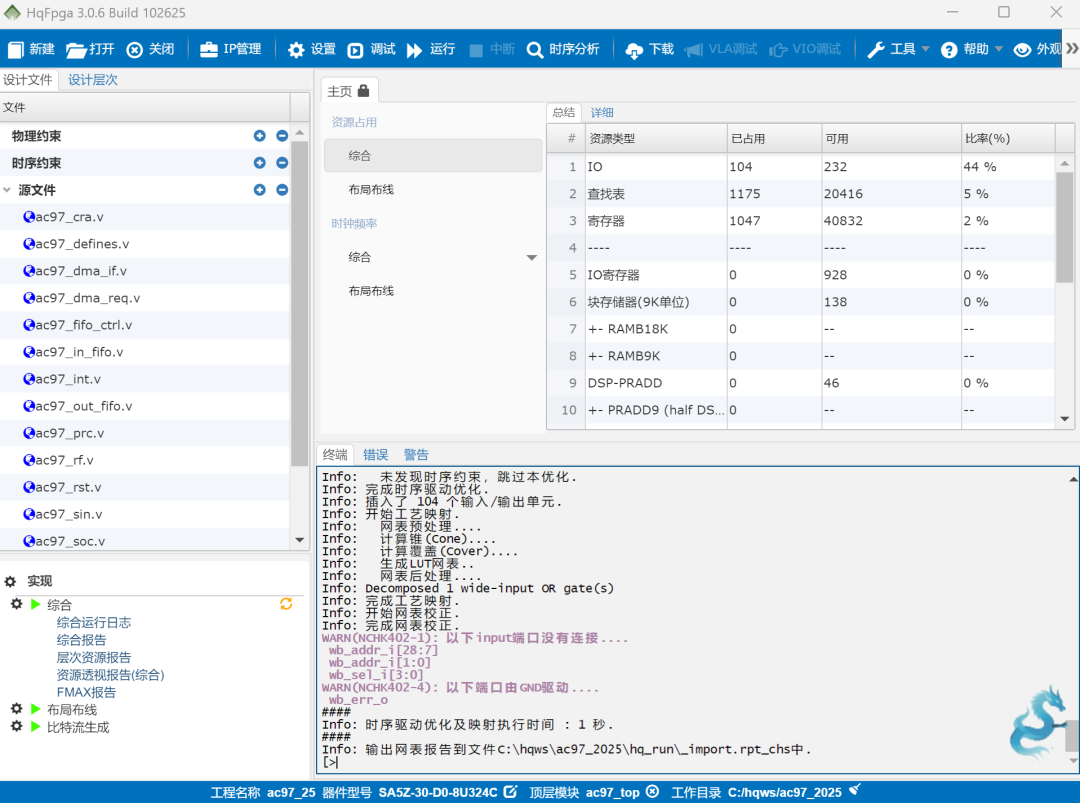

HQ2025新增资源透视报告,该报告功能旨在报告FPGA中被使用的可配置资源在应用中的底层配置结构信息,便于用户分析设计实现。比如FPGA上的Register既可以配置为Flip-Flop,也可以配置为Latch,如果在旧版本上,只有资源报告,是看不出具体Register实现的配置逻辑;在新版上,可以看到各种配置和各自的数量。如下图中,看到Register资源共使用1047个,其中配置为Flip-Flop共1047个,Latch为0个。

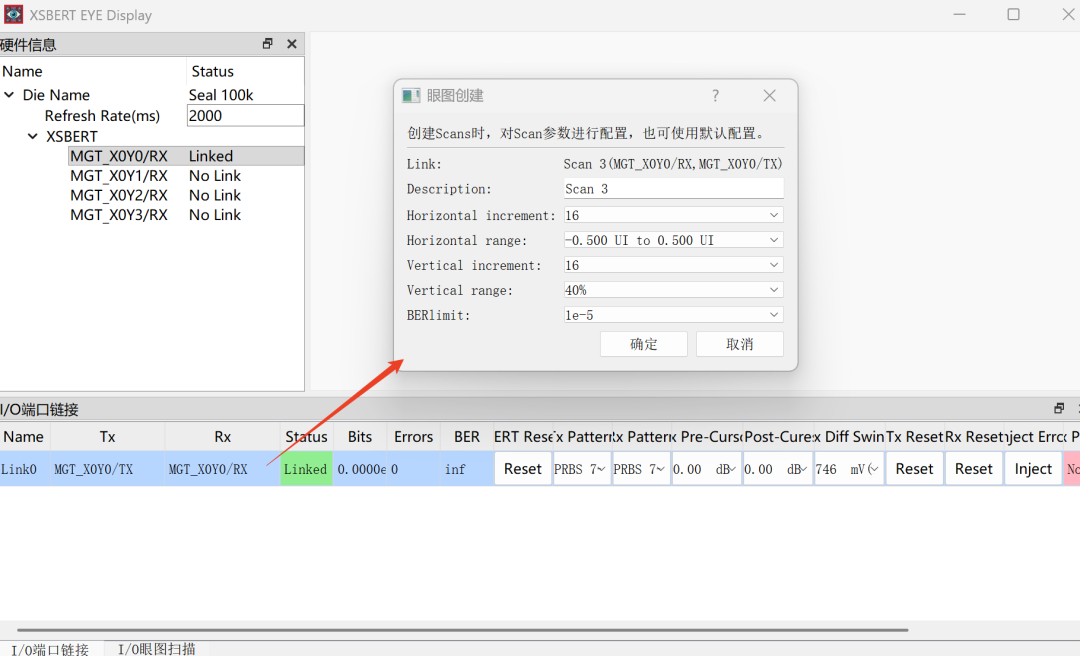

2.2.2层次资源报告分析器

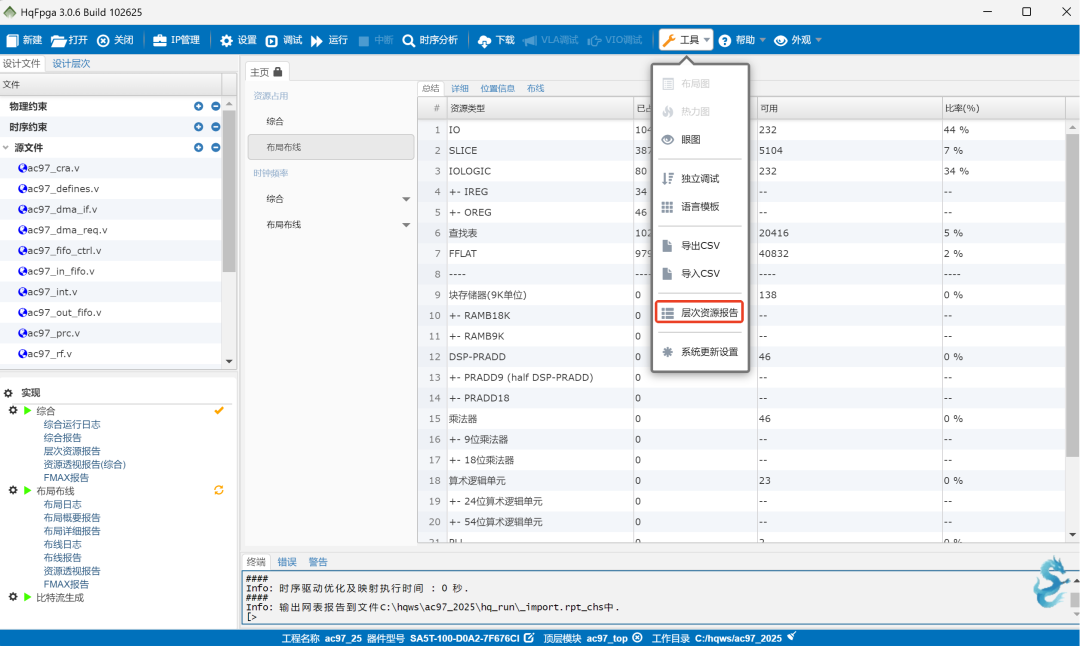

HQ2025新增层次资源报告分析器,内嵌到HQ套件主界面的【工具】-【层次资源报告】,如下图。

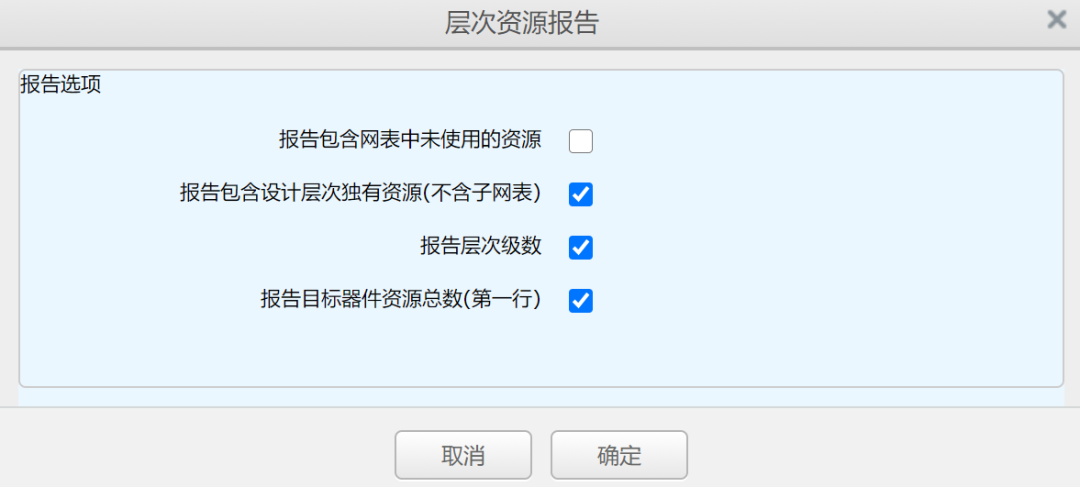

该功能可以按照用户的定制选项输出源设计综合结果中的层次资源统计信息。单击【层次资源报告】打开定制选项的对话框,如下图,可以定制选择:报告包含网表中未使用的资源、报告包含设计层次独有资源(不含子网表)、报告层次级数、报告目标器件资源总数(第一行),输出配置的层次资源信息。

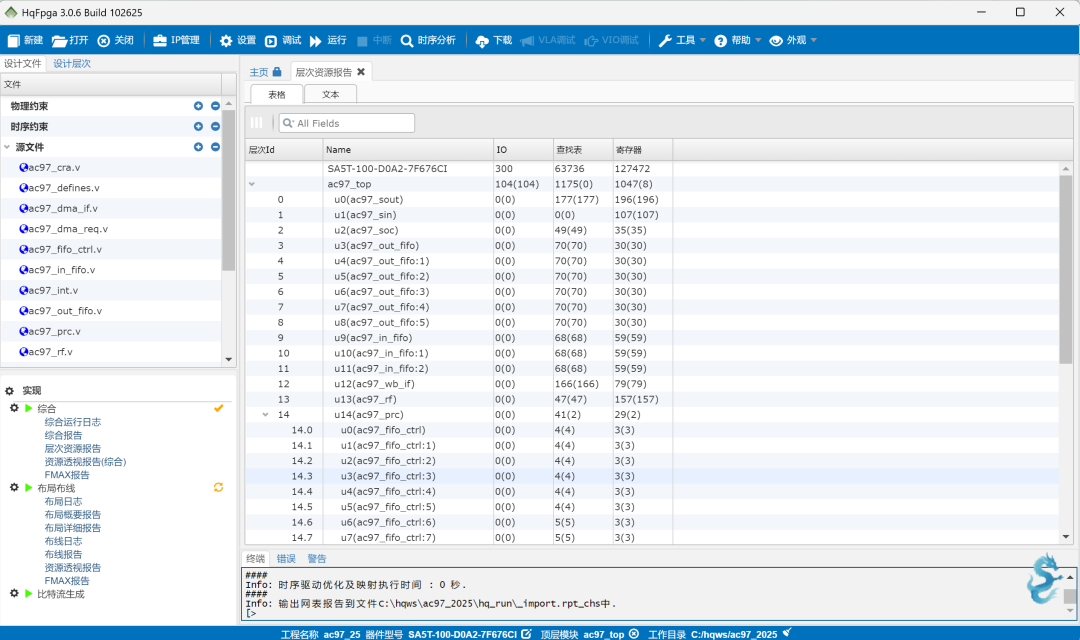

按照上图的配置,打开定制的层次资源报告,该报告信息有两种形式:表格、文本。具体如下图的图示。

2.3 IDE(集成设计管理)

2.3.1 源文件启用/禁用

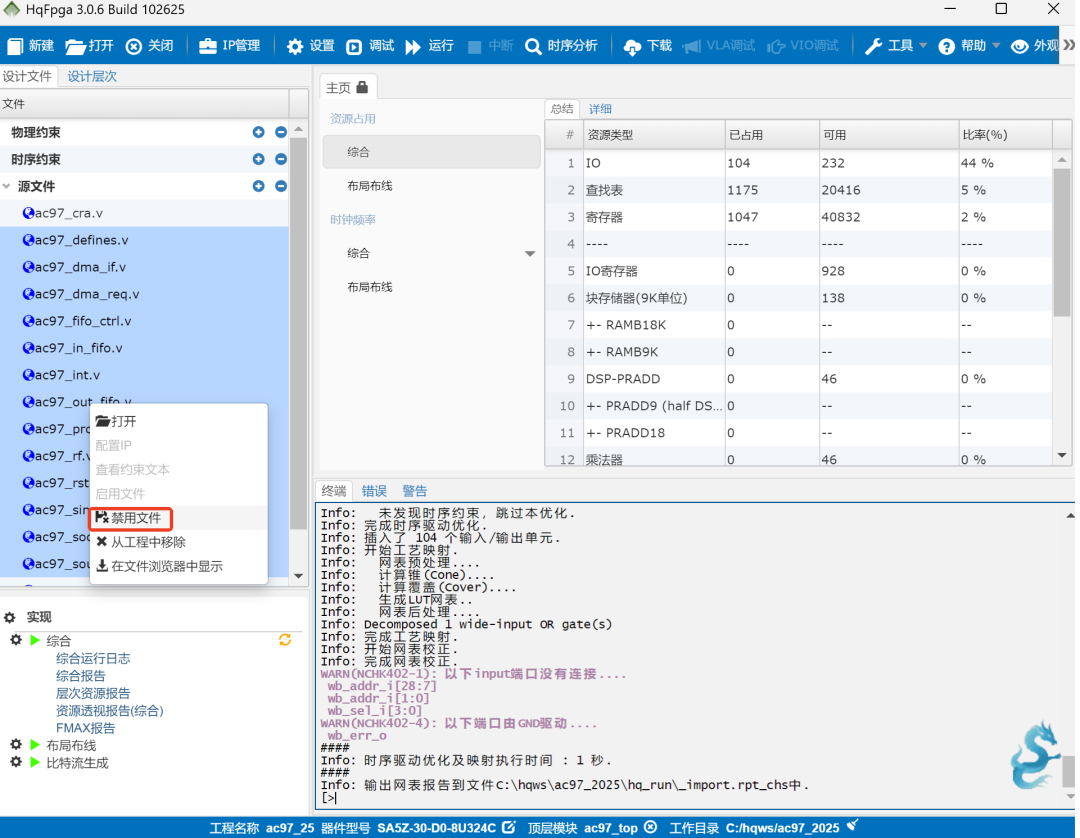

HQ2025新增源文件的启用/禁用功能,方便用户可以自由启用和禁用当前工程的设计,进行所需的编译和设计。该功能支持单文件,也支持多文件的启用和禁用。如下面的左图,选中【设计文件】区的多个文件,右键弹出菜单,选择【禁用文件】,被禁用的文件如下面的右图灰色显示,不参与工程的编译、运行和调试等。

如下面的左图,选中【设计文件】区的多个禁用文件,右键弹出菜单,选择【启用文件】,被禁用的文件再次恢复原来的正常被使用状态,如下面右图。

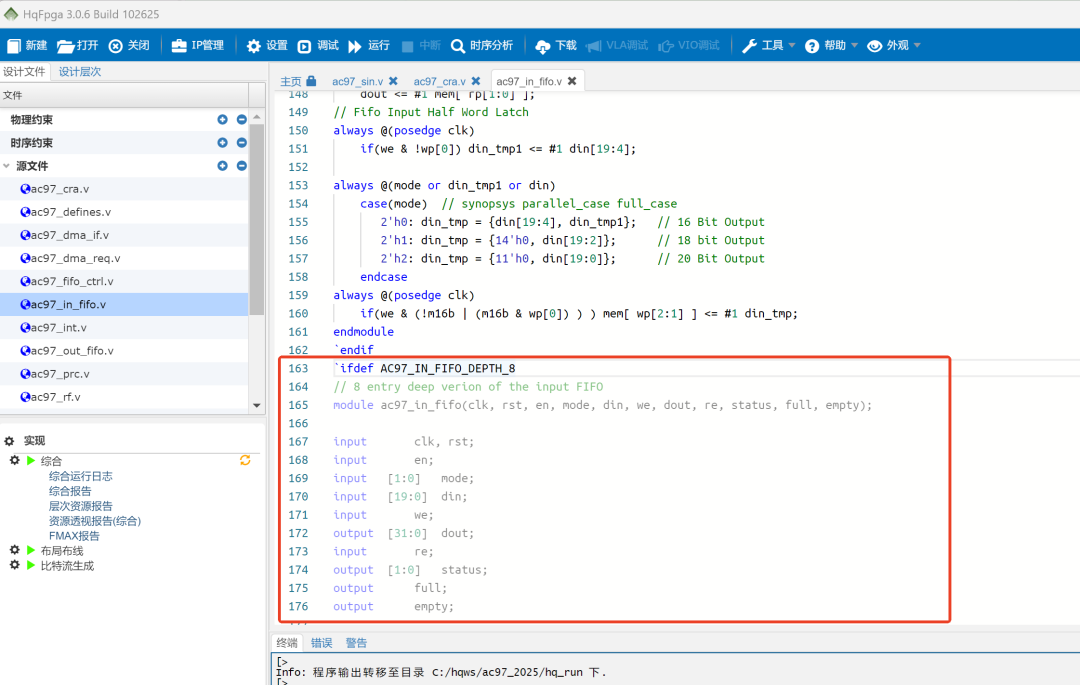

2.3.2编辑器ifdef差异化显示

HQ2025的编辑器新增ifdef差异化显示,对于条件为false的ifdef条件预编译语句部分实现灰色显示,即在当前设计中,灰色部分源码不起作用,如下图所示,AC97_IN_FIFO_DEPTH_8没有define声明,所以”`ifdef AC97_IN_FIFO_DEPTH_8”条件控制的部分是无效的,在编辑区的显示为灰色。

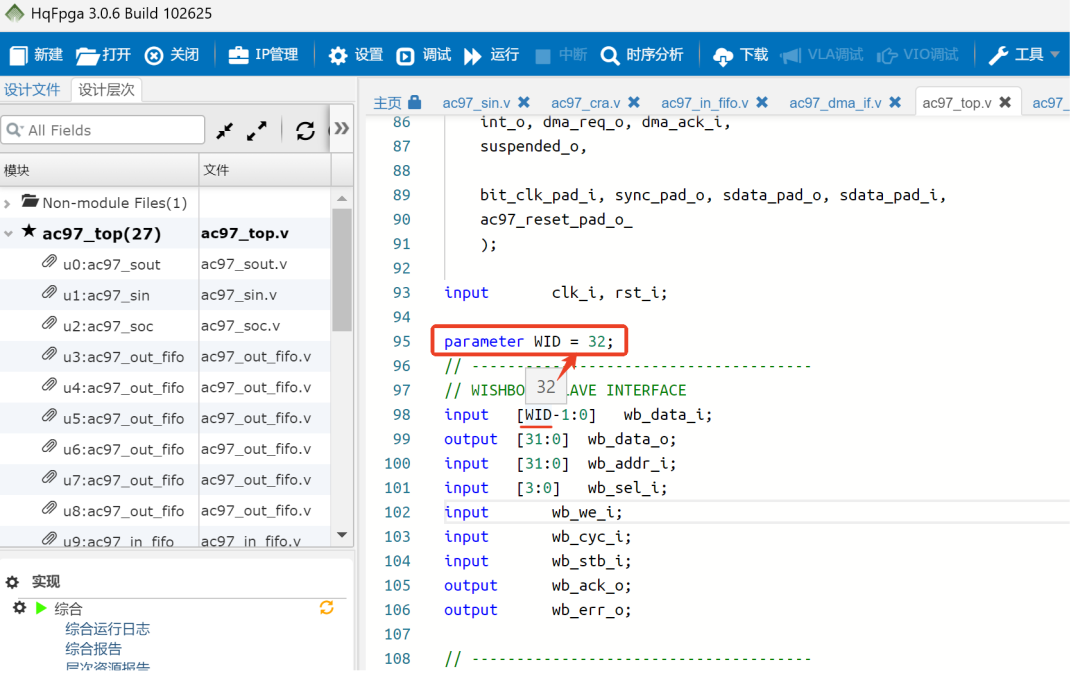

2.3.3编辑器参数值显示

HQ2025的编辑器新增参数值显示,对于宏参、parameter,鼠标放在参数名上,可以显示值。如下图示,定义了参数WID为32,当鼠标放在第98行的WID上,显示出32。

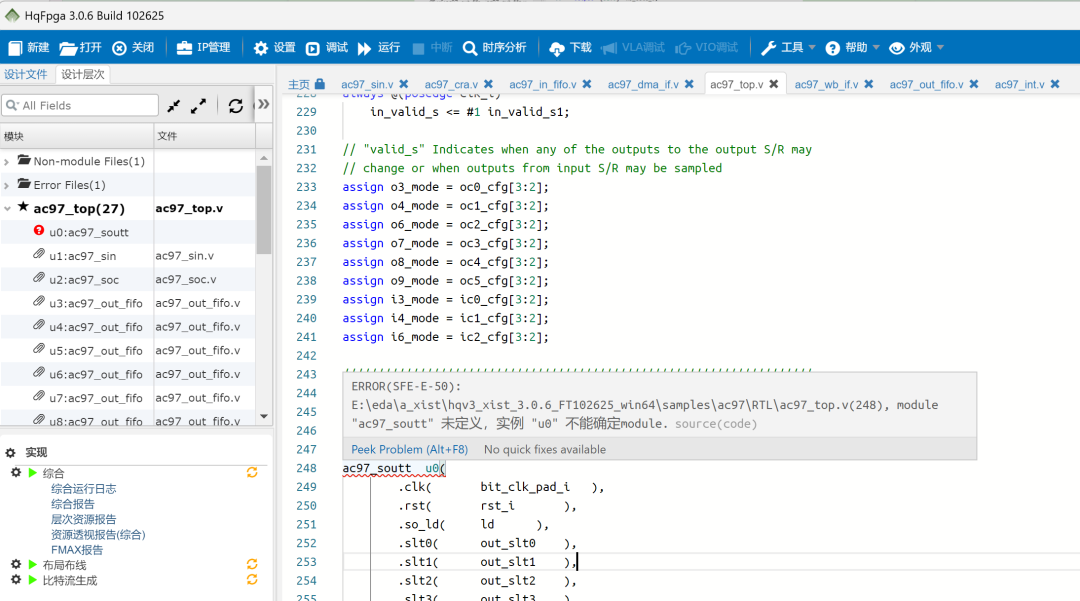

2.3.4 编辑器显示源码编译错误信息

HQ2025的编辑器新增源码编译错误的信息显示,如存在编译错误,错误语句会有红色波纹线提示,鼠标放在改语句上,会显示出错误信息,同时存在错误的文件会在设计层次中以“红色小问号”显示出来,如下图,ac97_soutt module没有定义,例化语句存在语法错误,对应的错误信息,直观的在错误语句上方显示出来。

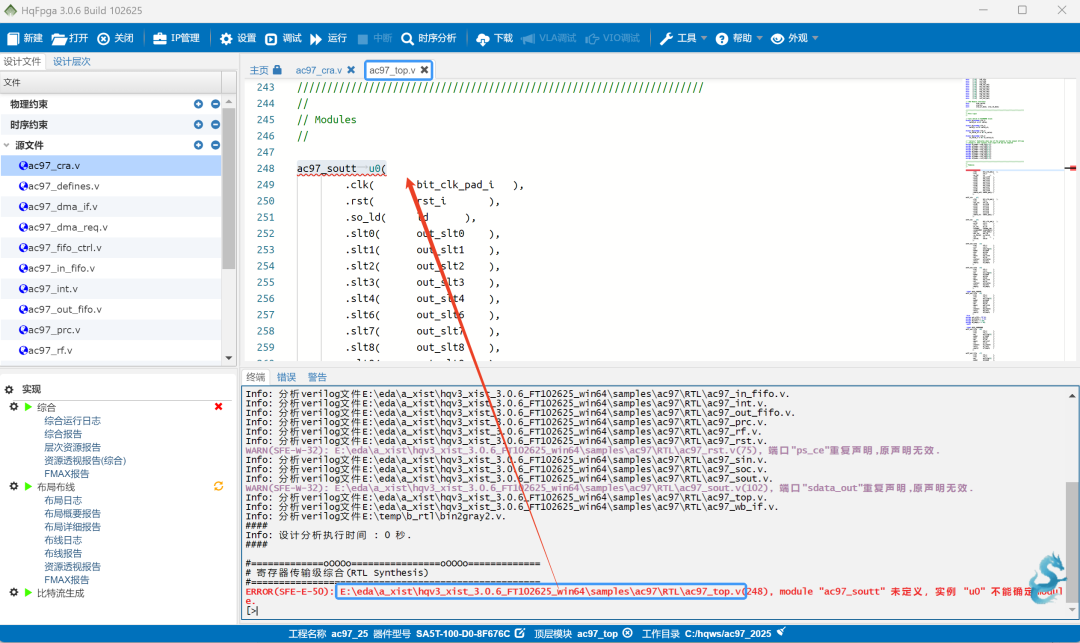

2.3.5 终端窗口输出信息中文件超链接

HQ2025升级了终端文件识别,即识别出输出信息中的文件并显示超链接。如下图中,终端窗口输出的ERROR信息中包含了文件路径信息:E:edaa_xisthqv3_xist_3.0.6_FT102625_win64samplesac97RTLac97_top.v(248),即文件的路径和错误位置,双击这个路径这一行,对应的错误文件ac97_top.v会在编辑区被打开,并且显示出错误的位置,如下图。

3、 眼图(XSBERT-EYE-CHART)

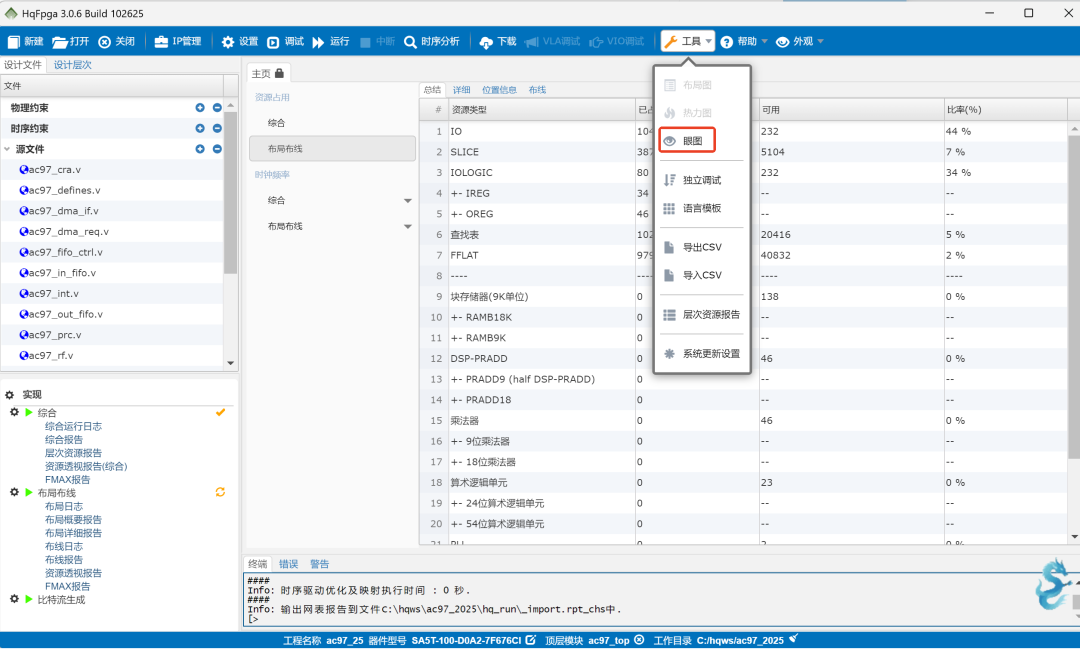

XSBERT(XiST Bit Error Ratio Test)是一种集成的测试工具,用于验证和测试FPGA中的高速串行接口,如SERDES(串行解串器)。它能够生成数据并进行误码率(BER)测试,提供链路性能的实时监控和诊断,帮助设计人员评估和优化串行接口的可靠性。通过使用XSBERT,用户可以检测信号质量问题、进行链路调试,并确保数据传输的稳定性,从而优化FPGA设计的整体性能。眼图已内嵌到HQ套件主界面的【工具】-【眼图】,如下图。

眼图分三个区

左上为芯片、链接信息界面,显示器件信息及链接状态,也可以设定链接状态刷新时间。

下部为 I/O Links 与 I/O Scans 两个页面,用于显示状态和调整参数。

右上为眼图显示及信息总结界面。可以使用鼠标左键拖动颜色条(Color Bar),调节显示效果。

使用示例

在 XSBERT bin/bit 文件下载完成后,点击上图中的【眼图】,打开眼图;点击区1、2,选择所需的 Tx 和 Rx创建链接,可以添加多组链接;点击区2的I/O Links 窗口中,想要观察眼图的链接的【Name】栏,右键创建扫描,选择所需扫描配置,点击【ok】生成眼图,如下图左图。眼图生成后的效果如下图图右。

4 、调试器

4.1 支持调试器多LA

HQ2025调试器支持更多LA(Logic Analyzer,逻辑分析仪), 每个LA相当于一台逻辑分析仪,最大支持16台。

相较于之前单LA,只能选择观察一组信号。如果故障是由模块间的复杂交互引起的,单次捕获很难捕捉到全貌。多LA则允许开发者同时、独立地捕获和触发多组不相关或弱相关的信号序列,从而高效地解耦和定位复杂系统中分散的、有依赖关系的故障。特别适用于复杂SoC、多核系统、高速互联以及任何包含多个异步或并发进程的设计,是提高调试效率和解决复杂问题的强大武器。具体特性对比如下表。

可以在下图的界面上点击红框加号增加。

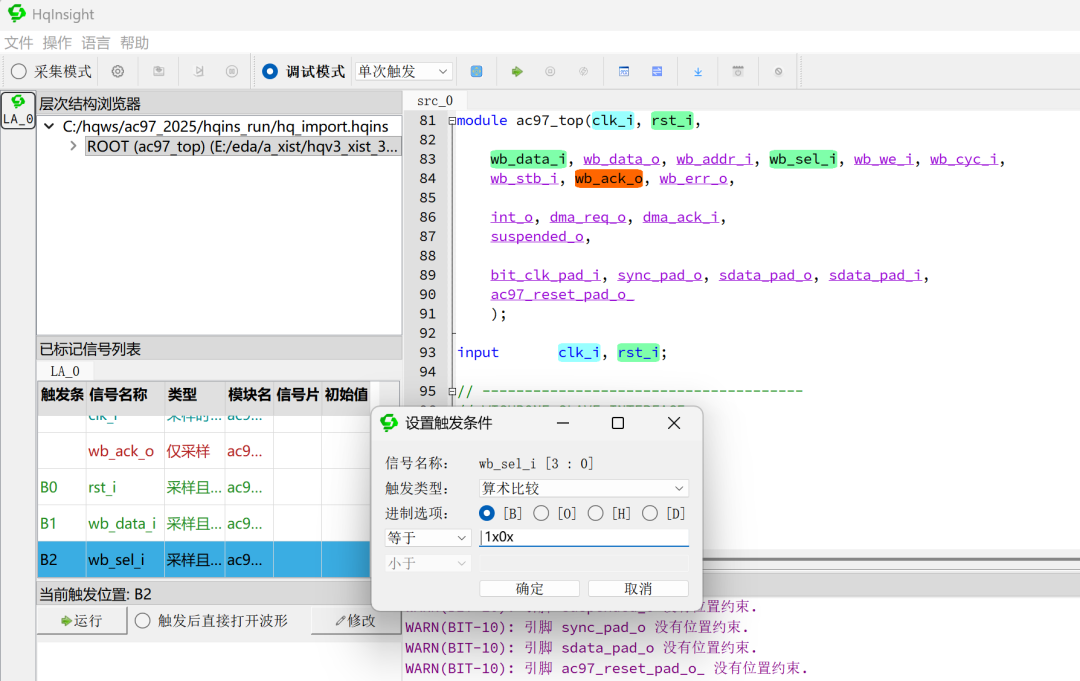

4.2 调试器触发方式支持X值

HQ2025调试器新增触发方式的X值,X值是don’t care(任意状态),如a=4'bxx11,不关心高两位([3:2],可以是00/01/10/11),只要低两位[1:0]是11就触发,该功能的主要用途用于解决未初始化寄存器、多驱动冲突、接口协议违规等深层设计问题。使用方式如下图。

4.3其它

改进EDIF网表调试支持,例如采用VLA IP调试。

支持高速下载器。

提升易用性及稳定性,例如支持信号设置保存、启用与禁用等。

5、 IP Creator

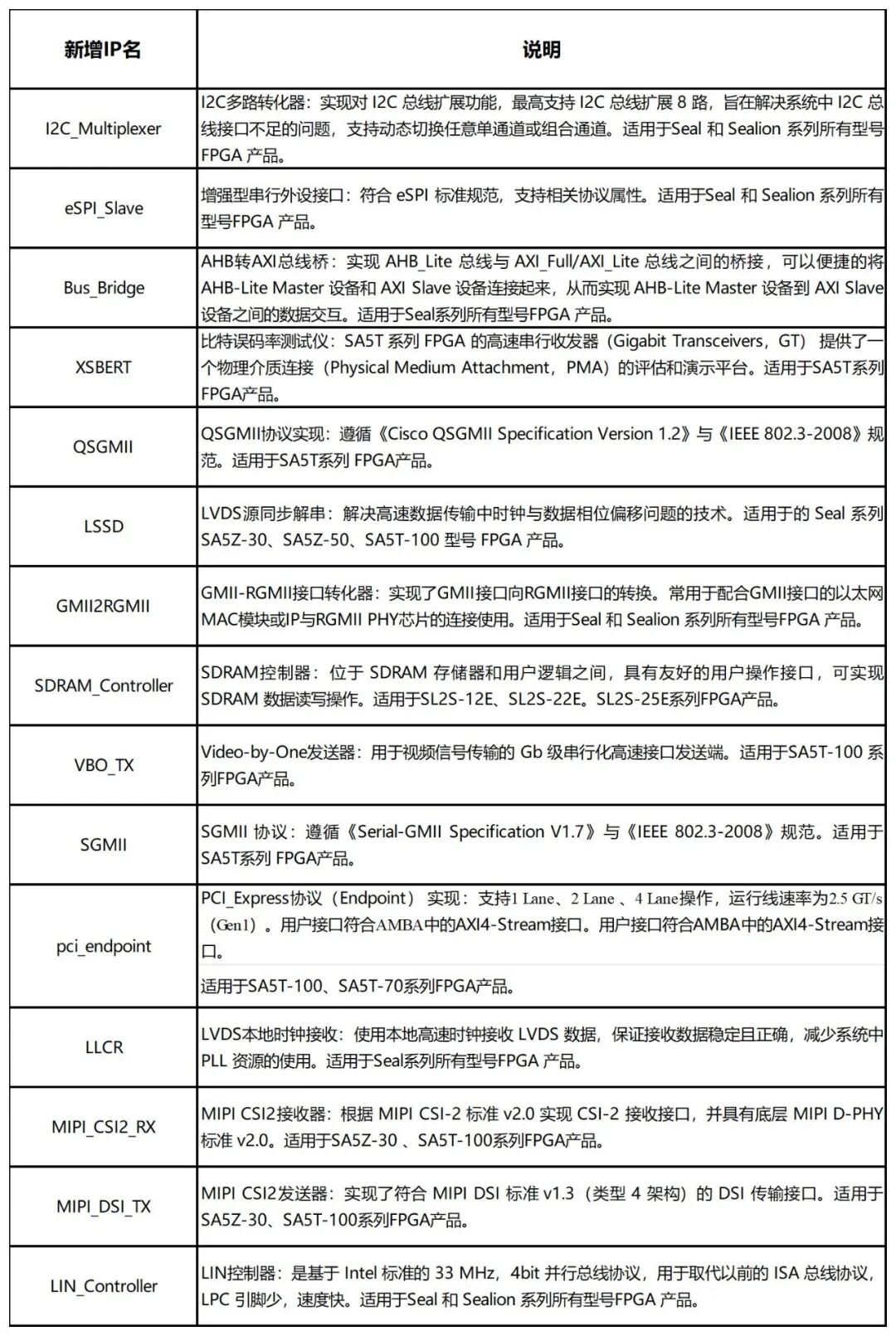

5.1丰富了IP品类

HQ2025的IP Creator新增较多品类的IP,方便项目高效开发。

* 具体详情请见每个IP配置界面打开用户手册。

此外,对多个IP做了升级,如FIR_Filter,SerDes、DDRC, PLL,EBR、FIFO_Generator等。

5.2 改进IP Creator平台的易用性和稳定性

例如增强异常处理。

HDL型IP生成flow可配置。

基于器件的配置。

增加浮点数range显示等。

6 、软件优化

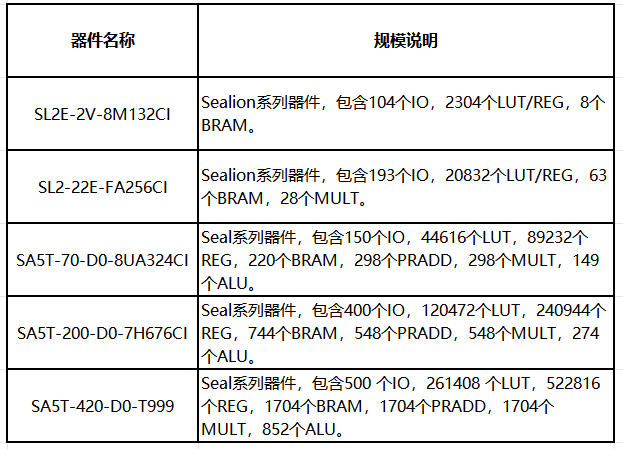

HQ2025软件(综合~布局布线~下载)支持了更多的器件,如SA5T-70/SA5T-200/SA5T-420等,并做了多方面优化,功能、性能、鲁棒性都得到了提升。

6.1新增器件的支持

HQ2025新增了多款器件的支持,如下表:

6.2综合

FSM优化:改进识别支持更多描述方式的FSM、支持更多编码方式等。

改进移位寄存器识别与映射,支持动态移位。

RAM/ROM推断与映射改进:完整支持了memory OUTREG结构、地址寄存器结构、包含RESET控制的结构;支持了有选择器链的BE-RAM;改进了可变字节宽度的BE-RAM支持。

支持跨层次资源合并,减少资源的消耗。

增强原语例化优化(例如不同IP网表中相同进位链合并)。

增强LUT合并功能。

总体资源占用率降低~5%,运行时间减少约10%。

6.3布局

改进Seal系列产品布局优化,时序性能提升~3%。

增强Packing,减少资源占用率约1%,减少运行时间~30%。

增加了DRC检查,不仅检查物理约束,而且检查设计中的连接关系,帮助工程师方便快捷定位约束问题。

新增解析式布局算法,提高运行速度,较之前版本提升10%。

完整支持IO缺省状态及IO统计等功能,IO是器件与外部交互的唯一接口。以前IO的缺省状态交给硬件来控制,软件没有干预,导致客户应用中有风险,而且很难排查。完整支持后,每一种器件的IO都有确定的状态,既避免了应用中的风险,而且方便问题调试与排查。

6.4布线

提升seal系列产品布线的时序性能约5%,减少运行时间约30%。

内存使用比之前版本减少约25%。

更全面的进展,欢迎您试用最新发布版本,更欢迎您提出宝贵意见和建议。

-

FPGA

+关注

关注

1664文章

22504浏览量

639321 -

eda

+关注

关注

72文章

3145浏览量

183787 -

调试

+关注

关注

7文章

653浏览量

35883

原文标题:“芯”技术分享 | 2025年HqFpga软件中的进展说明

文章出处:【微信号:智多晶,微信公众号:智多晶】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

国产智多晶FPGA介绍及应用

国产FPGA智多晶叼

EDA Tools in FPGA

基于多种EDA工具的FPGA设计

光纤激光器市场前景广阔,有望在传感和医疗领域取得重大进展

eda工具软件有哪些 EDA工具有什么优势

泰凌微电子、谷歌与和众科技的Matter联合项目取得重大进展

智多晶FPGA设计工具HqFpga接入DeepSeek大模型

智多晶重磅发布HQPEP功耗评估工具

智多晶EDA工具HqFpga软件的主要重大进展

智多晶EDA工具HqFpga软件的主要重大进展

评论