美国海军使用字母名称对船体类型进行分类。例如,海军使用BB作为战舰的名称和驱逐舰的DD。在20世纪50年代早期 - 冷战开始后不久 - 海军为第一艘具有特殊雷达通信系统的驱逐舰雷达纠察舰提供装备。 DDR有额外的雷达天线并作为预警装置。

在存储设备领域,“DDR”这一名称对通信系统,时钟,个人电脑,智能手机,平板电脑和服务器。 DDR存储设备不再提供有关潜在敌方力量的早期预警,而是在电路板数据传输,功耗和依赖内存的技术方面不断改变我们对性能的看法。

DDR4值得特别关注

2014年,推出了第四代DDR内存(DDR4),降低了功耗,提高了数据传输速度和更高的芯片密度。 DDR4内存还具有改进的数据完整性,增加了对写入数据的循环冗余检查和片上奇偶校验检测。

在速度,性能和带宽方面有显着改进,DDR4内存值得特别关注。要了解DDR3和DDR4设备之间的区别,想象一下将当前的四门家用轿车换成独一无二的超级跑车。就像超级跑车以更高的速度运行并需要不同的空气动力学一样,DDR4提供了强大的信号完整性并且涉及高数据速率。

在查看设计时,我们可以将超级跑车类比更进一步。与家用轿车相比,超级跑车需要更先进的空气动力学和碳纤维复合材料,用于车身和部件。同样,围绕DDR4内存构建的PCB设计需要与标准PCB不同的布线方法。

如果没有专门的布线方法和对DDR4特定设计规则的关注,从发送器到接收器的信号质量会受到影响。从PCB布局的角度来看,如何处理DDR4专用设计?最好采用哪些规则来确保您的设备按照预期的数据运行?

DDR4设计规则

在使用时,时间可以是一切敏感信号和时钟技术。通过遵循DDR4路由和PCB设计的示例性指导原则,确保您的电路板能够有效地管理其数据。否则,您可能会遇到设计滞后,或遇到EMI和其他信号破坏性漏洞的重复问题。

您需要记住,数据速率范围从1.6Gbps到3.2Gbps,大 - 缩小扇出,更高的边沿速率需要特定的技术来维持信号完整性所需的最小误码率。例如,缺乏对设计规则的关注可能导致从一个信号到下一个信号的电容和电感耦合。随着这种耦合的增加,串扰变得越来越麻烦。

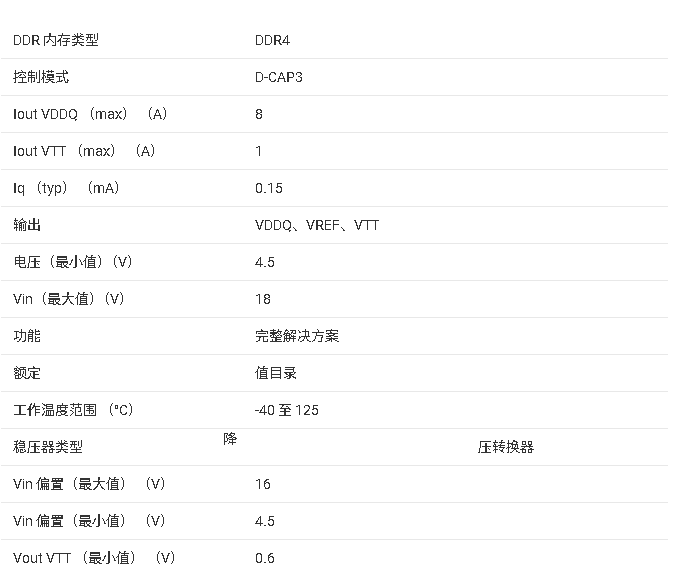

为了减少电容耦合的机会,您可以从设计中移除所有未使用的通孔焊盘。终端电压(VTT)与地之间的去耦电容将使电感耦合最小化。 VTT为存储器供电,与输入/输出电压(VIO)和核心电压(VCORE)分开。

< p> 基于时钟和时钟的接口在信号和数据传输技术中猖獗

不同DDR4拓扑的路由计划

DDR4 SDRAM采用翻盖拓扑或fly-by拓扑结构。两种拓扑都有优点和缺点。翻盖拓扑使用较少的电路板空间和两层,但需要复杂的布线方案。拥挤存储器设备下的顶层和底层之间的路由可能会导致路由拥塞和更长的存根走线。

相比之下,fly-by拓扑允许轻松路由并提供最佳信号完整性。然而,具有一层直插式存储器设备的飞越拓扑需要更多空间。最终,决定哪种选项最适合您的布局取决于您的设备需求。

在为PCB设计设置布线时,始终在同一层上布置相同的网络组。使用45°角而不是90°角,避免使用T型接头来处理关键的网络和时钟。不要将距离超过0.025英寸的存储器信号路由到PCI或系统时钟,并确保您的布线距离参考平面至少30密耳,并使边缘无效。此外,保持系统复位信号与其他信号之间的距离。

间距和长度问题

DDR4 SDRAM需要更短的路径和正确的间距以获得最佳效果时序和最佳信号完整性。始终避免将两个信号层彼此相邻布线,并将信号线布置在实心参考平面上。在构建路由规划时,请避免在空隙或参考平面分裂上路由信号线。

与存储器接口相关的任何信号都应在相应的GND或电源层之间路由。在同一层上的给定字节通道组内路由DQ,DQS和DM信号,以减少或消除层到层的传输速度差异。由于时钟信号必须具有比DQS信号更长的传播延迟,因此时钟信号跟踪的长度必须长于DIMM的最长DQS跟踪。差分时钟线具有更高的抗噪声能力以及对信号完整性的其他负面影响。

强大的路由软件将帮助您确保任何信号密集型设计都能顺利运行

要计划布局中轨迹之间的间距,您可以使用到特定轨迹的最近返回路径的垂直距离作为因子。实践涉及使用“H”来表示因子。将该长度乘以5,以找到两个时钟对或时钟对之间的最小间距。请记住,地址/命令/控制和DQ/DQS/DM走线在走线之间至少需要3H。

为简化问题,您可以轻松模拟AltiumDesigner®中的信号完整性,以进行设计捕获和电路板布局PCB设计过程的各个阶段。模拟器计算走线的特征阻抗,并将该信息与I/O缓冲器宏模型信息一起用作输入。

Altium还可以帮助您定义走线的走线宽度和厚度。路由宽度设计规则中的特征阻抗驱动宽度选项。对于具有易失性存储器,非易失性存储器,时序和时钟依赖性或差分对的电路板,PCB布局从未如此简单。使用PCB设计软件可以为您准确有效地完成工作。

-

pcb

+关注

关注

4418文章

23979浏览量

426277 -

封装

+关注

关注

128文章

9339浏览量

149057 -

PCB布线

+关注

关注

22文章

473浏览量

43654 -

华强pcb线路板打样

+关注

关注

5文章

14629浏览量

44725

发布评论请先 登录

DDR4价格疯涨!现货市场狂飙!

X3D续命,棘蛇再推高端新品,DDR4时代真的结束了吗?

IDT 4MX0121V:DDR3/DDR4 NVDIMM的理想开关/多路复用器

使用DDR4时钟架构

64GB 288 - Pin DDR4 RDIMM详细介绍

32GB (x72, ECC, DR) 288 - Pin DDR4 RDIMM:技术剖析与设计考量

深度解析:DDR4、DDR5 与 LPDDR6 内存的验证要点与挑战

利基型DRAM供需错配,DDR4 8Gb接受度高,加速转进DDR5/LPDDR5

N34C04 EEPROM:DDR4 DIMM的理想SPD解决方案

三星正式启动DDR4模组停产倒计时,PC厂商加速转向DDR5,供应链掀抢货潮

TPS65295 DDR4内存电源解决方案技术文档总结

DDR4设计规则及DDR4的PCB布线指南

DDR4设计规则及DDR4的PCB布线指南

评论