CSP封装是最新一代的内存芯片封装技术,其技术性能又有了新的提升。CSP封装可以让芯片面积与封装面积之比超过1:1.14,已经相当接近1:1的理想情况,绝对尺寸也仅有32平方毫米,约为普通的BGA的1/3,仅仅相当于TSOP内存芯片面积的1/6。与BGA封装相比,同等空间下CSP封装可以将存储容量提高三倍。

CSP封装内存不但体积小,同时也更薄,其金属基板到散热体的最有效散热路径仅有0.2毫米,大大提高了内存芯片在长时间运行后的可靠性,线路阻抗显著减小,芯片速度也随之得到大幅度提高。

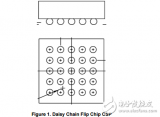

CSP封装内存芯片的中心引脚形式有效地缩短了信号的传导距离,其衰减随之减少,芯片的抗干扰、抗噪性能也能得到大幅提升,这也使得CSP的存取时间比BGA改善15%-20%。在CSP的封装方式中,内存颗粒是通过一个个锡球焊接在PCB板上,由于焊点和PCB板的接触面积较大,所以内存芯片在运行中所产生的热量可以很容易地传导到PCB板上并散发出去。CSP封装可以从背面散热,且热效率良好,CSP的热阻为35℃/W,而TSOP热阻40℃/W。

特点:

①体积小:在各种封装中,CSP是面积最小,厚度最小,因而是体积最小的封装。在输入/输出端数相同的情况下,它的面积不到0.5mm间距QFP的十分之一,是BGA(或PGA)的三分之一到十分之一。因此,在组装时它占用印制板的面积小,从而可提高印制板的组装密度,厚度薄,可用于薄形电子产品的组装;

②输入/输出端数可以很多:在相同尺寸的各类封装中,CSP的输入/输出端数可以做得更多。例如,对于40mm×40mm的封装,QFP的输入/输出端数最多为304个,BGA的可以做到600-700个,而CSP的很容易达到1000个。虽然目前的CSP还主要用于少输入/输出端数电路的封装。

③电性能好:CSP内部的芯片与封装外壳布线间的互连线的长度比QFP或BGA短得多,因而寄生参数小,信号传输延迟时间短,有利于改善电路的高频性能。

④热性能好:CSP很薄,芯片产生的热可以很短的通道传到外界。通过空气对流或安装散热器的办法可以对芯片进行有效的散热。

⑤CSP不仅体积小,而且重量轻:它的重量是相同引线数的QFP的五分之一以下,比BGA的少得更多。这对于航空、航天,以及对重量有严格要求的产品应是极为有利的

⑥CSP电路:跟其它封装的电路一样,是可以进行测试、老化筛选的,因而可以淘汰掉早期失效的电路,提高了电路的可靠性;另外,CSP也可以是气密封装的,因而可保持气密封装电路的优点。

⑦CSP产品:它的封装体输入/输出端(焊球、凸点或金属条)是在封装体的底部或表面,适用于表面安装。

-

芯片

+关注

关注

462文章

53534浏览量

459018 -

pcb

+关注

关注

4391文章

23742浏览量

420710 -

封装

+关注

关注

128文章

9139浏览量

147887

发布评论请先 登录

可以解决众多封装难题的CSP-ASIP

TVS新型封装CSP

什么是CSP封装

CSP封装量产测试中存在的问题

倒装芯片CSP封装

什么是CSP封装?CSP封装散热这个难题应该如何解决?

浅谈CSP封装芯片的测试方法

浅析先进封装之CSP和FCCSP

CSP封装芯片的测试方法

详解芯片尺寸封装(CSP)类型

CSP封装是什么?具有什么特点

CSP封装是什么?具有什么特点

评论