并行工程:指多功能型团队从最初形成阶段开始,所有的专业人员同力协作、同时开发产品及制造工艺的做法。

在传统串行工程的产品开发模式中,产品设计和工艺设计是两个相互独立、顺序执行的过程,这种模式容易造成产品设计过程与加工制造过程脱节,使产品的可制造性、可装配性和可维护性较差,从而导致设计改动难度大,产品开发周期长、成本高,而且质量难以保证,甚至有大量的设计无法投入生产,从而造成了人力和物力的巨大浪费。

并行工程理念的提出,向传统的产品开发模式提出了挑战,它打破了传统设计方法的顺序,将产品设计和工艺设计并行开发。

传统和高级的产品开发方法之间最明显的区别是早期是否聚齐了所有的专业人员以及是否能够随时开展工作。这个概念由麻省理工学院在一项耗资500万美元的标志性研究《改变世界的机器:精益生产的故事》(The Machine That Changed the Word: The Story of Lean Production)中提出,作者给出了以下结论:

在最好的日本精益项目中,项目初期参与人数最多,所有相关的专业人士都会参与其中,项目领导者的任务是鼓励整个小组权衡项目中会出现的所有困难,并且达成一致。

并行工程的理念是DFX的核心内容,也是我个人分享DFX知识的原则基础,它强调了周全的前期工作的重要性。

发布评论请先 登录

串行通讯与并行通讯介绍

一文看懂AI大模型的并行训练方式(DP、PP、TP、EP)

串行通信和并行通信的区别是什么

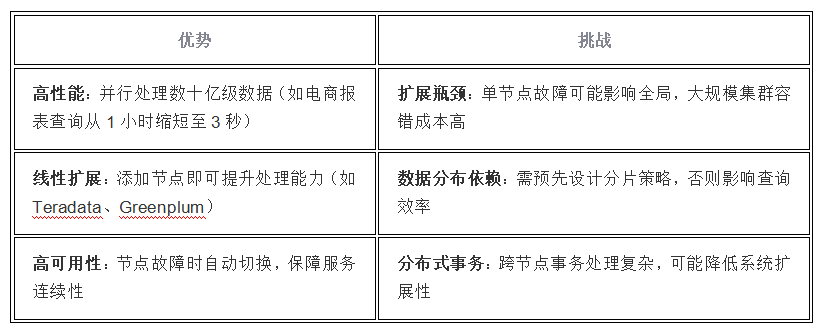

多节点并行处理架构

300 kHz 至 2.0 GHz 5 位数字衰减器,带串转并行驱动器 skyworksinc

0.01 – 4.0 GHz 7 位数字衰减器,带串行和并行驱动器 skyworksinc

读懂极易并行计算:定义、挑战与解决方案

用FPGA并行通信读取位置角度AD2S1210的最快角度更新速率是多少,是1/t16 HZ吗?

龙芯并行机器研制及应用项目推进会成功举办

如何使用FPGA驱动并行ADC和DAC芯片,使用不同编码方式的ADC与DAC时的注意事项

浅谈直流有刷电机驱动及调速技术

解析DeepSeek MoE并行计算优化策略

并行工程浅谈

并行工程浅谈

评论